Изобретение относится к области вычислительиой техиики и может быть исиользовано в аналоговых и цифро-аналоговых устройствах вычислительной техники н автоматики.

Известны блоки регулируемой задержки на конденсаторах н катодных иовторителях, осуществляющие заиоминание и носледовательную нередачу аналоговых напряжений. Однако этим схемам свойственна погрешность, возникающая ири передаче аналогового напряжения вдоль деиочки катодиых новторнтелей, низкое быстродействие схемы, обусловленное наличием механических ключей, разряд конденсаторов токами утечки ламп, невозможность создания траизисторных аналогов этих схем.

Предлагаемое устройство содержит транзисторы, включенные ио схеме с общей базой, нричем конденсаторы соединены с коллекторами предыдущих транзисторов н эмиттерами последующих. Для управления последовательной передачей заряда с конденсатора на конденсатор базовые цепи четных транзисторов соединены с одним нлечом триггера, а базовые цени нечетных транзисторов - с другим плечом триггера унравления последовательной передачей заряда. Для обеспечения съема нередаваемого аналогового напряжения относительно нулевого уровня нечетные коидеисаторы соединены с одним плечом

триггера, а четные - с другим плечом триггера обнуления. Для устраиения обратной передачи заряда служат диоды, включеиные в коллекторные цени транзисторов.

Такое выполнение устройства конструктивно проще, повышает надежность и точность, расширяет частотный диапазон.

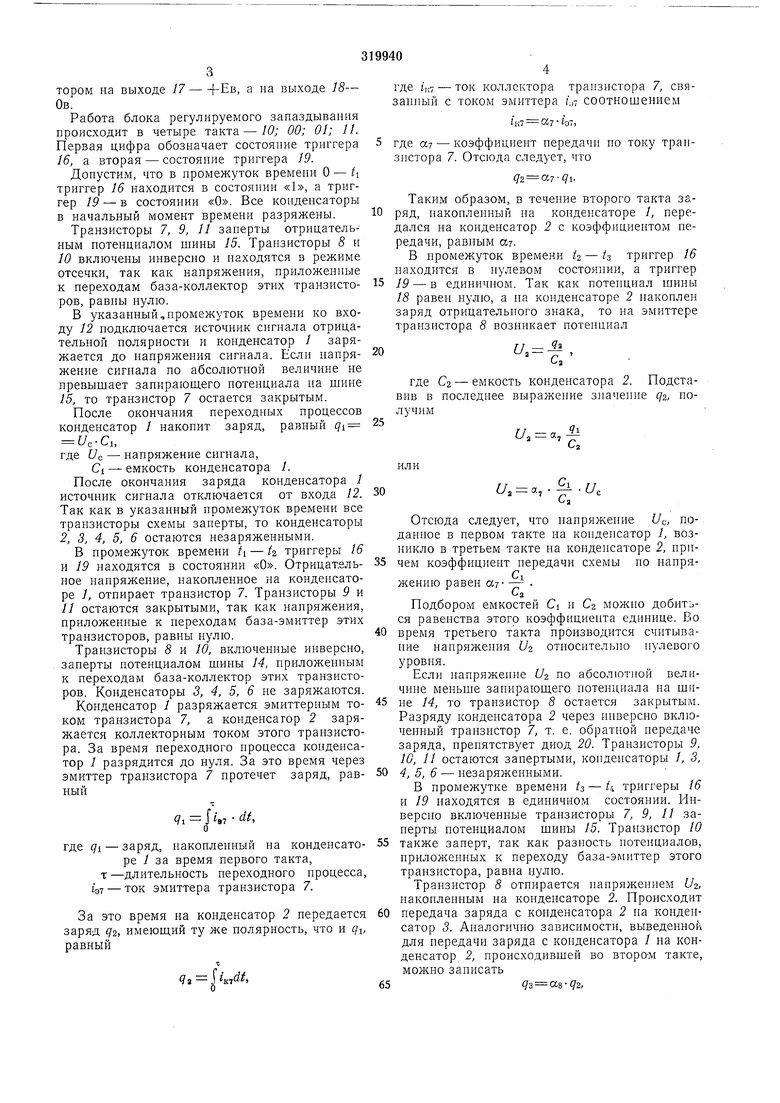

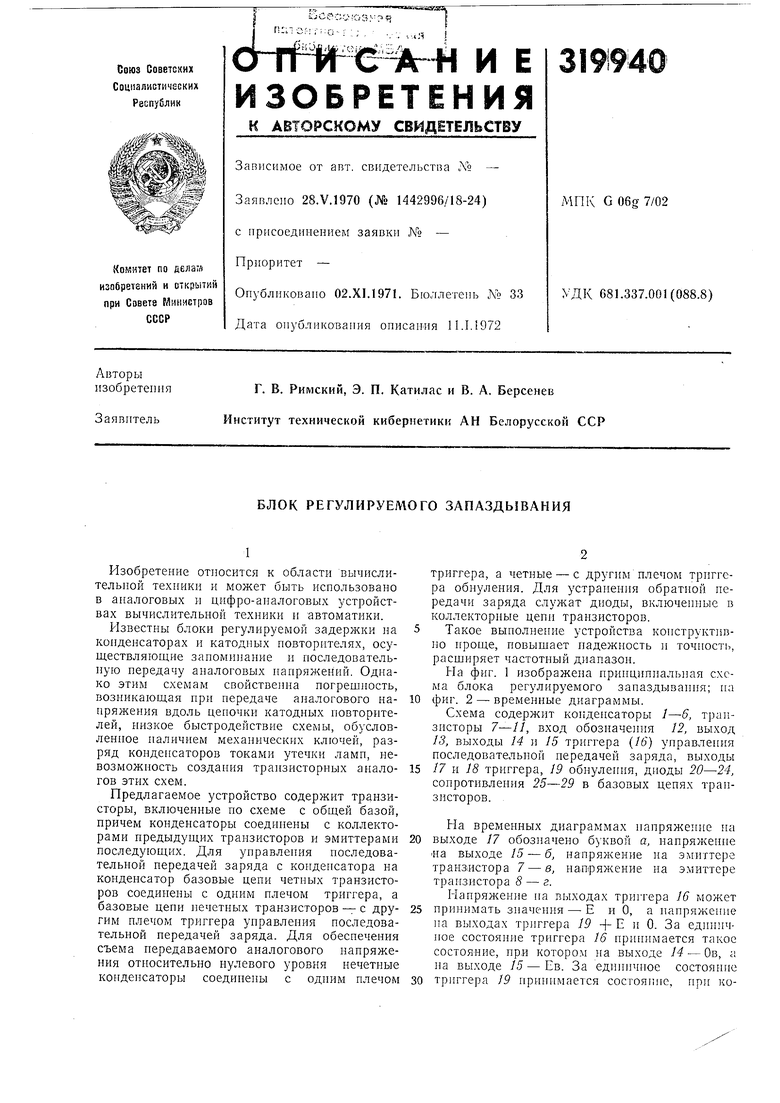

На фиг. 1 изображена нринципиальиая схема блока регулируемого заназдывання; на

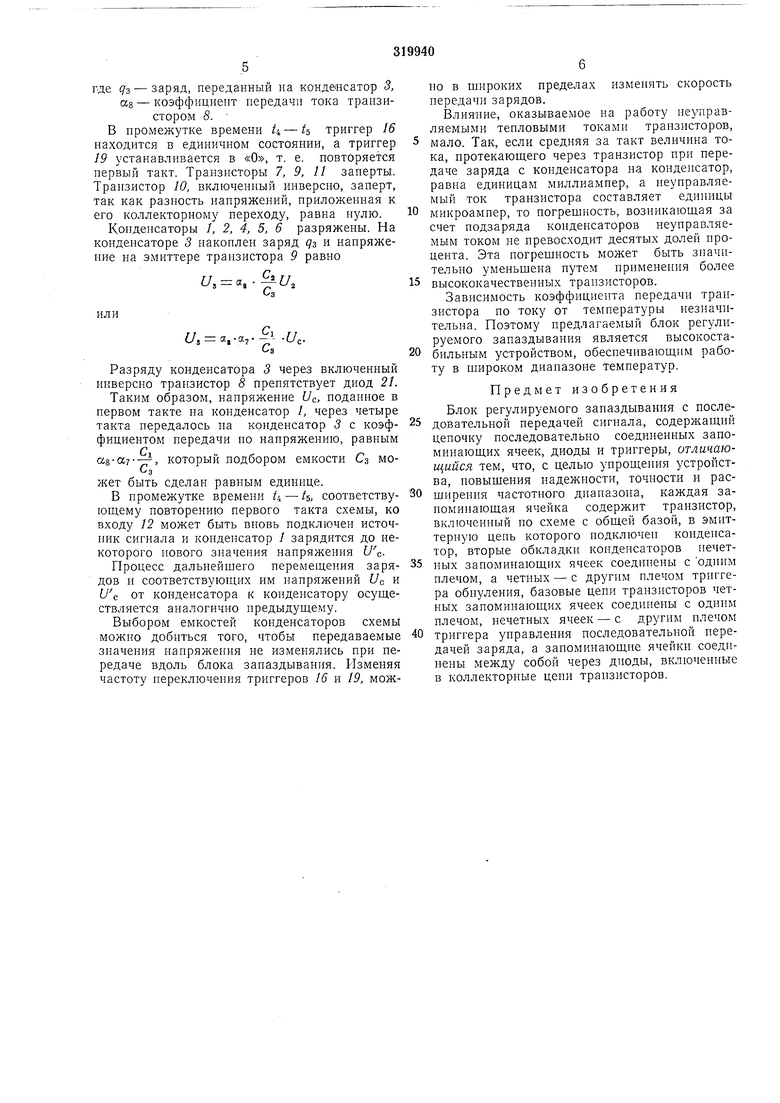

фиг. 2 - временные диаграммы.

Схема содержит конденсаторы /-5, транзисторы 7-11, вход обозиачения 12, выход 13, выходы 14 и 15 триггера (/6) унравления носледовательной передачей заряда, выходы

17 и 18 триггера, 19 обнуления, диоды 20-24, сопротивления 25-29 в базовых цепях транзисторов.

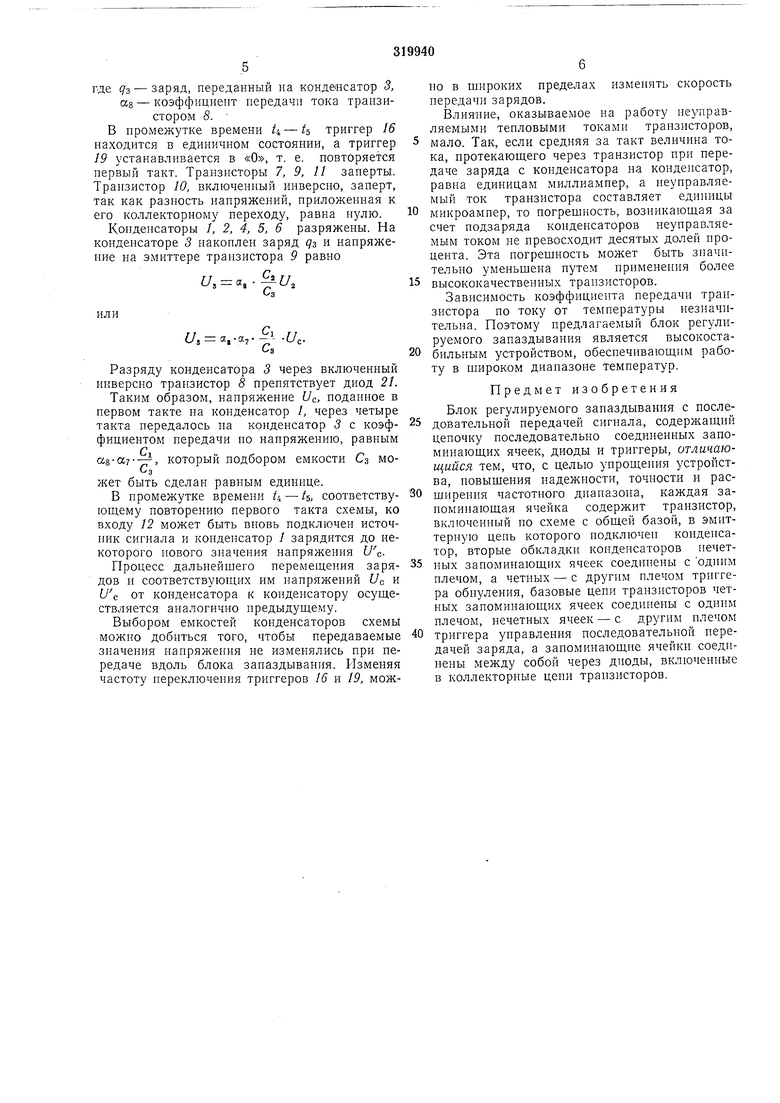

Па временных диаграммах нанряже ие на

выходе 17 обозначено буквой а, напряжение

на выходе 15 - б, напряжение на эмиттере

транзистора 7 - в, напряжение на эмиттере

транзистора 8 - г.

Напряжение на выходах триггера 16 может принимать значения - Е и О, а напряжение па выходах триггера /5 -(- Е и 0. За единичное состояние триггера 16 ирииимается такое состояние, ири котором на выходе 14 - Ов, а на выходе 15 - Ев. За единичное состояние триггера 19 ирииимается состояние, при котором на выходе 17рЕв, а на выходе 18-

ОБ.

Работа блока регулируемого заназдывання происходит в четыре такта - 10; 00; 01; П. Первая цифра обозначает состояние триггера 16, а вторая - состояние триггера 19.

Доиустим, что в иромежуток времени О - t триггер 16 находится в состоянии «1, а триггер 19 - в состоянии «О. Все конденсаторы в начальный момент времени разряжены.

Транзисторы 7, 9, 11 заиерты отрицательным нотенциалом шины 15. Транзисторы 8 н 10 включены инверсно и находятся в режиме отсечки, так как нанряжения, нриложенные к нереходам база-коллектор этих транзисторов, равны нулю.

В указанный,промежуток времени ко входу 12 подключается источник сигнала отрицательной полярности и конденсатор / заряжается до напряжения сигнала. Если напряжение сигнала но абсолютной величине не нревышает запирающего потенциала на шнне 15, то транзистор 7 остается закрытым.

После окончания переходных процессов конденсатор / накопит заряд, равный (/1 где t/c - напряжение сигнала,

Ci - емкость конденсатора 1.

После окончания заряда конденсатора 1 источник сигнала отключается от входа 12. Так как в указанный промежуток времени все транзисторы схемы заперты, то конденсаторы 2, 3, 4, 5, 6 остаются незаряженными.

В промежуток времени ti - /2 триггеры 16 и 9 находятся в состоянии «О. Отрицательное напряжение, накопленное на конденсаторе 1, отпирает транзистор 7. Транзисторы 9 н )/ остаются закрытыми, так как напряжения, приложенные к переходам база-эмиттер этих транзисторов, равны нулю.

Транзисторы 5 и 10, включенные инверсно, занерты потенциалом шины 14, приложенным к переходам база-коллектор этих транзисторов. Конденсаторы 3, 4, 5, 6 не заряжаются.

Конденсатор 1 разряжается эмнттерным током транзистора 7, а конденсатор 2 заряжается коллекторным током этого транзистора. За время переходного процесса конденсатор 1 разрядится до нуля. За это время через эмиттер транзистора 7 нротечет заряд, равный

-1/,,

dt.

7i

где 9i - заряд, накопленный на конденсаторе / за время первого такта, т-длительность переходного процесса, гэт - ток эмиттера транзистора 7.

За это время на конденсатор 2 передается заряд 2, имеющий ту полярность, что н q, равный

где i-ifi - ток коллектора транзистора 7, связанный с током эмиттера f;,7 соотношением

1к7 СХ747,

где ол - коэффициент нередачи по току транзистора 7. Отсюда следует, что

qz aTqi.

Таким образом, в течение второго такта заряд, накопленный на конденсаторе /, нередался на конденсатор 2 с коэффициентом нередачи, равным ат.

В промежуток времени 4 - з триггер 16 находится в нулевом состоянии, а триггер 19 - в единичном. Так как потенциал шины 18 равен нулю, а на конденсаторе 2 наконлен заряд отрицательного знака, то на эмиттере транзнстора 8 возникает потенциал

а

и,

где Cz - емкость конденсатора 2. Подставив в последнее выражение значение q, получим

-«,

или

, а, ..f/e

Сц

Отсюда следует, что напряжение t/c, поданное в первом такте на копдепсатор /, возникло в третьем такте на конденсаторе 2, нрнчем коэффициент передачи схемы по напряжению равен - .

Са

Подбором емкостей Ci и Cz можно добиться равенства этого коэффициента единице. Во

время третьего такта производится считывание напряжения Uz относительно пулевого уровня.

Если напряжение Uz по абсолютной величине меньше заннрающего нотенциала на шяпе 14, то транзистор 8 остается закрытым. Разряду конденсатора 2 через инверсно включенный транзистор 7, т. е. обратной нередаче заряда, препятствует диод 20. Транзисторы 9, 10, 11 остаются запертыми, конденсаторы 1, 3,

4, 5, 6 - незаряженными.

В промежутке времени tz - /4 триггеры 16 и 19 находятся в единичном состоянии. Инверсно включенные транзисторы 7, 9, 11 заперты потенциалом шины 15. Транзистор 10

также заперт, так как разность нотенциалов, приложенных к переходу база-эмиттер этого транзистора, равна нулю.

Транзистор 8 отпирается напряжением 11-, наконленным на конденсаторе 2. Происходит

передача заряда с конденсатора 2 на конденсатор 3. Аналогично зависимости, выведенной для нередачн заряда с конденсатора / на конденсатор 2, происходившей во втором такте, можно занисать где (7з - заряд, переданный на конденсатор 3, as - коэффициент передачи тока транзистором 8. В промежутке времени 4 - 4 триггер 16 находится в единичном состоянии, а триггер 19 устанавливается в «О, т. е. повторяется первый такт. Транзисторы 7, 9, 11 заперты. Транзистор 10, включенный инверсно, заперт, так как разность напряжений, приложенная к его коллекторному переходу, равна нулю. Конденсаторы /, 2, 4, 5, 6 разряжены. На конденсаторе 3 накоплен заряд q и напряжение на эмиттере транзистора 9 равно и, а,.и, f/, a..a,..e. Оз Разряду конденсатора 3 через включенный инверсно транзистор 8 препятствует диод 21. Таким образом, напряжение f/c, поданное в первом такте па конденсатор /, через четыре такта передалось на конденсатор 3 с коэф-25 фнциентом передачи по напряжению, равным а,.аг, который подбором емкости Сз моСзжет быть сделан равным единнце. В промежутке времени 4 - U, соответству-30 ющему повторению первого такта схемы, ко входу 12 может быть вновь подключен источпик сигнала и конденсатор / зарядится до некоторого нового значения напряжения f/cПроцесс дальнейшего перемещения заря-35 дон и соответствующих пм напряжений Uc и Uc от конденсатора к конденсатору осуществляется аналогично предыдущему. Выбором емкостей конденсаторов схемы можно добиться того, чтобы передаваемые40 значения напряжения не изменялись при передаче вдоль блока запаздывания. Изменяя частоту переключения триггеров 16 н 19, мож510 15 20 ПО в широких пределах изменять скорость передачи зарядов. Влияние, оказываемое на работу неуправляемыми тепловыми токами трапзисторов, мало. Так, если средняя за такт величина тока, протекающего через транзистор при передаче заряда с конденсатора на конденсатор, равна единицам миллиампер, а неуправляемый ток трапзистора составляет единицы микроампер, то погрешность, возникающая за счет подзаряда конденсаторов неуправляемым током не превосходит десятых долей процента. Эта погрешность может быть значительно уменьшена путем применения более высококачественных транзисторов. Зависимость коэффициента передачи транзистора по току от температуры незначнтельпа. Поэтому предлагаемый блок регулируемого запаздывания является высокостабильным устройством, обеспечивающим работу в широком диапазопе температур. Предмет изобретения Блок регулируемого запаздывания с последовательной передачей сигнала, содержащий цепочку последовательно соединенных запоминающих ячеек, диоды и триггеры, отличающийся тем, что, с целью упрощеиия устронства, новышения надежности, точности и расширення частотного диапазона, каждая запоминающая ячейка содержит транзистор, включенный по схеме с общей базой, в эмнттерную цепь которого подключен конденсатор, вторые обкладки конденсаторов нечетных запоминающих ячеек соединены с одним плечом, а четных - с другим плечом триггера обнуления, базовые цепи транзисторов четпых запоминающих ячеек соединены с одннм плечом, нечетных ячеек - с другим плечом триггера управления последовательной передачей заряда, а запоминающие ячейки соедипены между собой через диоды, включенные в коллекторные цени трапзисторов.

ра2 1

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛУПРОВОДНИКОВЫЙ ключ | 1970 |

|

SU259959A1 |

| Электроимпульсатор | 1976 |

|

SU747475A1 |

| Автономная система энергоснабжения | 1989 |

|

SU1644357A1 |

| ЖДУЩИЙ МУЛЬТИВИБРАТОР НА ТРАНЗИСТОРАХ | 1967 |

|

SU196091A1 |

| Распределитель на транзисторах | 1973 |

|

SU504302A1 |

| Устройство для формирования серий импульсов с регулируемыми длительностями импульсов и интервалами между ними | 1976 |

|

SU991584A1 |

| УСТРОЙСТВО ЦИКЛИЧЕСКОЙ, СИНХРОННОЙ, с ВРЕМЕННЫМ | 1970 |

|

SU277009A1 |

| Устройство для управления транзисторным инвертором | 1988 |

|

SU1646032A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| Двухтактный релаксатор | 1978 |

|

SU765987A1 |

Даты

1971-01-01—Публикация