Изобретение относится к области вычислительной техники и предназначено для преобразования кодов.

Известен преобразователь кода из системы остаточных классов во взвешенную систему счисления со смешанным набором оснований, который содержит входной и выходной регистры, пирамиду матриц, устройство сравнения, включенное между входом и выходом выходного регистра, и логические схемы, включенные между входным регистром и пирамидой матриц и между пирамидой матриц и выходным регистром; для выявления случайных и систематических сбоев осуществляют двойной просчет по прямому и дополнительному кодам числа и затем сравнивают результаты, предварительно преобразовав дополнительный код в пря1мой.

Предлагаемое устройство отличается от известных тем, что содержит анализатор величины модульной суммы, а сумматоры в пирамиде объединены в группы по каждому модулю и параллельно-последовательно соединены между собой, причем входы пирамиды сумматоров соединены с соответствующими выходами устройства для хранения констант по каждому модулю, входы которого соединены с выходами входного регистра, а каждый из формирователей переносов соединен по входам с сумматорами данной группы, а по выходу - с последним сумматором последующей группы, причем выход предпоследнего сумматора группы сумматоров по последнему модулю соединен со входом анализатора величины модульной суммы, выходы которого соединены через элементы «И со входом элемента «ИЛИ.

Это позволяет повысить быстродействие преобразования и вычисления ранга числа.

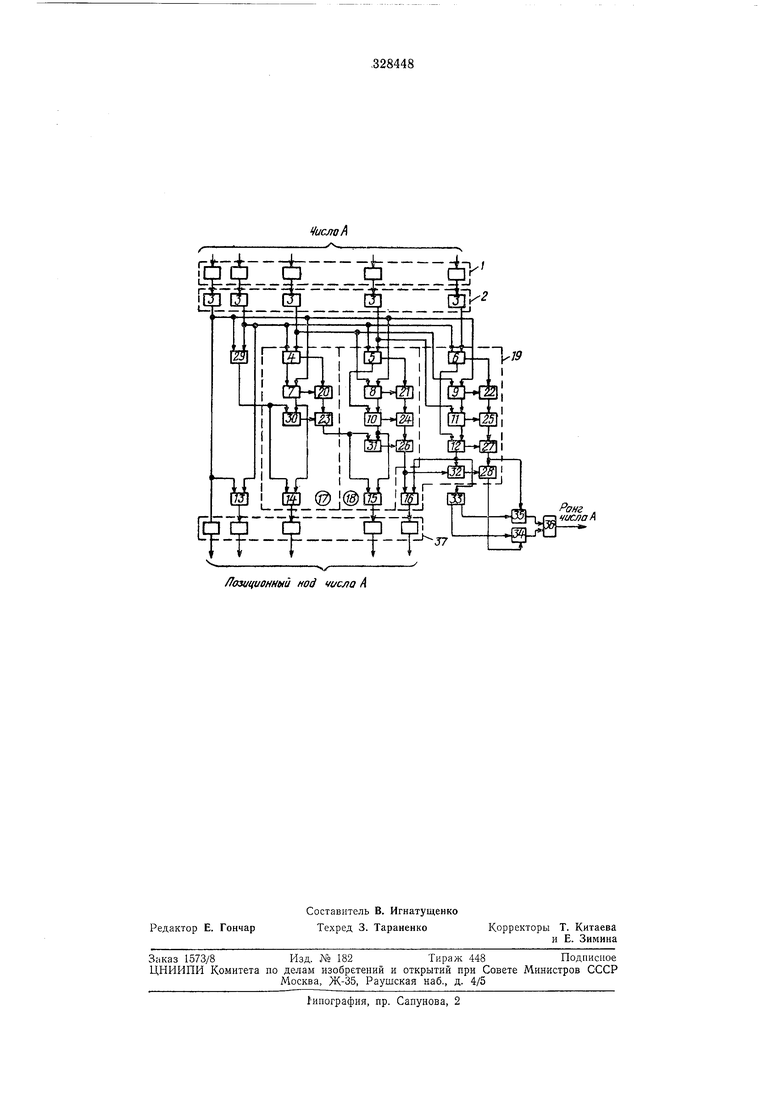

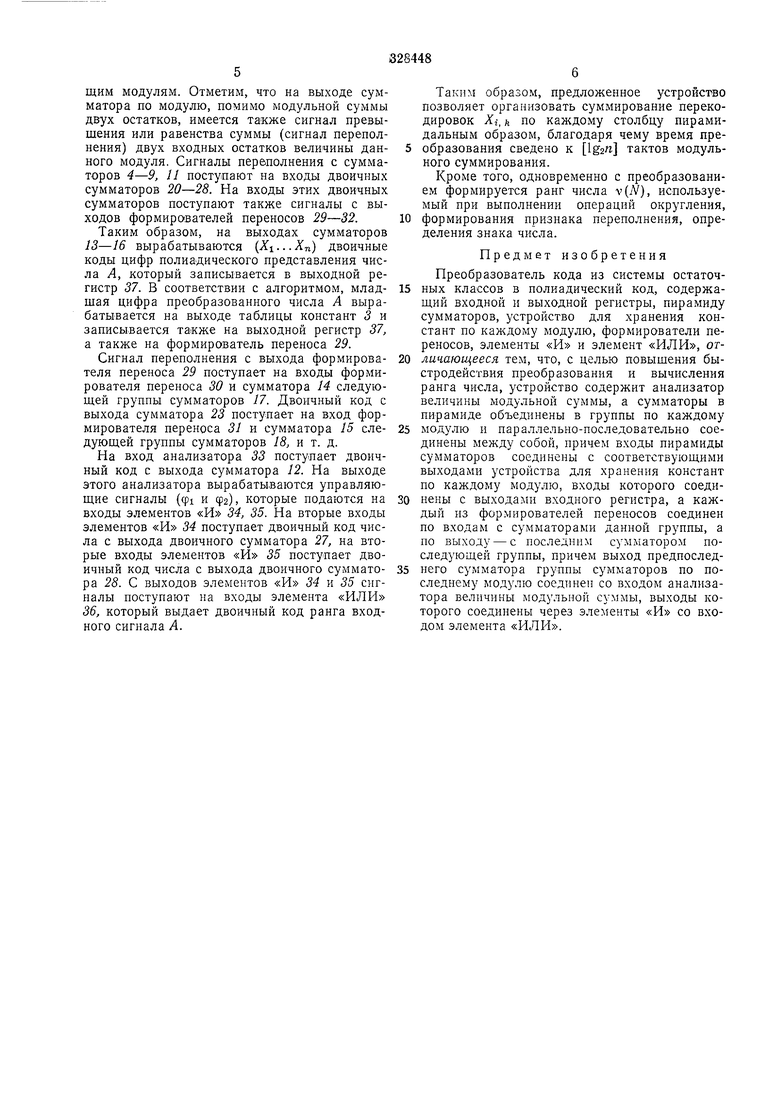

На чертел е изображена схема устройства.

Устройство содерл ит входной регистр / для запоминания остатков числа Л по соответствующим модулям; устройство 2 для хранения констант по каждому модулю, состоящее из долговременных запоминающих устройств 3 для каждого модуля; пирамиду из сумматоров 4-16, объединенных в группы 17, 18 и 19 по каждому модулю и предназначенных для

суммирования каждых двух входных остатков, представленных в двоичном коде, по соответствующему основанию; двоичные сумматоры 20-28 для суммирования двух входных чисел, представленных в двоичном коде, по основанию 2; формирователи переносов 29-32; анализатор величины модульной суммы 33, элементы «И 34 и 35, элемент «ИЛИ 36, выходной регистр 37. Устройство использует следующий алгоритм стемы счисления в полиадический код. При этом условимся обозначать: рг - основания системы счисления;P pi-pz...pn-величина, определяющая диапазон чисел, представляемых остатками; - базисные числа непозиционного представления; 1X1 Oi -неотрицательный остаток от деления целого числа X на Pi. Представление целого числа Л из диапазол на О, Д ввидеЛ аг.Я,)-Я (1) называется непозиционным. Здесь a,i N-Pi- pi, число определяется условием ll lPrl -Vift l. v(A)-ранг числа N. Представление целого числа Л из диапазона О, Д в виде ...-р -}-f ...-fXn.Pi.Pa.-.Pn-b

называется полиадическим.

Задача формулируется следующим образом: пусть число , Р представлено остатками

A--(ai,a.s,...,«„), a., ,

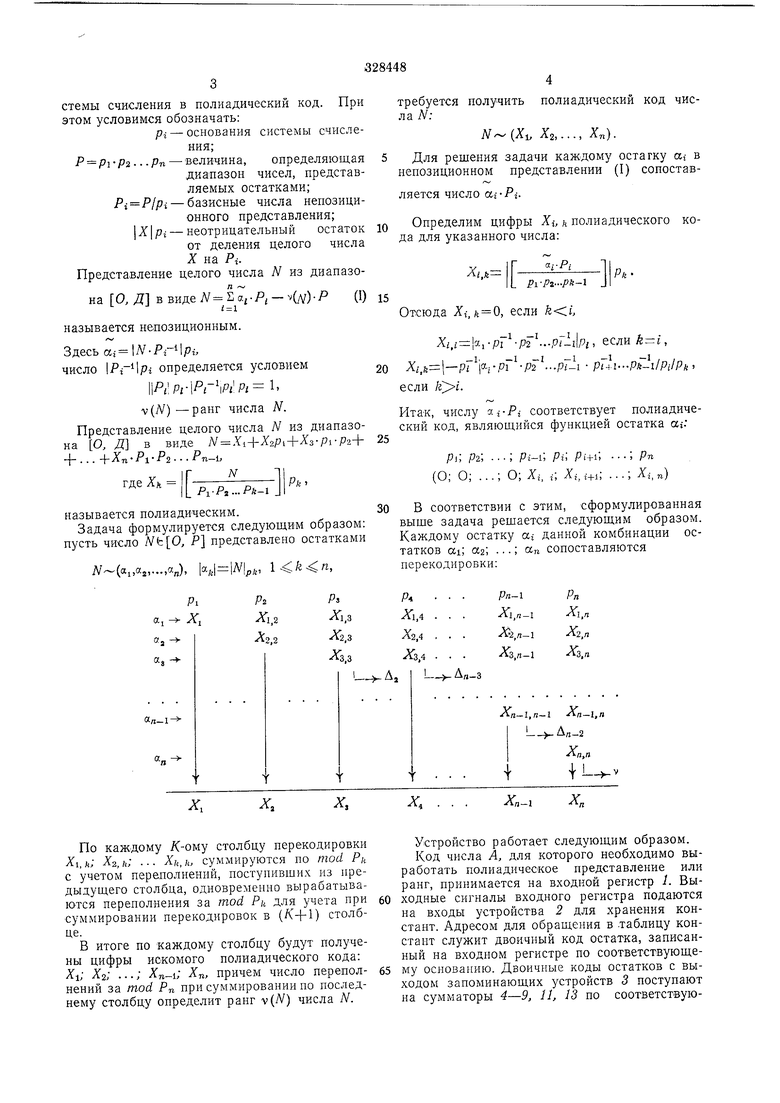

В соответствии с этим, сформулированная выще задача рещается следующим образом. Каждому остатку a-i данной комбинации остатков cci; «2; ...; an сопоставляются

перекодировки: требуется получить полиадический код числа N: N(X,, Хг,..., Хп). Для решения задачи каждому остатку a.i в непозиционном представлении (I) сопоставляется число аг-Рг,,, Определим цифры А, полиадического коДа для указанного числа: Xi k IГ IIР IL Pi-pz-.pa-i Л Отсюда Xi fe 0, если , Хг.г - -/ p2..-pi-i Pi, если , X.i k- -pi y-rPi -p2 --.pi-i pTli--Pk-ilPilPk если . Ита«, числу y.i-Pi соответствует полиадический код, являющийся функцией остатка ас. Pi, рг, ., pi-i, Рг, Pi+i, ..., рп (О; О; ...; О; Xi, ,; Xi,i+,; ...; Xi,n

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода из системы остаточных классов в позиционный код | 1978 |

|

SU744549A1 |

| ВСЕСОЮЗНАЯ iтЙЁ tft . ^>&^" - i-=---- | 1973 |

|

SU365701A1 |

| УСТРОЙСТВО для ФОРМИРОВАНИЯ позиционных | 1973 |

|

SU377766A1 |

| Устройство для формирования позиционных признаков непозиционного кода | 1980 |

|

SU968800A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1266009A1 |

| УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ | 1973 |

|

SU398950A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПОЗИЦИОННЫХ ХАРАКТЕРИСТИК НЕПОЗИЦИОННОГО КОДА | 1991 |

|

RU2020756C1 |

| НЕЙРОННАЯ СЕТЬ ДЛЯ ПРЕОБРАЗОВАНИЯ ОСТАТОЧНОГО КОДА В ДВОИЧНЫЙ ПОЗИЦИОННЫЙ КОД | 2006 |

|

RU2318238C1 |

| Устройство для сложения чисел в системе остаточных классов | 1980 |

|

SU930317A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

X,

X,

X.

По каждому /(-ому столбцу перекодировки 1,А; Xz,h; ... Xk,h, суммируются по mod Pk с учетом переполнений, поступивших из предыдущего столбца, одновременно вырабатываются переполнения за mod Pk для учета при суммировании перекодировок в (К+1) столбце.

В итоге по каждому столбцу будут получены цифры искомого полиадического кода: Xi; ...; Xn-i; Хп, причем число переполнений за mod Рп при суммировании по последнему столбцу определит ранг v(A) числа N.

X, . .

Хп-1

х„

Устройство работает следующим образом. Код числа А, для которого необходимо выработать полиадическое представление или ранг, принимается на входной регистр 1. Выходные сигналы входного регистра подаются на входы устройства 2 для хранения констант. Адресом для обращения в таблицу констант служит двоичный код остатка, записанный на входном регистре по соответствующещим модулям. Отметим, что на выходе сумматора по модулю, помимо модульной суммы двух остатков, имеется также сигнал превышения или равенства суммы (сигнал переполнения) двух входных остатков величины данного модуля. Сигналы переполнения с сумматоров 4-9, 11 поступают на входы двоичных сумматоров 20-28. На входы этих двоичных сумматоров поступают также сигналы с выходов формирователей переносов 29-32.

Таким образом, на выходах сумматоров 13-16 вырабатываются (Xi...Xn) двоичные коды цифр полиадического представления числа Л, который записывается в выходной регистр 37. В соответствии с алгоритмом, младшая цифра преобразованного числа А вырабатывается на выходе таблицы констант 3 и записывается также на выходной регистр 37, а также на формирователь переноса 29.

Сигнал переполнения с выхода формирователя переноса 29 поступает на входы формирователя переноса 30 и сумматора 14 следуюшей группы сумматоров 17. Двоичный код с выхода сумматора 23 поступает на вход формирователя переноса 31 п сумматора 15 следующей группы сумматоров 18, и т. д.

На вход анализатора 33 поступает двоичный код с выхода сумматора 12. На выходе этого анализатора вырабатываются управляющие сигналы (ф1 и ф2), которые подаются на входы элементов «И 34, 35. На вторые входы элементов «И 34 поступает двоичный код числа с выхода двоичного сумматора 27, на вторые входы элементов «И 35 поступает двоичный код числа с выхода двоичного сумматора 28. С выходов элементов «И 34 и 35 сигналы поступают на входы элемента «ИЛИ 36, который выдает двоичный код ранга входного сигнала А.

Таким образом, предложенное устройство позволяет организовать суммирование перекодировок Хг, h по каждому столбцу пирамидальным образом, благодаря чему время преобразования сведено к Ig2« тактов модульного суммирования.

Кроме того, одновременно с преобразованием формируется ранг числа v(N), используемый при выполнении операций округления, 0 формирования признака переполнения, определения знака числа.

Предмет изобретения

Преобразователь кода из системы остаточных классов в полиадический код, содержащий входной и выходной регистры, пирамиду сумматоров, устройство для хранения констант по каждому модулю, формирователи переносов, элементы «И и элемент «ИЛИ, отличающееся тем, что, с целью повышения быстродействия преобразования и вычисления ранга числа, устройство содержит анализатор величины модульной суммы, а сумматоры в пирамиде объединены в группы по каждому

5 модулю п параллельно-последовательно соединены между собой, причем входы пирамиды сумматоров соединены с соответствующими выходами устройства для хранения констант по каждому модулю, входы которого соединены с выходами входного регистра, а каждый из формирователей переносов соединен по входам с сумматорами данной группы, а по выходу - с последним сумматором последующей группы, причем выход предпоследнего сумматора группы сумматоров по последнему модулю соединен со входом анализатора величины модульной суммы, выходы которого соединены через элементы «И со входом элемента «ИЛИ.

Лоза1(ионный над тела А

Ранг . числа/

Даты

1972-01-01—Публикация