N:)

Од

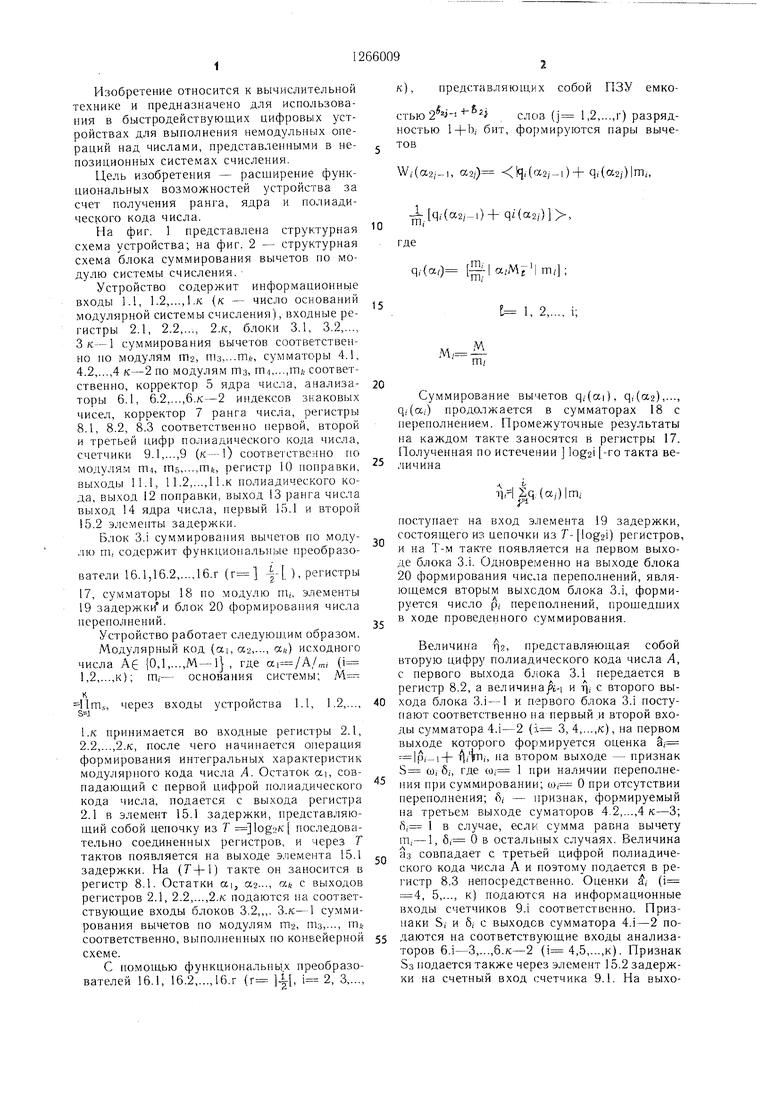

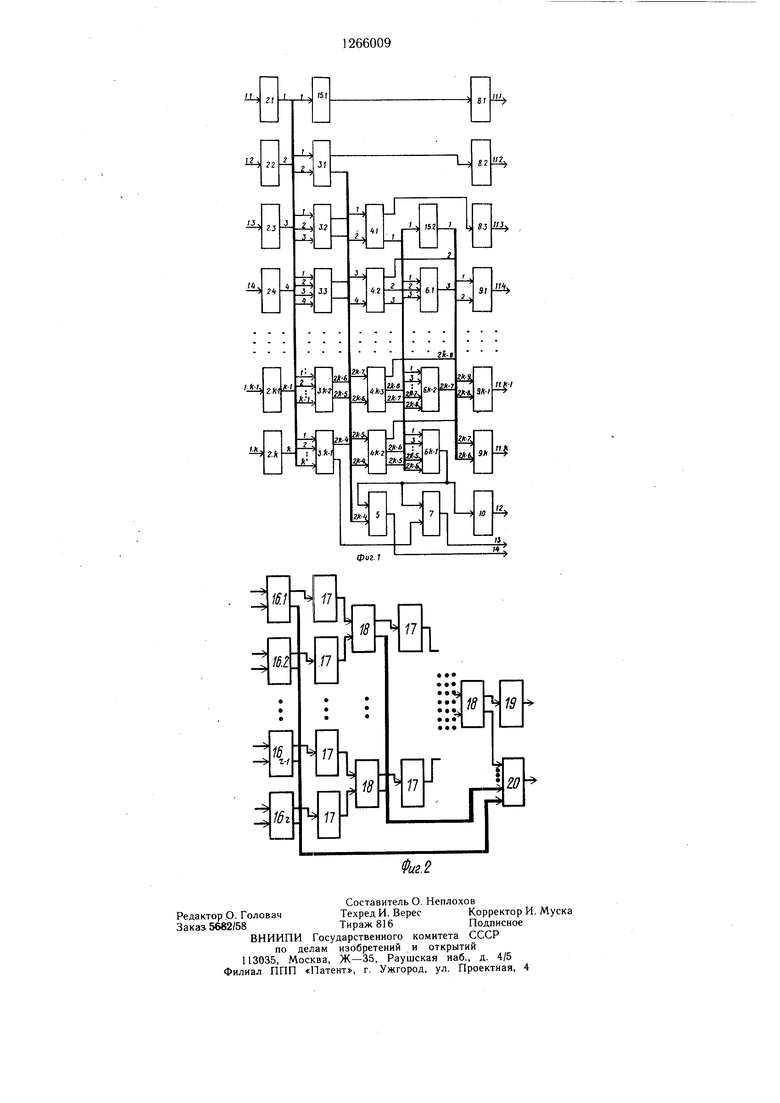

О5 Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых устройствах для выполнения немодульиых операций над числами, представленцыми в непозиционных системах счисления. Цель изобретения - расширение функциональных возможностей устройства за счет получения ранга, ядра и полиадического кода числа. На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока суммирования вычетов по модулю системы счисления. Устройство содержит информационные входы 1.1, 1.2,...,1.к (к - число оснований модулярной системы счисления), входные регистры 2.1, 2.2,..., 2.К, блоки 3.1, 3.2,..., Зк-1 суммирования вычетов соответственно но модулям mz, тз,...т/г, сумматоры 4.1, 4.2,...,4 к-2 по модулям 1Пз, rn.i,...,mi, соответственно, корректор 5 ядра числа, анализаторы 6.1, 6.2,...,6.к-2 индексов знаковых чисел, корректор 7 ранга числа, регистры 8.1, 8.2, 8.3 соответственно первой, второй и третьей цифр полиадического кода числа, счетчики 9.1,...,9 (к-1) соответственно по модулям m-i, 17)5,...,т/г, регистр И) поправки, выходы 11.1, 11.2,..., 1 .к полиадического кода, выход 12 поправки, выход 13 ранга числа выход 14 ядра числа, первый 15.1 и второй 15.2 элементы задержки. Блок 3.i суммирования вычетов по модулю т, содержит функциональные преобразователи 16.1,16.2,...,16.г ( -|- ), регистры 17, сумматоры 18 по модулю ш,, элементы 19 задержкии блок 20 формирования числа переполнений. Устройство работает следующим образом. Модулярный код {ai, «2,..., otfc) исходного числа AG {0,1,...,М-1} , где ,„, (i 1,2,...,к); т/- основания системы; М к И1гп5, через входы устройства 1.1, 1.2,..., 1.К принимается во входные регистры 2.1, 2.2,...,2.к, после чего начинается операция формирования интегральных характеристик модулярного кода числа А. Остаток а, совпадающий е первой цифрой полиадического кода числа, подается с выхода регистра 2.1 в элемент 15.1 задержки, представляющий собой цепочку из Г log2K последовательно соединенных регистров, и через Т тактов появляется на выходе элемента 15.1 задержки. На (Г-(-1) такте он заносится в регистр 8.1. Остатки ai, 0.2..., « с выходов регистров 2.1, 2.2,...,2.к подаются па соответствующие входы блоков 3.2,,,. З./с-1 суммирования вычетов по модулям т, шз,..., т. соответственно, выполненных по конЕ1ейерной схеме. С помощью функциональных преобразователей 16.1, 16.2,...,16.г (г , 1 2, 3,..., к), представляющих собой ПЗУ емкостью , слов (j 1,2,...,г) разрядностью 1+Ь, бит, формируются пары вычетовW,-(, a.2i)- q,(a2,-i)+q,{a2j)|rrii. 4г q(a2,-i)4- qt(a2/), 111, q,-(aO - a/M7 m, ; t 1, 2,..., i; M Суммирование вычетов q;(ai), q,(a2),..., q,(a,) продолжается в сумматорах 18 с переполнением. Промежуточные результаты на каждом такте заносятся в регистры 17. Полученная по истечении Iog2i -го такта величина11Г 2q,(a,) f поступает на вход элемента 19 задержки, состоящего из цепочки из Г- Iog2i) регистров, и на Т-м такте появляется на первом выходе блока 3.1. Одновре.менно на выходе блока 20 формирования числа переполнений, являющемся вторым выходом блока 3.1, формируется число fi,- переполнений, фощедших в ходе проведенного суммирования. Величина fjs, представляющая собой вторую цифру полиадического кода числа Л, с первого выхода 3.1 передается в регистр 8.2, а величин а Д-1 и т|; с второго выхода блока 3.1-1 и первого блока 3.1 поступают соответственно на первый и второй входы сумматора 4.1-2 3, 4,...,к), на первом выходе которого формируется оценка а; lpi-i+ i /bii, на втором выходе - признак S со, б;, где Ш;- 1 при наличии переполнения при суммировании; oj, О при отсутствии переполнения; б, - признак, формируемый на третьем выходе суматоров 4.2,...,4 к-3; б, 1 в случае, если сумма равна вычету in,- 1, б, О в остальных случаях. Величина аз совпадает с третьей цифрой полиадического кода числа А и поэтому подается в регистр 8.3 непосредственно. Оценки , (1 4, 5,..., к) подаются на информационные входы счетчиков 9.1 соответственно. Признаки S, и 6, с выходов сумматора 4л-2 подаются на соответствующие входы анализаторов 6.1-3,...,6. {i 4,5,...,к). Признак 5з подается также через элемент 15.2 задержки на счетный вход счетчика 9.1. На выходе анаизатора 6.i-2 формируется поправка i-ro порядка в,- SiV 6iS,i V...V6,--6,b...,64S3, которая поступает на счетный вход счетчика 9.i+l (i 4,5,6,...,к-1). Поправка в с выхода анализатора 6.к- передается в регистр 10 поправки, а также подается на первые входы корректоров 5 и 7 ядра и ранга числа, на вторые входы которых поступают соответственно величины T)fe и k- В результате коррекции в счетчиках 9; получают i-ые цифры полиадического кода а,- |a,-|-€)i-i Im/. В корректоре 5 определяется ядро числа т| ),, в корректоре 7 - ранг р pA-f ©А числа А. Полученные интегральные характеристики исходного модулярного кода ai, а,..., а, , р-и Т снимаются с выходов 11.1, 11.2,..., 1,, 12, 13 и 14 соответственно. Благодаря конвейерной структуре предлагаемого устройства формирование интегральных характеристик каждого последующего числа может быть начато после одного такта выполнения операций по формированию интегральных характеристик предыдущего числа. Формула изобретения Устройство для формирования интегральных характеристик модулярного кода, содержащее к входных регистров (к - число модулей системы), входы которых являются входами устройства, (к.-2) блоков суммирования вычетов по модулям mz, rn3,...,, соответственно, анализатор индексов знаковых чисел и регистр поправки, выход которого является выходом поправки устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет получения ранга, ядра и полиадического кода числа, в него введены первый и второй элементы задержки, дополнительный блок суммирования вычетов по модулю т, (к-2) сумматоров по модулям шз,..-, nifc соответственно, корректор ядра, (к-4) дополнительных анализаторов индексов знаковых чисел, корректор ранга, регистры трех младших цифр полиадического кода и (к-3) счетчиков по модулям т4, ГП5,..., т/г, выходы которых являются выходами полиадического кода устройства, выход корректора ядра является выходом ядра устройства, а-выход корректора ранга числа - выходом ранга устройства, выход первого входного регистра через первый элемент задержки соединен с входом регистра первой младшей цифры полиадического кода, j-й вход блока суммирования вычетов по модулю т;, подключен к выходу j-ro входного регистра (где i 2,3,..., К; j 1, 2,..., i), первый выход блока суммирования вычетов по модулю т2 подключен к входу регистра второй младшей цифры полиадического кода, первый иi второй входы i-ro сумматора по модулю гп,+2 (i 1,2,..., К-2) подключены к второму и первому выходам блоков суммирования вычетов по модулям m,+i и т,+2 соответственно, первый и второй выходы блока суммирования вычетов по модулю mfc подключены к вторым входам корректоров ядра и ранга числа соответственно, первые входы которых и вход регистра поправки объединены и подключены к выходу (К-3)-го анализатора индексов знаковых чисел, первый выход первого сумматора по модулю Шз подключен к входу регистра третьей младшей цифры полиадического кода, а его второй выход через второй элемент задержки подключен к счетному входу первого счетчика по модулю 014, первый вход i-ro сумматора по модулю т,.2 (i 2, 3,...,К-2) подключен к информационному входу счетчика по модулю т;+2, счетный вход счетчика по модулю т,--(2 (i 3, 4,..., К-2) подключен к выходу (i-2)-го анализатора индексов знаковых чисел соответственно, (2j - 1)-й и входы i-ro анализатора индексов знаковых чисел подключены соответственно к второму выходу j-ro и третьему выходу (Е+1)-го сумматоров для всех j 1, 2,..., i+1, t 1,2,..., i, i 1, 2,..., к-3.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования интегральных характеристик модулярного кода | 1986 |

|

SU1464293A1 |

| Устройство для формирования интегральных характеристик модулярного кода | 1984 |

|

SU1216777A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1989 |

|

SU1672448A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих цифровых устройствах для выполнения немодульных операций над числами, представленными в непозиционных системах счисления. Целью изобретения является расширение функциональных возможностей устройства за счет получения ранга, ядра и полиадического кода числа. Для этого устройство содержит информационные входы, входные регистры, блоки суммирования вычетов, сумматоры, корректор ядра числа, анализаторы индексов знаковых чисел, корректор ранга числа, регистры первой, второй и третьей цифр полиадического кода числа, счетчики, регистр поправки, выходы полиадического кода, выход поправки, выход ранга числа, выход ядра числа, два элемента задержки. Блок суммирования вычетов содержит функциональные преобразователи, регистры, сумматоры, элементы задержки, блок формирования числа переполнений. 2 ил. (Л

| Преобразователь кодов из системы остаточных классов в полиадический код | 1977 |

|

SU637809A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования позиционных признаков непозиционного кода | 1981 |

|

SU1007098A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-23—Публикация

1984-09-14—Подача