Изобретение относится к области вычислительной -и дискретной техники, в частности, к устройствам для автоматической селекции и формирования считанных сигналов запоминающих устройств с неразрушающим считыванием, выходные сигналы которых различаются фазами полярностей.

Известен дискриминатор-формирователь сигналов, считанных с запоминающего устройства с неразрушающим считыванием, имеющий два парафазных входа и состоящий из двух триггеров и двух схем совпадения, причем щина одного нарафазного входа подключена к первому входу одной схемы совпадения, второй вход которой соединен с нулевым выходом первого триггера, соответствующим его исходному состоянию, а выход упомянутой схемы совпадения соединен с единичным установочным входом второго триггера, нулевой вход которого вместе с нулевым входом первого триггера нодключен к шине установки исходного состояния устройства.

Однако известное устройство требует формирования выходных импульсов ио длительности и амплитуде, а изменение питающих напряжений и амплитуд входных сигналов влияет на работоспособность устройства.

Цель изобретения - повышение надежности работы устройства.

Достигают этого тем, что шина другого парафазного входа подключается к единичному входу первого триггера, с его нулевым выходом соединяется первый вход другой схемы совпадения, второй вход которой подключается к -единичному выходу второго триггера, а выход этой схемы совпадения является выходом устройства.

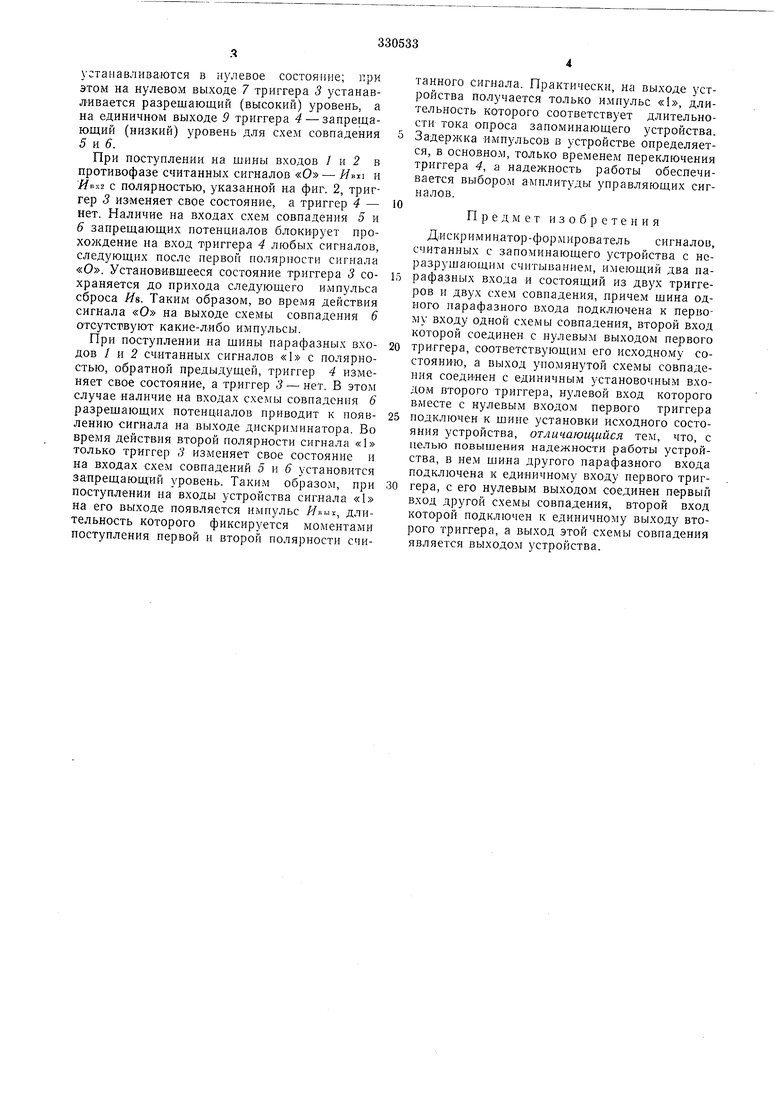

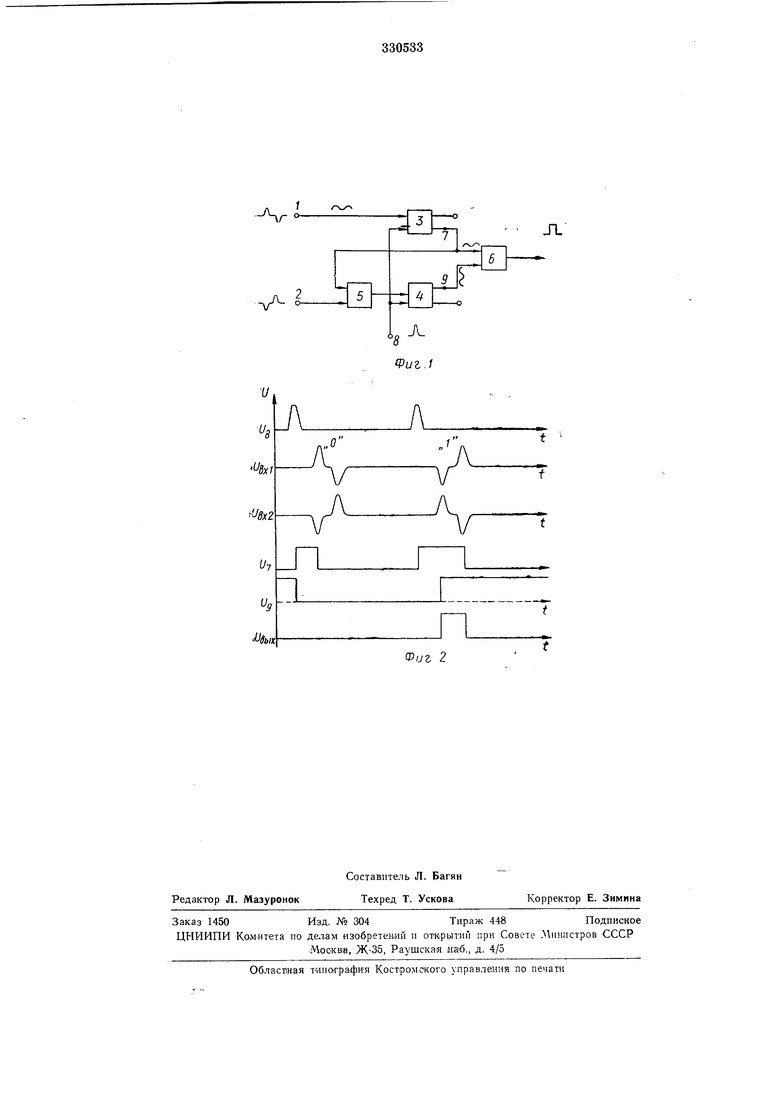

На фиг. 1 представлена функциональная блок-схема предложенного устройства; на фиг. 2 - временная диаграмма его работы.

Устройство содержит два парафазных в.хода 1 и 2, два триггера 3 и 4 (например, на транзисторах) и две схемы совпадення 5 и 6 (схемы «И). Шина парафазного входа 2 подключена к первому входу схемы совпадения 5, второй вход которой соединен с нулевым выходом 7 триггера 3. Выход схемы совпадения 5 соединен с единичным установочным входом триггера 4, нулевой вход которого в.месте с нулевым входом триггера 3 подключен к шине 8 установки исходного состояния устройства. Шина парафазного входа / подключена к единичному входу триггера 3, с нулевым выходом 7 которого соединен первый вход схемы совпадения 6, второй вход которой подключен к единичному выходу 9 триггера 4, а выход схемы совпадення 6 является выходом устройства.

Первоначально при помощи импульса сброса MS, подаваемого на шину 8, триггеры 3 и 4

устанавливаются в нулевое состояние; при этом на нулевом выходе 7 триггера 3 устанавЛивается разрешающий (высокий) уровень, а на единичном выходе 9 триггера 4 - запрещающий (низкий) уровень для схем совпадения

5и (J.

При поступлении на шины входов / и 2 в противофазе считанных сигналов «О - Яви и //ВХ2 с полярностью, указанной на фиг. 2, триггер 3 изменяет свое состояние, а триггер 4 - нет. Наличие на входах схем совпадения 5 и

6запрещающих потенциалов блокирует прохождение на вход триггера 4 любых сигналов, следующих после первой полярности сигнала «О. Установ-ИВщееся состояние триггера 3 сохраняется до прихода следующего импульса сброса Яв. Таким образом, во время действия сигнала «О на выходе схемы совпадения 6 отсутствуют какие-либо импульсы.

При поступлении на щины парафазных входов / и 2 считанных сигналов «I с полярностью, обратной предыдущей, триггер 4 изменяет свое состояние, а триггер 3 - нет. В этом случае наличие на в.ходах схемы совпадения 6 разрещающих потенциалов приводит к появлению сигнала на выходе дискриминатора. Во время действия второй полярности сигнала «1 только триггер 3 изменяет свое состояние и на входах схем совпадений 5 и 5 установится запрещающий уровень. Таким образом, при поступлении на входы устройства сигнала «1 на его выходе появляется импульс Явмг, длительность которого фиксируется моментами поступления первой и второй полярности считанного сигнала. Практически, на выходе устройства получается только импульс «I, длительность которого соответствует длительности тока опроса запоминающего устройства.

Задержка импульсов в устройстве определяется, в основном, только временем переключения триггера 4, -а надежность работы обеспечивается выбором амплитуды управляющих сигналов.

Предмет изобретения

Дискриминатор-формирователь сигналов, считанных с запоминающего устройства с неразрушающим считыванием, имеющий два парафазных входа и состоящий из двух триггеров и двух схем совпадения, причем шина одного парафазного входа подключена к первому входу одной схемы совпадения, второй вход которой соединен с нулевым выходом первого

триггера, соответствующим его исходному состоянию, а выход упомянутой схемы совпадения соединен с единичным установочным вхоДОЛ1 второго триггера, нзлевой вход которого вместе с нулевым входом первого триггера

подключен к шине установки исходного состояния устройства, отличающийся тем, что, с целью повышения надежности работы устройства, в нем шина другого парафазного входа подключена к единичному входу первого триггера, с его нулевым выходом соединен первый вход другой схемы совпадения, второй вход которой подключен к единичному выходу второго триггера, а выход этой схемы совпадения является выходом устройства.

о

%/

%2

t

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВУХПОЛЯРНЫХ СИГНАЛОВ В ПОТЕНЦИАЛЬНЫЕ | 1970 |

|

SU277015A1 |

| Устройство синхронизациии и нормирования импульсных последовательностей | 1981 |

|

SU957423A2 |

| ПРЕОБРАЗОВАТЕЛЬ ДВУХПОЛЯРНЫХ СИГНАЛОВ В ПОТЕНЦИАЛЬНЫЕ | 1969 |

|

SU247349A1 |

| Синхронизатор импульсов | 1976 |

|

SU741461A1 |

| Делитель частоты | 1975 |

|

SU518870A1 |

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1322471A1 |

| Устройство контроля веса материала в бункерах | 1980 |

|

SU972243A1 |

| Устройство для регистрации первой фазы сложного сигнала | 1981 |

|

SU993458A1 |

| Устройство синхронизации и нормирования импульсных последовательностей | 1979 |

|

SU855981A1 |

| Устройство синхронизации и нормирования импульсных последовательностей | 1986 |

|

SU1330743A1 |

фуг 2

Даты

1972-01-01—Публикация