Предложенный преобразователь предназначен для использования в составе запоминающих устройств, выходные сигналы которых различаются фазами полярностей импульсов в том случае, если возникает необходимость их стыковки с вычислительными устройствами, выполненными на потенциальных логических элементах.

Известные устройства такого назначения выполняют обычно на одном триггере, например на туннельном диоде.

Однако установление потенциального уровня, соответствующего двухполярному сигналу, происходит в такой схеме с задержкой на Бремя, равное временному интервалу между импульсами различной полярности, так как при одном сигнале, например «О, туннельный диод переключается дважды под действием обеих полярностей, а при другом - «1 под действием второй полярности. При этом сигналу «О соответствует низкий (высокий) уровень потенциала, а сигналу «1 - высокий (низкий) потенциал на выходе триггера.

При необходимости получения информации в прямом и обратном коде преобразователь имеет парафазный выход.

налы, соответствующий потенциальный уровень которых устанавливается с минимальной задержкой.

Это достигается тем, что в нем выходы двух триггеров через диоды подключены к входу инвертора, выход которого соединен с одноименными входами резистивных суммирующих схем, соединенных с триггерами, а вторые входы суммирующих схем через

диоды подключены к входным шинам.

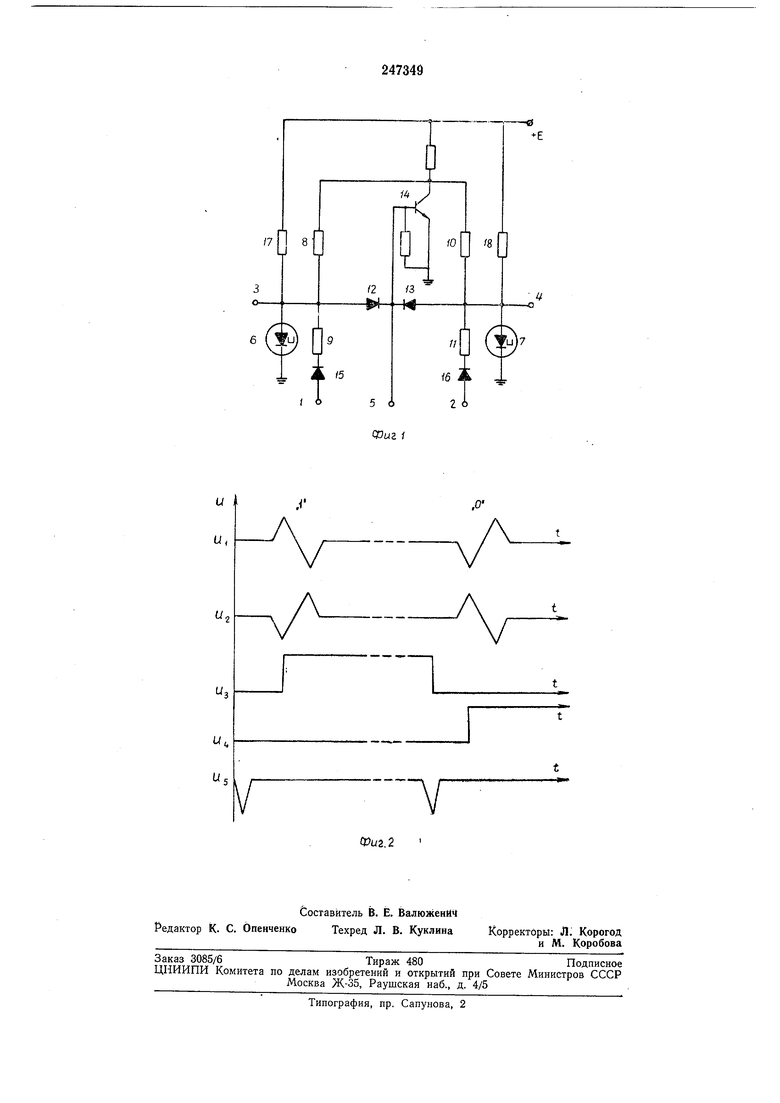

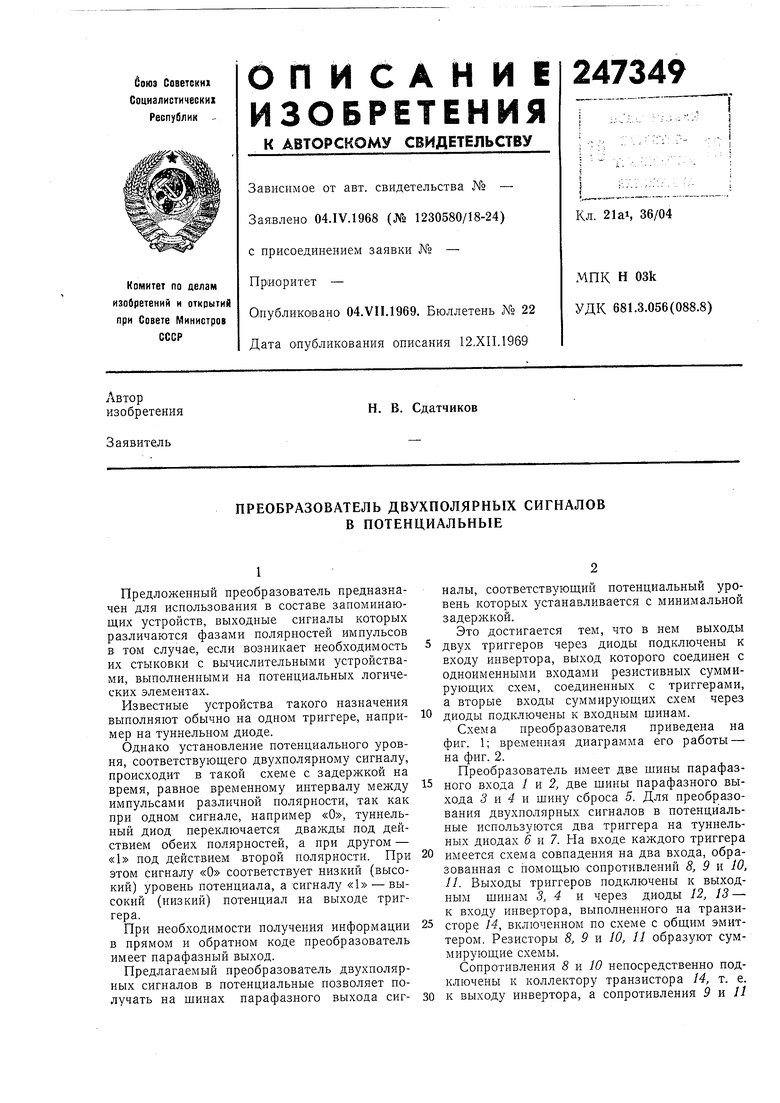

Схема преобразователя приведена на фиг. 1; временная диаграмма его работы - на фиг. 2. Преобразователь имеет две шины парафазного входа 1 к 2, две шины парафазного выхода 3 II 4 и шину сброса 5. Для преобразования двухполярных сигналов в потенциальные используются два триггера на туннельных диодах 5 и 7. На входе каждого триггера

имеется схема совпадения на два входа, образованная с помощью сопротивлений 8, 9 и 10, 11. Выходы триггеров подключены к выходным шинам 3, 4 -я через диоды 12, 13 - к входу инвертора, выполненного на транзисторе 14, включенном по схеме с общим эмиттером. Резисторы S, Р и 10, 11 образуют суммирующие схемы.

через диоды 15 и 16 - к шинам парафазного входа / и 2. Сопротивления 17 ti 18 образуют цепь смещения туннельных диодов 5 и 7 и обеспечивают их работу в режиме статического триггера.

Работа преобразователя заключается в следующем.

Первоначально триггеры с помощью отрицательного импульса сброса Us, подаваемого на шину 5, устанавливаются в нулевое состояние. При этом рабочие точки туннельных диодов 6 и 7 находятся на туннельной ветви их характеристик, и на выходных шинах 3 и 4 устанавливается низкий потенциал. Импульс сброса подается каждый раз перед поступлением двухполярных сигналов на шины 1 и 2. При наличии низкого потенцала на туннельных диодах 6 к 7 транзистор 14 заперт, а на его коллекторе имеется высокий потенциал.

Токи, протекающие при этом по сопротивлениям 8 и 10, не превышают порог переключения туннельных диодов 6 и 7, который определяется величинами сопротивлений 17 и 18.

При поступлении на входные шины сигнала «1 первая полярность на шине 1 (f/i) положительная, а на шине 2 (f/g) отрицательная туннельный диод 6 переключается, а диод 7 сохраняет свое первоначальное состояние, так как диод 16 заперт. Наличие высокого положительного потенциала на диоде 6, а следовательно, и на базе транзистоа 14, вызывает отпирание транзистора. При этом на коллекторе транзистора 14 устанавливается низкий потенциал, и ток через сопротивления 8 и 10 уменьшается практически до нуля.

При действии второй противоположной по фазе полярности сигнала «1 диоды и 7 не изменяют своего состояния, так как ток входного сигнала по сопротивлению 11 не превышает порога переключения диода 7, а диод 15 заперт. Таким образом, на шине 5 сохраняется высокий потенциал (t/з), а на шине 4 - первоначальный низкий потенциал (f/4).

Подобным образом схема работает и при

поступлении двухполярного сигнала «О (пер5 вая полярность на шине / - отрицательная,

а на шине 2 - положительная); только в этом

случае высокий потенциал устанавливается

на шине 4 и низкий на шине 3.

Время установления потенциального сигнал а практически определяется временем переключения туннельных диодов.

При малых временных интервалах между полярностями входных сигналов необходимо, чтобы транзистор инвертора переключался до момента поступления второй полярности сигнала, что практически легко обеспечивается, так как переключение транзистора форсируется туннельными диодами. Для надежной работы преобразователя

0 необходимо выполнение условий нормальной работы схем совпадения, т. е. суммарный ток по сопротивлениям 8, 9 н 10, 11 должен превышать порог переключения туннельных диодов 5 и 7 соответственно, а в отдельности

5 каждый из этих токов не должен превышать этот порог. Это достигается выбором величин этих сопротивлений.

Предмет изобретения

0 Преобразователь двухполярных сигналов в потенциальные с двумя парафазными входами и выходами, содержащий два триггера на туннельных диодах с резистивными суммирующими схемами на их входах и инвертор

5 на транзисторе, отличающийся тем, что, с целью уменьшения времени установления выходного потенциального сигнала, в нем выходы триггеров через диоды подключены к входу инвертора, выход которого соединен

0 с одноименными входами суммирующих схем, вторые входы которых через диоды подключены к входным шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВУХПОЛЯРНЫХ СИГНАЛОВ В ПОТЕНЦИАЛЬНЫЕ | 1970 |

|

SU277015A1 |

| Компаратор тока | 1986 |

|

SU1370758A1 |

| ПРЕОБРАЗОВАТЕЛЬ МОЩНОСТИ В ЧАСТОТУ | 1992 |

|

RU2057349C1 |

| ДИСКРИМИНАТОР | 1967 |

|

SU194424A1 |

| Датчик случайных двоичных сигналов | 1974 |

|

SU526871A1 |

| Аналоговое множительное устройство | 1979 |

|

SU860087A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

| ВПТБ | 1973 |

|

SU408455A1 |

| Логическая схема "или-и-не" | 1974 |

|

SU510784A1 |

и

и.

У

Даты

1969-01-01—Публикация