Преобразователь предназначен для использования в составе запоминающих устройств с неразрушаемым считыванием, выходные сигналы которых различаются фазами полярностей импульсов, если возникает необходимость в их стыковке с вычислительными устройствами на потенциальных логических элементах.

Известен преобразователь двухполярных сигналов в потенциальные уровни, выполненный на туннельных диодах с резистивными суммирующими схемами на их входах и инверторе на транзисторе.

Недостатком известного устройства является малый перепад потенциальных уровней (порядка 0,7-1 е) и критичность работы устройства к изменению питающих напряжений и амплитуд входных сигналов.

Предлагаемый: преобразователь обеспечивает установление потенциальных уровней, соответствующих входным двухполярным сигналам, с минимальной задержкой. Он отличается тем, что в нем выходы двух триггеров, начальный уровень потенциального сигнала на которых является разрешающим для схем совпадения, включенных на входы этих триггеров, соединены со входами каждой схемы совпадения, а третьи входы схем совпадения подключены ко входным шинам преобразователя. Схемы совпадения выполнены на нелинейных элементах, например диодах.

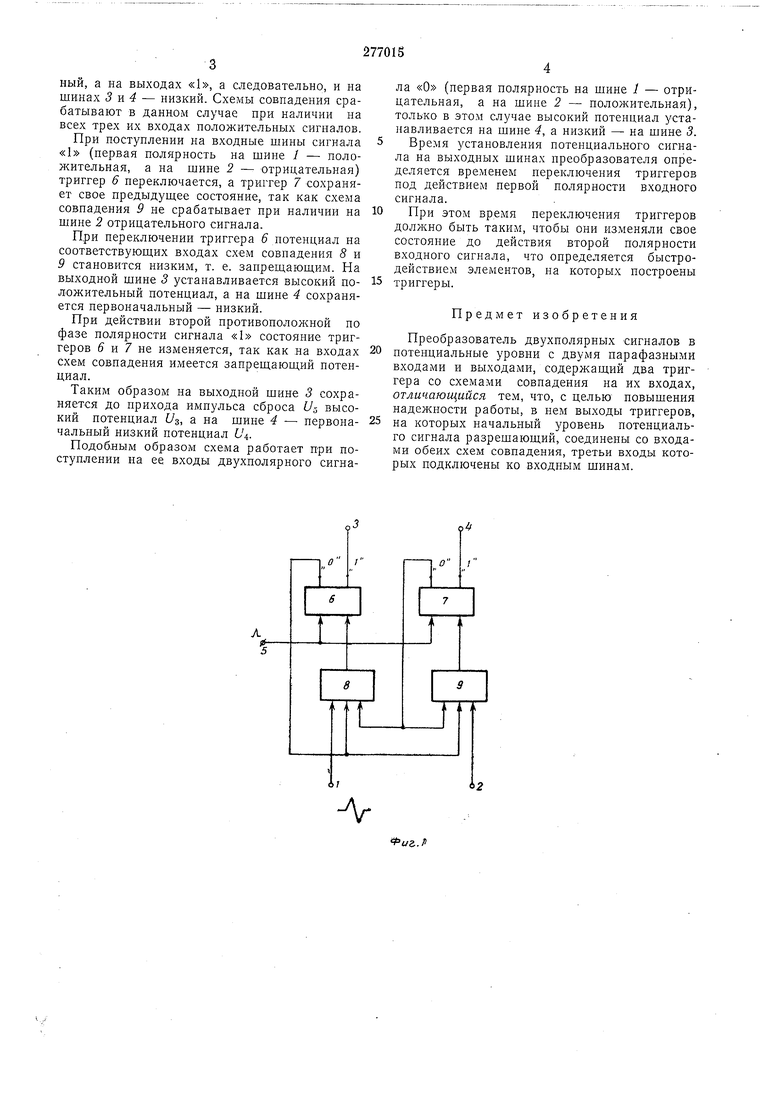

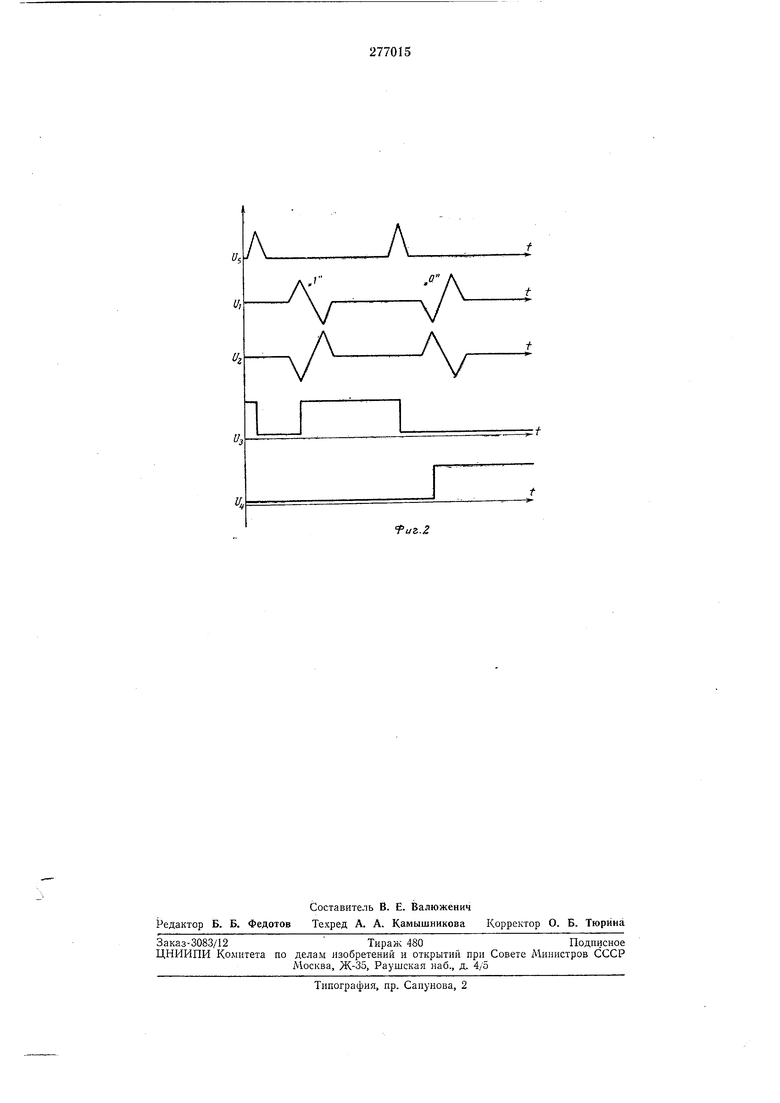

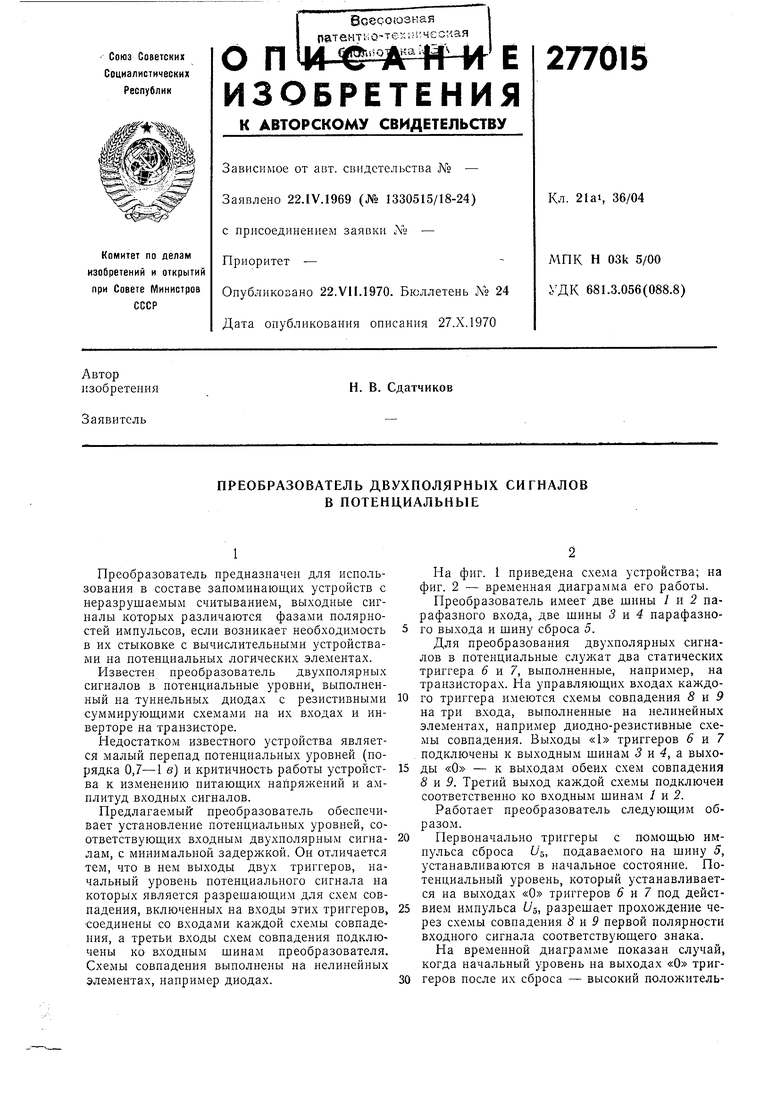

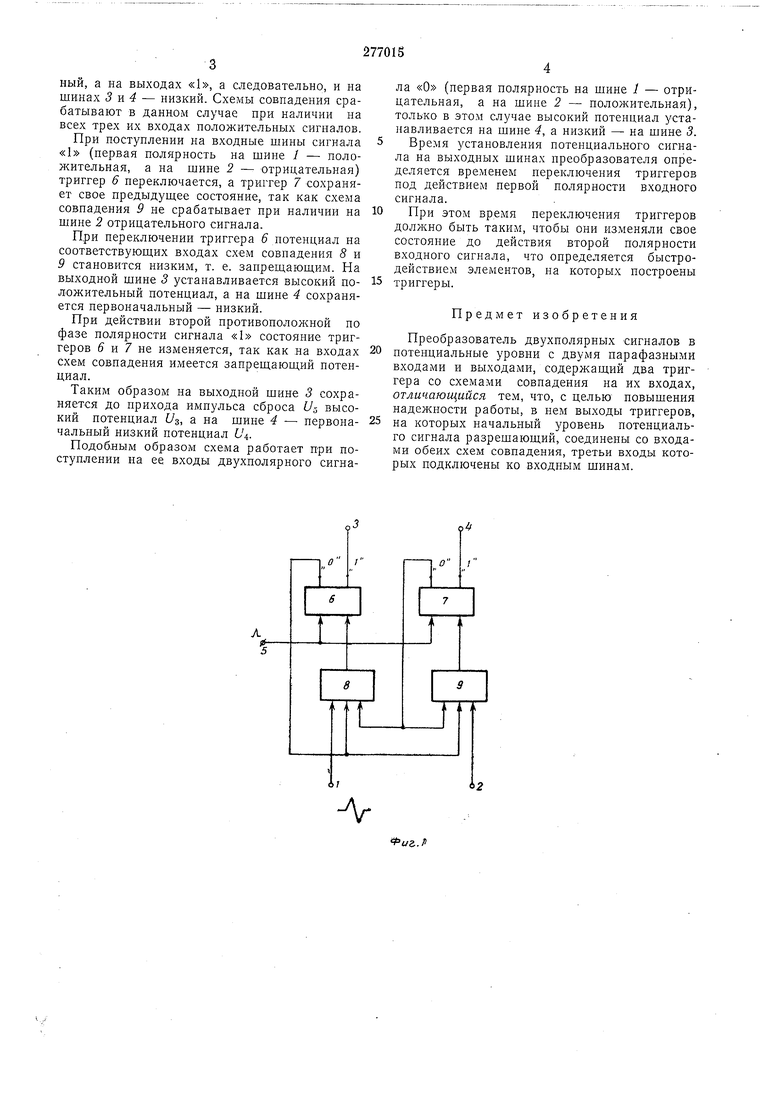

На фиг. 1 приведена схема устройства; на фиг. 2 - временная диаграмма его работы.

Преобразователь имеет две шины / и 2 парафазного входа, две шины 3 и 4 парафазного выхода и шину сброса 5.

Для преобразования двухполярных сигналов в потенциальные служат два статических триггера 6 и 7, выполненные, например, на транзисторах. На управляющих входах каждого триггера имеются схемы совпадения 8 к 9 на три входа, выполненные на нелинейных элементах, например диодно-резистивные схемы совпадения. Выходы «1 триггеров и 7 подключены к выходным шинам 3 v. 4, а выходы «О - к выходам обеих схем совпадения 8 Н 9. Третий выход каждой схемы подключен соответственно ко входным шинам 1 и 2.

Работает преобразователь следующим образом.

Первоначально триггеры с помощью импульса сброса L/5, подаваемого на шину 5, устанавливаются в начальное состояние. Потенциальный уровень, который устанавливается на выходах «О триггеров 6 н 7 под дей-ствием импульса бз, разрешает прохождение через схемы совпадения 8 к 9 первой полярности входного сигнала соответствующего знака.

ныи, а на выходах «1, а следовательно, и на шинах 3 и 4 - низкий. Схемы совпадения срабатывают в данном случае при наличии па всех трех их входах положительных сигналов.

При поступлении на входные шины сигнала «1 (первая полярность на шине / - полол :ительная, а на шине 2 - отрицательная) триггер 6 переключается, а триггер 7 сохраняет свое предыдушее состояние, так как схема совпадения 9 не срабатывает при наличии на шине 2 отрицательного сигнала.

При переключении триггера 6 потенциал на соответствующих входах схем совпадения 8 и 9 становится низким, т. е. запрещаюшим. На выходной шине 3 устанавливается высокий положительный потенциал, а на шине 4 сохраняется первоначальный - низкий.

При действии второй противоположной по фазе полярности сигнала «1 состояние триггеров 5 и 7 не изменяется, так как на входах схем совпадения имеется запрешаюш,ий потенциал.

Таким образом на выходной шине 3 сохраняется до прихода импульса сброса Us высокий потенциал Us, а на шине 4 - первоначальный низкий потенциал U.

Подобным образом схема работает при поступлении на ее входы двухполярного сигнала «О (первая полярность на шине 1 - отрицательная, а на шине 2 - положительная), только в этом случае высокий потенциал устанавливается на шине 4, а низкий - на шине 3.

Время установления потенциального сигнала на выходных шинах нреобразователя определяется временем переключения триггеров под действием первой полярности входного сигнала.

При этом время переключения триггеров должно быть таким, чтобы они изменяли свое состояние до действия второй полярности входного сигнала, что определяется быстродействием элементов, на которых построены

триггеры.

Предмет изобретения

Преобразователь двухполярных сигналов в потенциальные уровни с двумя парафазными входами и выходами, содержащий два триггера со схемами совпадения на их входах, отличающийся тем, что, с целью повышения надел иости работы, в нем выходы триггеров, на которых начальный уровень потенциальго сигнала разрешающий, соединены со входами обеих схем совпадения, третьи входы которых подключены ко входным шинам.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВУХПОЛЯРНЫХ СИГНАЛОВ В ПОТЕНЦИАЛЬНЫЕ | 1969 |

|

SU247349A1 |

| Фазо-импульсный преобразователь | 1980 |

|

SU875296A1 |

| ЦИФРОВОЙ ИНТЕГРИРУЮЩИЙ ВОЛЬТАМПЕРМЕТР | 1972 |

|

SU347909A1 |

| ДИСКРИМИНАТОР-ФОРМИРОВАТЕЛЬ | 1972 |

|

SU330533A1 |

| ВПТБ | 1973 |

|

SU408455A1 |

| Устройство для регистрации первой фазы сложного сигнала | 1981 |

|

SU993458A1 |

| Преобразователь напряжение-код с коррекцией динамической погрешности | 1975 |

|

SU898609A1 |

| Формирователь биполярных сигналов | 1990 |

|

SU1780156A1 |

| Синхронизатор импульсов | 1976 |

|

SU741461A1 |

| СЛЕДЯЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2045813C1 |

Л

Даты

1970-01-01—Публикация