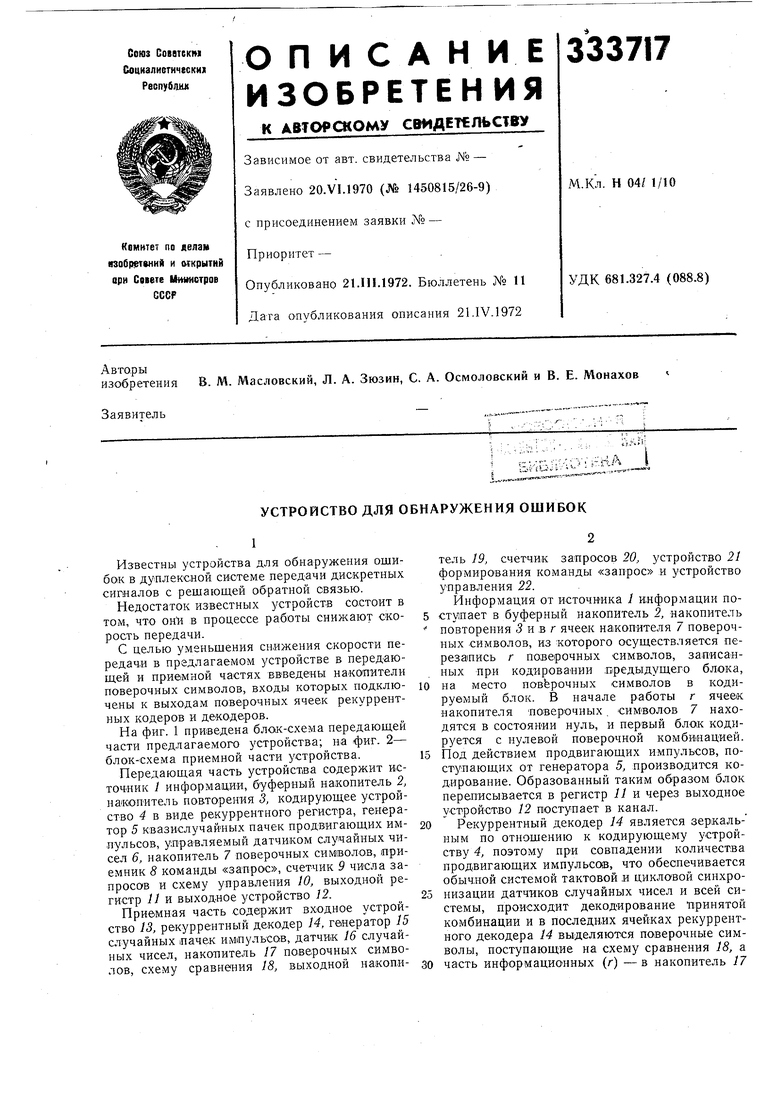

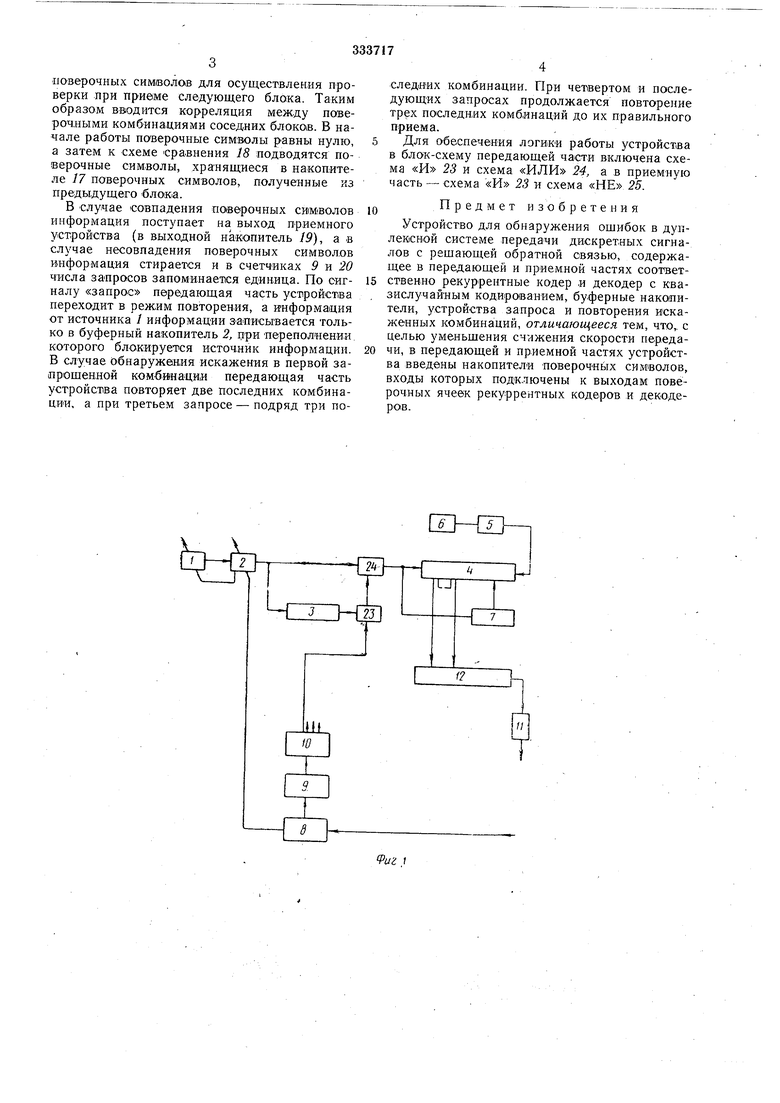

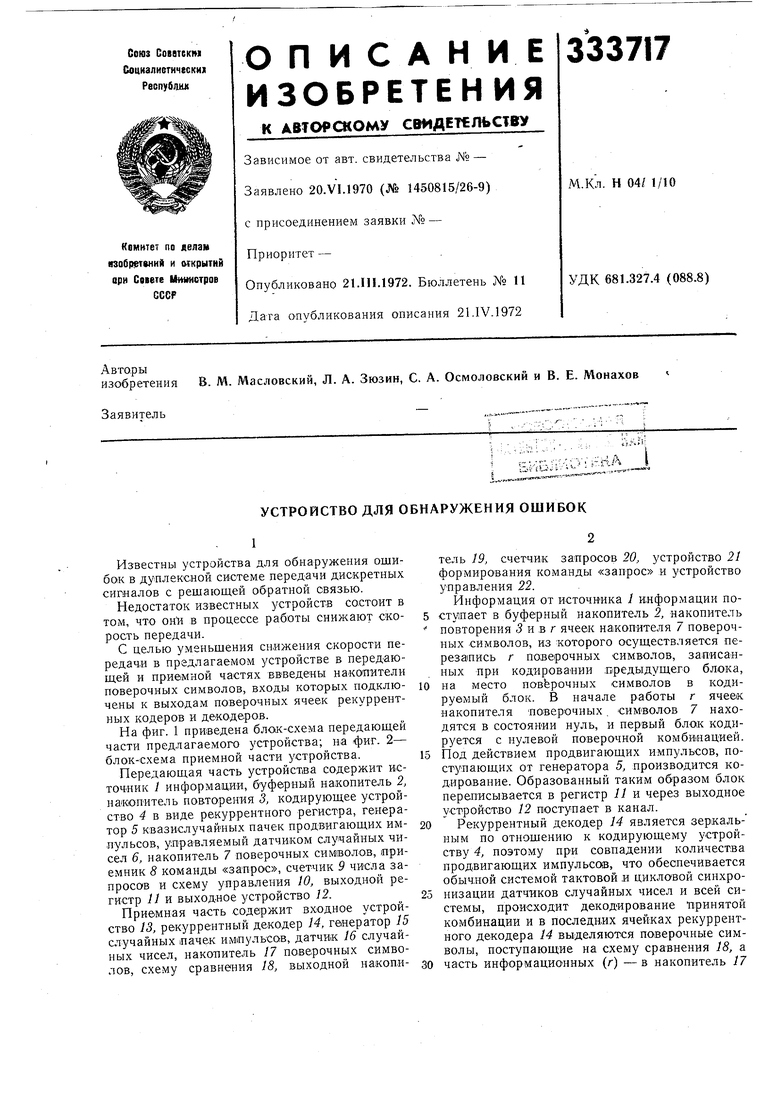

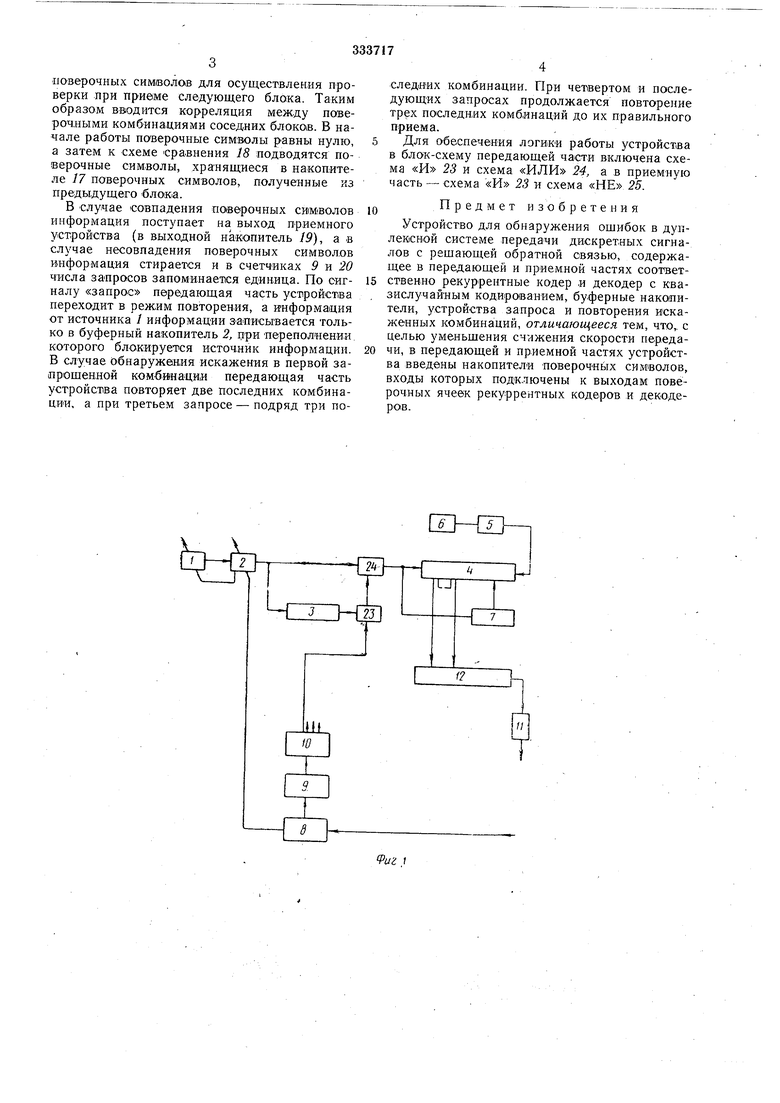

Известны устройства для обнаружения ошибок в дуплексной системе передачи дискретных сигналов с решающей обратной связью. Недостаток известных устройств состоит в том, что OHYi в процессе работы снижают скорость передачи. С целью уменьшения снижения скорости передачи в предлагаемом устройстве в передаюш,ей и приемной частях вв-ведены накопители поверочных символов, входы которых подключены к выходам поверочных ячеек рекуррентных кодеров и декодеров. На фнг. 1 приведена блок-схема передающей части предлагаемого устройства; на фиг. 2- блок-схема приемной части устройства. Передающая часть устройства содержит истоЧНик 1 информации, буферный накопитель 2, накопитель повторения 5, кодирующее устройство 4 в виде рекуррентного регистра, генератор 5 квазислучайных пачек продвигающих импульсов, управляемый датчиком случайных чисел 6, накопитель 7 поверочных символов, ириемник 8 команды «запрос, счетчик 9 числа запросов и схему управления 10, выходной регистр 11 ъ выходное устройство 12. Приемная часть содержит входное устройство 13, рекуррентный декодер 14, генератор 15 случайных пачек импульсов, датчик 16 случайных чисел, накот1итель 17 поверочных символов, схему сравнения 8, выходной накопитель 19, счетчик запросов 20, устройство 21 формирования команды «запрос и устройство управления 22. Информация от источника 1 информации поступает в буферный накопитель 2, накопитель повторения 5 и в г ячеек накопителя 7 поверочных символов, из которого осуществляется перезапись г поверочных символов, зап-исаиных при кодировании предыдущего блока, на место поверочных символов в кодируемый блок. В начале работы г ячеек накопителя поверочных, символов 7 находятся в состоянии нуль, и первый блок кодируется с нулевой поверочной комбидацией. Под действием продвигающих импульсов, поступающих от генератора 5, производится кодирование. Образованный таким образом блок переписывается в регистр 7/ и через выходное устройство 12 поступает в канал. Рекуррентный декодер 14 является зеркальным по отношению к кодирующему устройству 4, поэтому прИ совпадении количества продвигающих импульсо В, что обеспечивается обычной системой тактовой и цикловой синхронизации датчиков случайных чисел и всей системы, происходит декодирование принятой комбинации и в последних ячейках рекуррентного декодера 14 выделяются поверочные символы, поступающие на схему сравнения 18, а часть информационных (г) -в накопитель 17

поверочных символов для осуществления проверки при приеме следующего блока. Таким образом вводится корреляция между поверочными комбипадиями соседних блоков. В начале работы поверочные сим:волы равны нулю, а затем к схеме Сравнения 18 подводятся поверочные СИМ-ВОЛЫ, хранящиеся в накопителе 17 поверочных символов, полученные из предыдущего -блока.

В случае совпадения поверочных символов информация поступает на выход приемного устройства (в выходной накопитель 19), а в случае несовпадения поверочных символов информация стирается и в счетчиках 9 20 числа запросов запоминается единица. По сигналу «запрос передающая часть уст1ройСТ|Ва переходит в режим повторения, а Информащия от источника / информации з-адаисывается только в буферный накопитель 2, при переполнении которого блокируется источник информации. В случае Обнаружения искажения в первой запрощенной ком-бинацйи передающая часть устройства повторяет две последних комбинации, а при третьем запросе - подряд три последйих комбинации. При четвертом и последующИх запросах продолжается повторение трех последних комблнаций до их правильного приема.

Для обеспечения логики работы устройства в блок-схему передающей части включена схема «И 23 и схема «ИЛИ 24, а в приемную часть -схема «И 23 и схема «НЕ 25.

Предмет изобретения

Устройство для обнаружения ошибок в дуплексной системе передачи дискретных сигналов с рещающей обратной связью, содержащее в передающей и приемной частях соответственно рекуррентные кодер и декодер с квазислучайным кодированием, буферные накскпители, устройства запроса и повторения искаженных комбинаций, отличающееся тем, что,, с целью уменьшения снижения скорости передачи, в передающей и приемной частях устройства введены накопители поверочнйх символов, входы которых подключены к выходам поверочных ячеек рекуррентных кодеров и декодеров.

/Jpjifioui

Itf

яана/1

11

%.

i9

Авторы

Даты

1972-01-01—Публикация