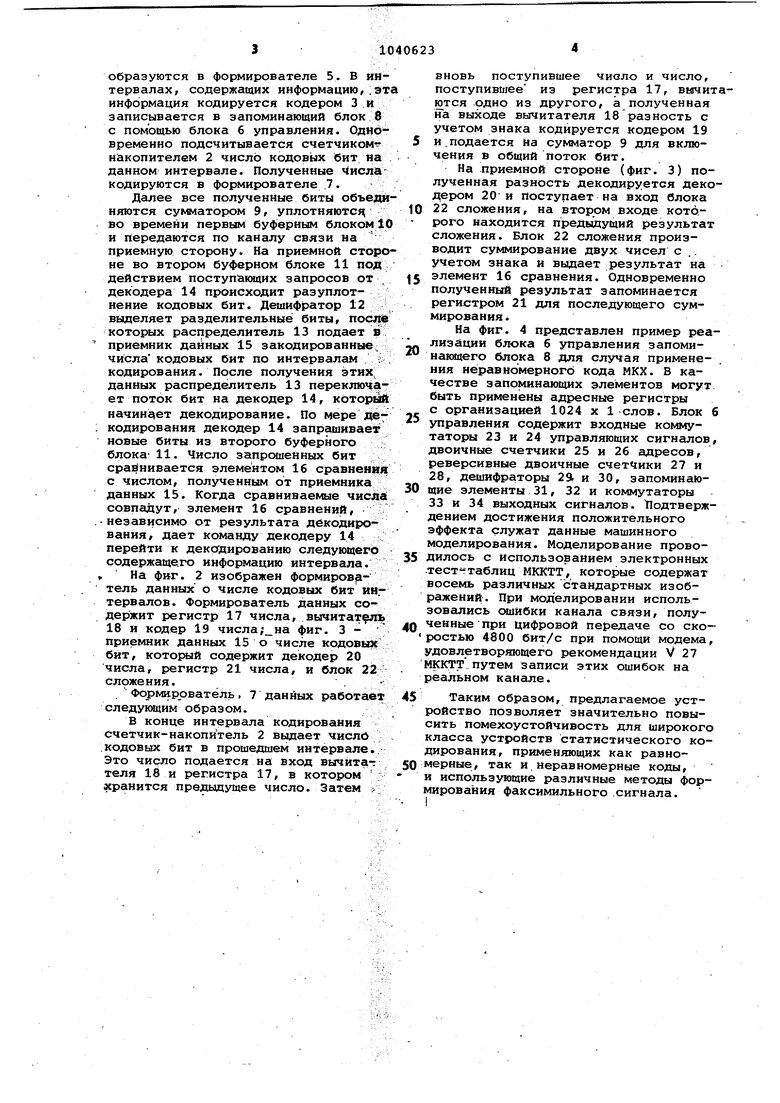

Изобретение относится к факсимил ной технике, в частности к устройст вам сжатия объема передаваемых сигналов путем статистического кодиро.вания, и может быть использовано дл передачи информации, закодированной как равномерньам, так и неравномерным кодом. Известно устройство статистйчесчого кодирования и декодирований факсимильных сигналов,.которое на передающей стороне содержит вхойной делитель видеосигнала. Выход делите подан на кодер видеосигнала, формирователь разделительных бит, формирователь бит описания, формировател сигнала адреса, выходы которых через после.довательно саединенн а е сумматор и первый буферный блок под ны в канал связи. Кроме того, допол нительный выход кодера видеосигнала подключен к. дополнительному входу формирователя сигнала адрес. На при емной стороне известное устройство содержит последовательно соединенные второй буферный блок, дешифрато разделительных бит, распределитель, дешифратор сигнала адреса и декодер 1. ,. Недостаток известного устройства заключается, в сравнительно низкой помехоустойчивости, что обуславлив аетс.я наличием в сигнале бит адрес Цель изобретения - повышение помехоустойчивости при передаче факсимильных сигналов. Указанная цель достигается тем, что в устройство статистического кодирования и декодирования факсимильных сигналов, содержащее на пер дающей стороне входной делитель, выход которого соединен с входом кодера видеосигнала и через формирователь разделительных бит и формирователь бит описания с двумя входами сумматора, выход которого ; подключен к входу первого буферного блока, а на приемной стороне последовательно соединенные второй буфер ный блок,дешифратор разделительных бит, распределитель и декодер видео сигнала первый выход которого является выходом устройства, а втор выход соединен с управляющим входом второго буферного блока, введейы на передающей стороне последовательно соединенные счетчик-нокопитель и формирователь данных о числе кодовы бит, включенные между выходом входного делителя и первым дополнительным входом сумматора, и последОвательно соединенные блок управления и запоминающий блок, включенные между выходом кодера видеосигнала и BiojwM дополнительным входом сумматора, причем выход кодера соеди.нен с вторым входом счетчика-накопителя, а дополнительный выход коде .ра видеосигнала - с вторым входом запоминающего блока, а на приемной стороне последовательно соединенные приемник данных о числе кодовых бит к злемент сравнения, включенные между дополнительным выходом распределителя и вторым входом декодера видеосигнала, второй выход которого Соединен с вторым входом элемента сравнения. На фиг. 1 представлена структурная электрическая схема устройства статистического кодирования и декодирования факсимильных сигналов, на фиг. 2 - структурная электрическая схема формирователя данных о числе кодовых бит; на фиг. 3 - структурная электрическая схема приемника данных о числе кодовых бит; на фиг. 4 - структурная электрическая схема блока управления и запоминающего блока для случая применения неравномерного кода (модифицированного кода Хаффмена (МКХ). Устройство статистического кодирования и декодирования факсимильных сигналов (фиг. 1) содержит на передающей стороне входной делитель 1, выход которого соединен с первым входом счетчика-накопителя 2 и со входами кодера 3 видеосигнала, формирователя 4 разделительных бит, формирователя 5 бит описания. Второй вход счетчика-накопителя 2 вместе со входом б управления подключен к дополнительному выходу кодера 3, выход счетчика-накопителя 2 подан на вход формирователя 7 данных о числе кодовых бит, а выход блока б управления - на вход запоминающего блока 8. Выходы формирователя 7 данных, запоминающего блока 8, формирователя 4 разделительныхбит и формирователя 5 бит описания подсоединены к соответствующим входам сумматора 9, выход которого через первый буферный блок 10 подан в канал связи. На приемной стороне устройство содержит последовательно соединенные второй буферные .блок 11., дешифратор 12 разделитель Ных бит, распределитель 13 и декодер 14 видеосигнёша. вторым выходом распределиттеля 13 и вторым входом декодера 14 введены последовательно соединенные приемник 15данных о числе кодовых бит и элемент 16 сравнения, второй вход которого подключен ко второму выходу декодера 14 и к управляющему входу второго буферного блока 11. Устройство работает следующим образом. Входной сигнал во входном делителе 1 делится йа строки и на и.нтер-, валы кодирования. Вначале строки развертки после разделительных бит, Сформированных формирователем 4, передаются биты описания строки по интервалам кодирования. Эти биты

бразуются в формирователе 5. В инервалах, содержащих информацию,.эта нформация кодируется кодером 3 .и записывается в запоминающий блок 8 помощью блока 6 управления. Одноременно подсчитывается счетчиком-г накопителем 2 число кодовых бит на анном интервале. Полученные кодируются в формирователе .7.

Далее все полученные биты объединяются сумматором 9, уплотняютс во времени первым буферным блоком 10 и передаются по каналу связи на приемную сторону. На приемной стороне во втором буферном блоке 11 под ействием поступающих запросов от декодера 14 происходит разуплотнение кодовых бит. Дешифратор 12 выделяет разделительные биты, после которых распределитель 13 подает в приемник данных 15 закодированные, числа кодовых бит по интервалам . . кодирования. После получения этих данных распределитель 13 переключает поток бит на декодер 14, который начинает декодирование. По мере де кодирования декодер 14 запрашивает новые биты из второго буферного блока- 11. Число запрсяиенных бит сравнивается элементом 16 сравнения с числом, полученным от приемника данных 15. Когда сравниваемые числа совпадут, элемент 16 сравнений,

независимо от результата декодирования, дает команду декодеру 14 перейти к декргдированию следующего содержащего информацию интервала.

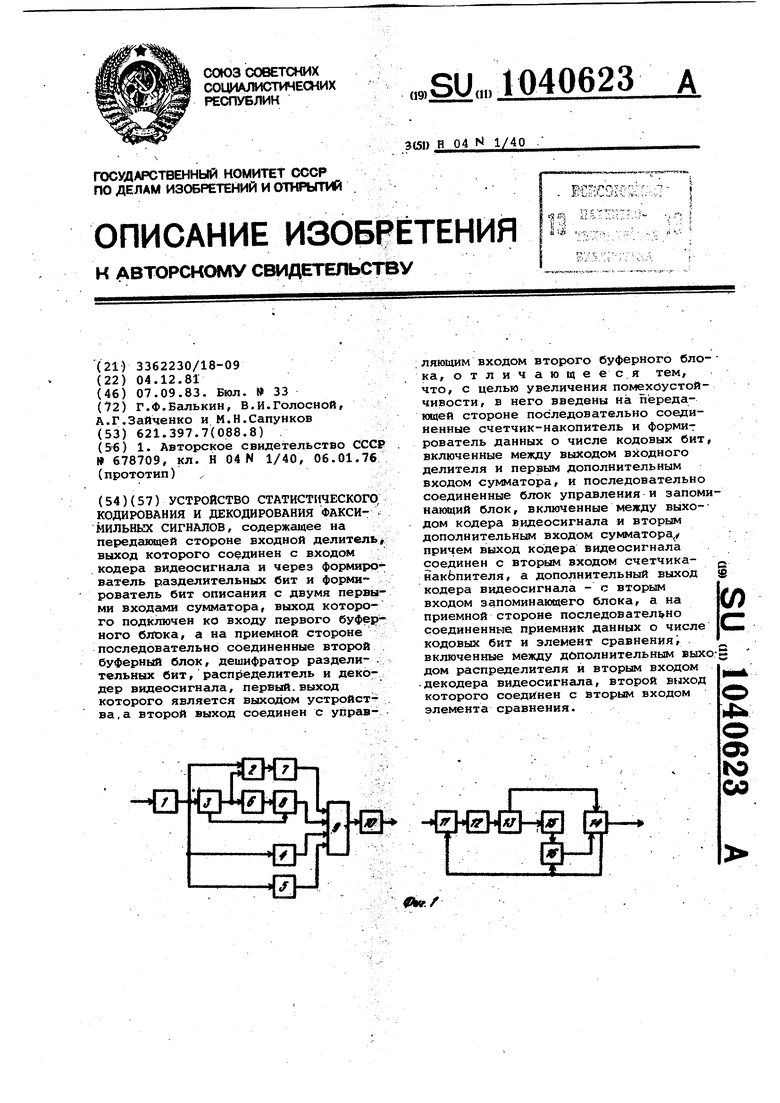

На фиг. 2 изображен формиров тель данных о числе кодовых бит интервалов. Формирователь данных содержит регистр 17 числа, вычитат ль 18 и кодер 19 числа; на фиг. 3 приемник данных 15 о числе кодовых бит, который содержит декодер 20 числа, регистр 21 числа, и блок 22 слржения..

Формирователь, 7 данйых работает следукяцим образом.

В конце интервала кодирования четчик-накопитель 2 выдает число

кодовых бит в прошедшем интервале. Это число подается на вход вычитателя 18 и регистра 17, в котором ранится предыдущее число. Затем

вновь поступившее число и число, поступившее из регистра 17, вычитаются 9ДНО из другого, а полученная на выходе вычитателя 18 разность с учетом знака кодируется кодером 19 и,подается на сумматор 9 для включения в общий поток бит.

На приемной стороне (фиг. 3) полученная разность декодируется декодером 20и Поступает на вход блока

22 сложения, на втором входе которого находится предыдущий результат сложения. Блок 22 сложения производит суммирование двух чисел с .. учетом знака и выдает результат на

элемент 16 сравнения. Одновременно полученный результат запоминается регистром 21 для последующего суммирования.

На фиг. 4 представлен пример реализации блока 6 управления запоминакадего блока 8 для случая примене- . ния неравномерного кода МКХ. В качестве запоминающих элементов могут быть применены адресные регистры с организацией 1024 х 1 слов. Блок 6

управления содержит входные коммутаторы 23 и 24 управляющих сигналов, двоичные счетчики 25 и 26 адресов, реверсивные двоичные 27 и 28, дешифраторы 29 и 30, запоминающие элементы 31, 32 и коммутаторы 33 и 34 выходных сигналов. 11одтверждением достижения положительного эффекта служат данные машинного моделирования. Моделирование проводилось с использованием электронных -тестттаблиц МККТТ, которые содержат восемь различных стандартных изображений. При моделировании использовались сшИбки канала связи, полученные при цифровой передаче со скоростью 4800 бит/с при помощи модема, удовлетворяющего рекомендации V 27 МККТТ путем записи этих ошибок на реальном канале.

Таким образом, предлагаемое устройство позволяет значительно повысить помехоустойчивость для широкого класса устройств статистического коди{ювания, применяющих как равномерные, так и неравномерные коды, и использующие различные методы формирования факсимильного сигнала.

fpt/f.

n€fp

го

И

0vt.J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство статистического кодирования и декодирования факсимильных сигналов | 1985 |

|

SU1332560A2 |

| Устройство кодирования и декодирования факсимильных сигналов | 1980 |

|

SU1043834A1 |

| Устройство для сжатия спектра видеосигнала | 1976 |

|

SU678709A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство для моделирования алгоритмов цифрового статистического кодирования-декодирования видеосигналов | 1983 |

|

SU1231626A1 |

| Устройство для передачи и приема дискретной информации с коррекцией ошибок | 1988 |

|

SU1578825A2 |

| МНОГОПАРАМЕТРИЧЕСКАЯ АДАПТИВНАЯ СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 2010 |

|

RU2441330C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2356179C1 |

| Устройство для передачи и приемадиСКРЕТНОй иНфОРМАции C КОРРЕКциЕйОшибОК | 1979 |

|

SU809615A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ ВИДЕОСИГНАЛА, ПРЕДСТАВЛЯЮЩЕГО ИЗОБРАЖЕНИЯ, ПРИЕМНИК ТЕЛЕВИЗИОННОГО СИГНАЛА, ВКЛЮЧАЮЩЕГО ДАННЫЕ ЗАГОЛОВКОВ И ПОЛЕЗНЫЕ ДАННЫЕ В ВИДЕ СЖАТЫХ ВИДЕОДАННЫХ | 1992 |

|

RU2128405C1 |

УСТРОЙСТВО СТАТИСТИЧЕСКОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ФАКСИМИЛЬНКХ СИГНАЛОВ, содержащее на переданяцей стороне входной делитепь выход которого соединен с входом кодера видеосигнала и через формиро ватель разделительных бит и формирователь бит описания с двумя первыми входами сумматора, выход которого подключен ко входу первого буферного блt)кa, а на приемной стороне последовательно соединенные второй буферный блок, дешифратор раздели-тельных бит, распределитель и декодер видеосигнала, первый, выход которого является выходом устройст--- . ва,а второй выход соединен с управ:ляющим входом второго буферного блока, отличающееся тем, что, с целью увеличения помехоустойчивости , в него введены на передающей стороне последовательно соединенные счетчик-накопитель и формит рователь данных о числе кодовых бит, включенные между выходом входного делителя и первым дополнительным входом сумматора, и последовательно соединенные блок управления и запоминающий блок, включенные между выходом кодера видеосигнала и вторым дополнительным входом сумматора у причем выход кодера видеосигнала соединен с вторым входом счетчиканакЬпителя, а дополнительный выход кодера видеосигнала - с вторым (Л входом запоминающего блока, а на приемной стороне последовательно с соединенные приемник данных о числе кодовых бит и элемент сравненияi включенные между дополнительным выхо дом распределителя и вторым входом декодера видеосигнала, второй выход которого соеД11нен с вторым входом элемента сравнения. Од OQ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для сжатия спектра видеосигнала | 1976 |

|

SU678709A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-09-07—Публикация

1981-12-04—Подача