Изобретен1ие относится к области вычислительной те.хиики, в частности к преобразопателя.м цифровой (|Юрмы представления ннфор.мации в аналоговую, и может быть использова-по в системах вывода :И(Ифор.ма|Ци.и из цифровы.х вычислительных устройств.

РЬвестны многокзнальпые преобразовател и кода в напряжение, содержащие общий для все.х каналов преобразователь .кода в папряжепие, выход которого соединен с одним входом схемы сравие|П1Ия, другой вход которой через коммутатор подключен к выходам ннтсграторов, HCT04iHHK эталлотнюго напряжения и устройство управления.

Однако для работы известного устройства необходимо получить код приращения преобразуемого напряжения ,и корректировать его для компенсации дрейфа иитегратора, что услож1няет программу вьггислений в цифровом вычислительном устройстве и связь иоследнего с многоканальны:м преобразователем кода в напряжение.

С целью повышения надежаюсти предлагаемый многокаиальный преобразователь кода в иапряже.На-1е содержит в каждом ка«але вентнль, триггер и ключ, причем выход схемы срависиня через вентили И триггеры соединен с унраВляющ1НМ11 входа.м.и ключей, другне входы которых подключены к разиополяриым щинам источника эталонного напряження, а выходы к.тючей соединены со входами интегратор о,в.

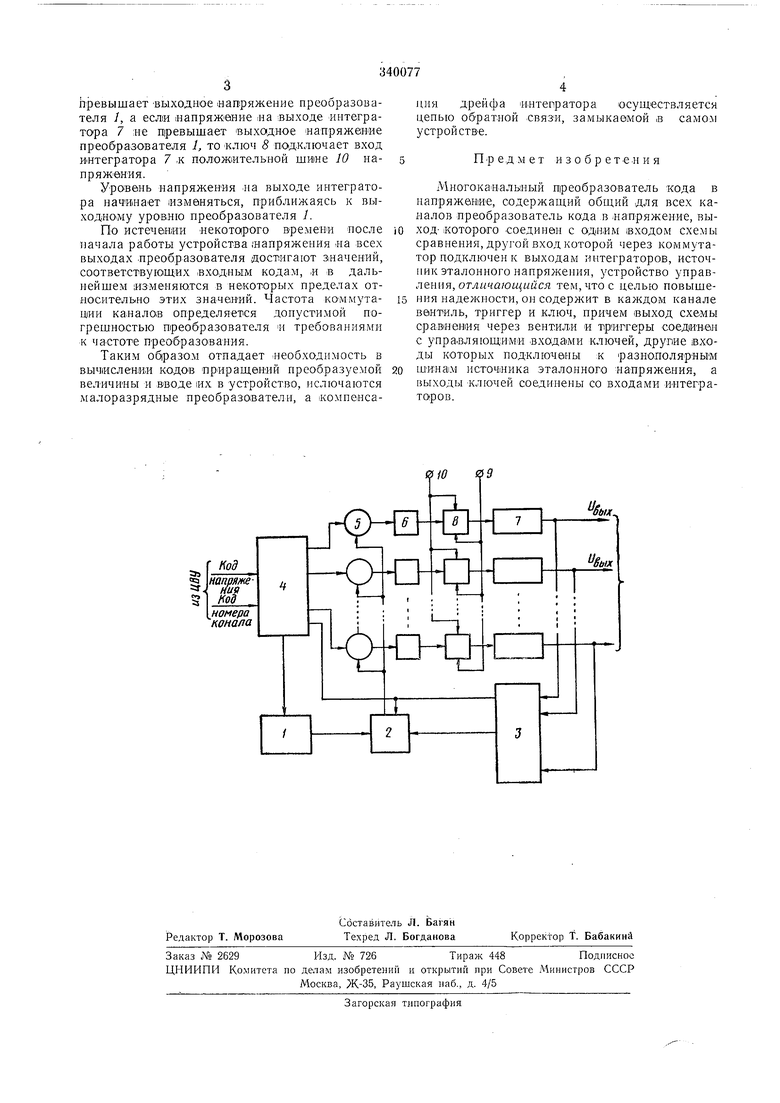

На чертеже предста влена функциональная блок-схема предлагаемого устройства.

Устройство содержит общий для всех каналов преобразователь 1 кода в напряженпе, схему сравнения 2, коммутатор 3 и устройство унравлення 4.

Каждый канал преобразователя содержит вентиль 5, триггер 6, интегратор 7 и 5.

На вход устройства управления 4 поступают из ци:фрового вычислительного устройства код номера очередного канала и код напряжения, декодируемого по данному каналу. По сигналу из устрой.ства управления 4 коммутатор 3 подключает выход иптегратора 7 соответствующего ка-иала ко входу схемы сравнения 2, одновременно открывается вентнль 5 того же канала, а код декодируемого иапряжен ия из устройства управления 4 поступает на вход преобразователя /. Вы.ходное 1гапряженне последнего сравиивается с напряжением на выходе соотзетствуюпл,ега каиала в схеме сравиения 2, с выхода которой сигнал о знаке рассогласования 4iepe3 открытый вентиль 5 поступает «а триггер 6 и запоминается. Ключ 8, управляемый триггером 7, подключает пход интегратора 7 к отрицательной шине 9 напряжения, если напряженне на его выходе

превышает выходное «ашряжение преобразователя /, а если иапряжвние иа выходе интегратора 7 ;не превышает выходное «апряжение преобразователя 1, то «люч 8 подключает вход ННтегратора 7 ,к положительной шине 10 напряжения.

Уровень напряжения .на выходе ннтегратора начинает изменяться, приближаясь к выходному ypoBiHio преобразователя /.

По истечении «екоторого времен1И носле начала работы устройства (напряжения ла всех выходах .преобразователя достигают значений, соответствующих входным кодам, ,и в дальнейшем изменяются в некоторых пределах относительно этих значений. Частота коммутаHJИи каналов определяется допустимой погрешностью преобразователя и требованиями к частоте преобразования.

Таким об|разом отпадает .необходимость в вычислении кодов прираш,вний преобразуемой величины и вводе их в устройство, ислючаются малоразрядные преобразователи, а компенсация дрейфа интегратора осушествляется цепью обратной .связи, замыкаемой в самом устройстве.

Предмет и з о б р е т .е .и и я

Многока налыный нреобразователь кода в напряжение, содержащий общий для всех каналов преобразователь кода в «апряжеиие, выход-iKOTO.poiro .соединен с одним входом схемы сравнения, другой вход которой через коммутатор нодключен к выходам интеграторов, источник эталонного напряжения, устройство управления, отличаюм ыйся тем, что с целью повышеВИЯ надежности, он содержит в каждом канале вентиль, триггер и ключ, причем выход схемы срав1нения через вентили и триггеры со.ед1ИН:ви с управляющим1И входами ключей, другие IBXOды которых подключены к разнополяр-ньш mwHaiM источника эталонного -напряжения, а выходы ключей соединены со входами интеграторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU947958A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1056449A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1970 |

|

SU271917A1 |

| ЦИФРОВОЕ СПЕЦИАЛИЗИРОВАННОЕ УСТРОЙСТВО | 1970 |

|

SU275526A1 |

| АВТОМАТИЧЕСКОЕ ИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 1967 |

|

SU190070A1 |

| ЦИКЛИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ «УГОЛ —КОД» | 1972 |

|

SU346793A1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ ИНФОРМАЦИИ | 1967 |

|

SU222908A1 |

| Преобразователь код-сдвиг фазы | 1972 |

|

SU439917A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬBr^irr^f^^.ocitJ и а ^ и»^ ^^- \^ f "^.' -^' S i.' . /I'i.';'^-:; •^;-"'-J ; iXJ'4-'^, | 1972 |

|

SU332567A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА — КОД | 1973 |

|

SU372684A1 |

0/ 05

8ш

Даты

1972-01-01—Публикация