Изобретение относится к области вычислительной техники.

Известны цифровые специализированные устройства для решения дифференциальных уравнений и арифметических задач, выполненные на интеграторах, содержащих соединенные между собой 7-регистр, / -регистр, линии задернски и логические элементы.

Однако известные устройства недостаточно быстродейственны и имеют невысокую точность вычисления при решении задач с большим числом операций умножения, деления.

В предложенном устройстве эти недостатки исключены.

Устройство отличается от известных тем, что в нем нулевые выходы триггеров / -регистра каждого интегратора через схему совпадений подключены к дополнительным входам управления одного или нескольких других интеграторов; входы уиравления каждого интегратора подключены ко входам группы последовательно соединенных и зашунтированных нормально замкнутыми ключами вентплей, свободный вход первого из которых подключен к выходу источника тактовых импульсов, а выход последнего соединен со входом счнтывания информации с / -регистра; едиинчные выходы триггеров У-регистра соединены с установочными входами триггеров 7 -регистра через вентили переноса, вторые входы которых через линии задержки подключены ко входам прираш,енпя аргумента интегрируемых функцнй.

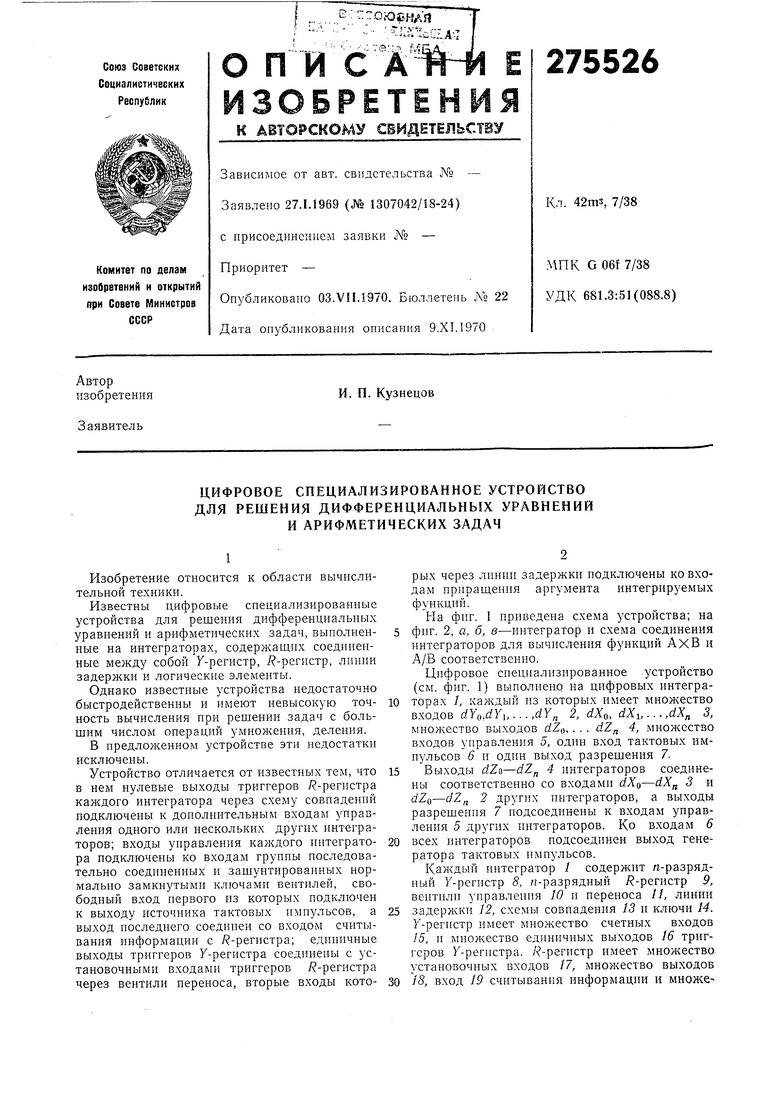

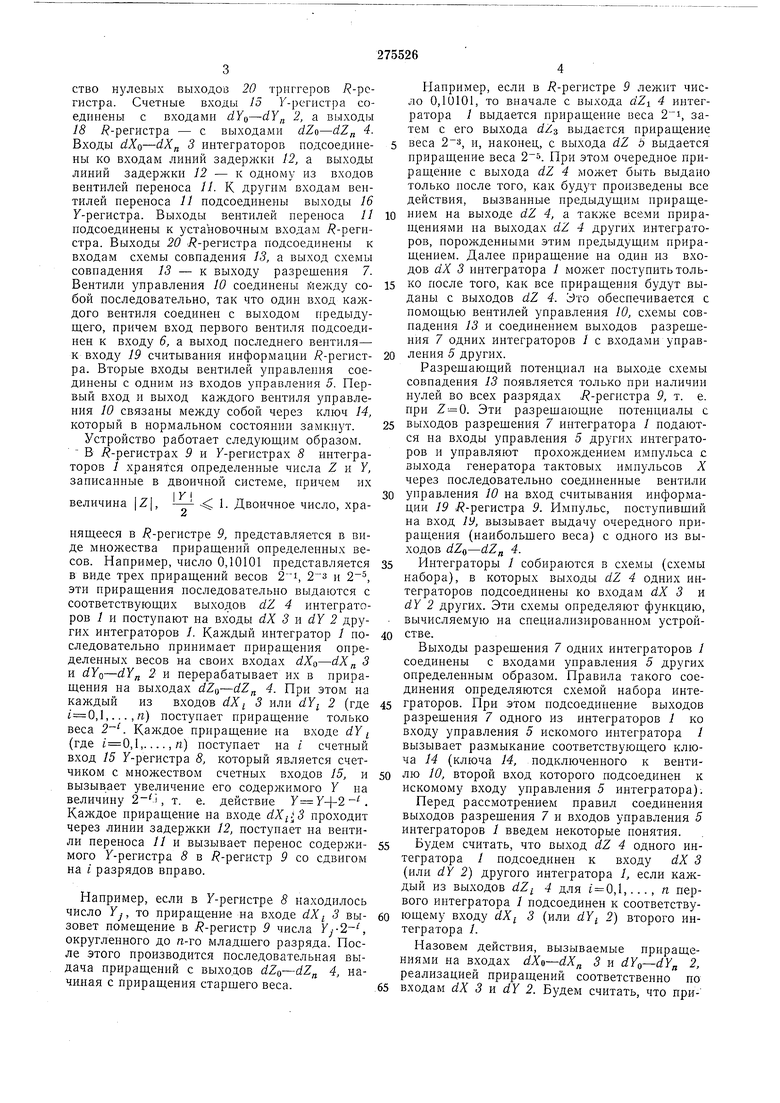

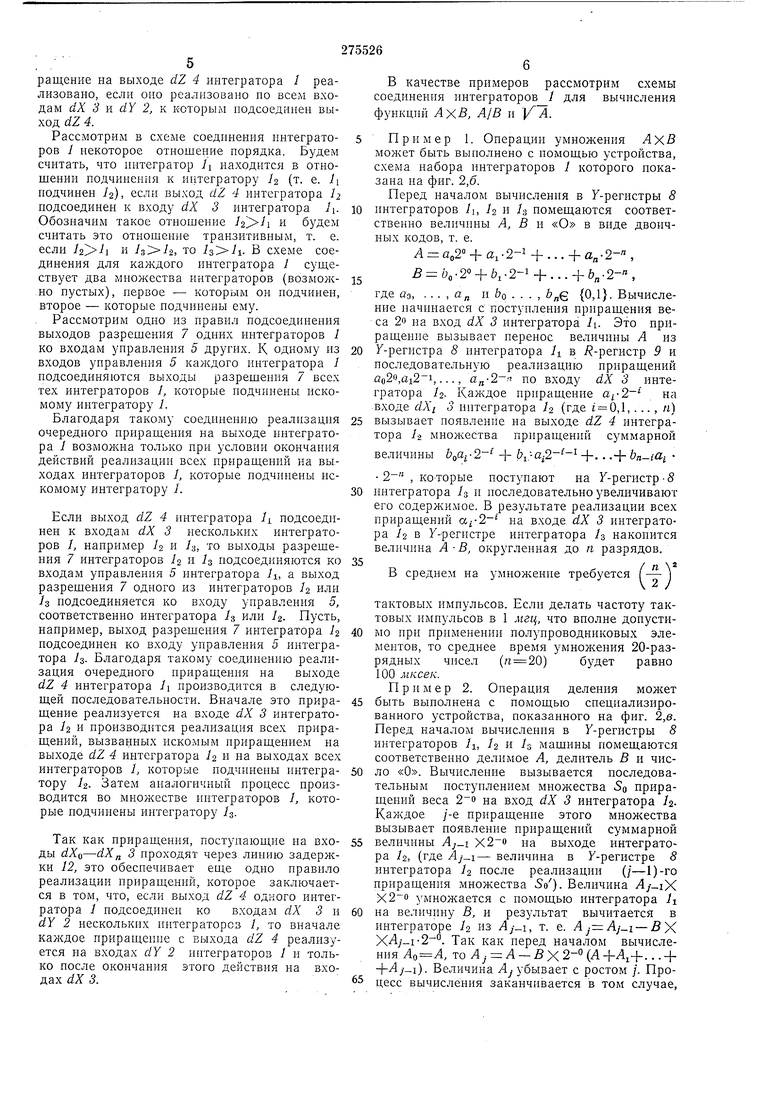

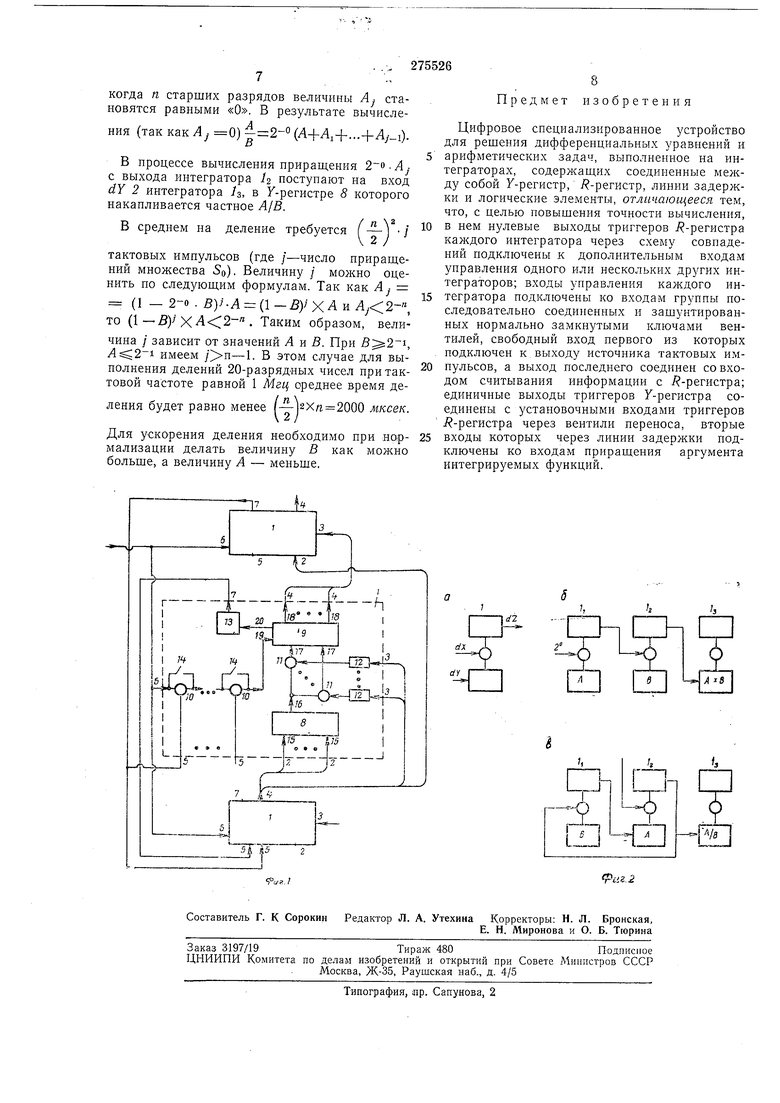

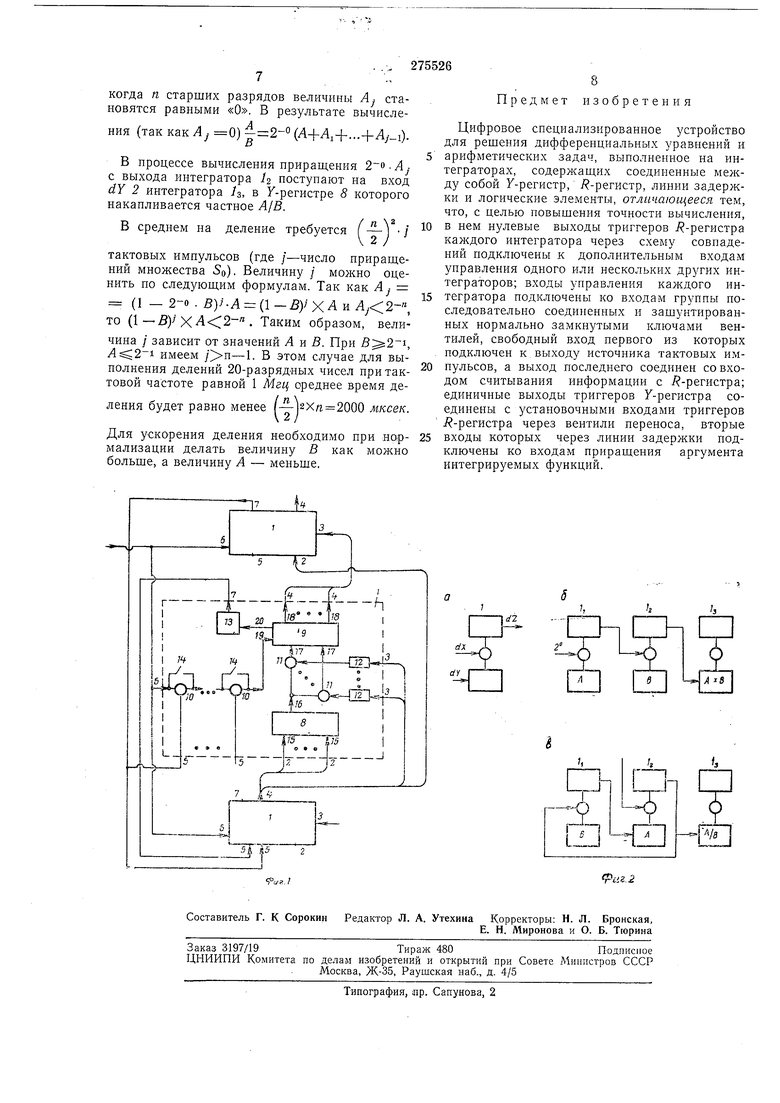

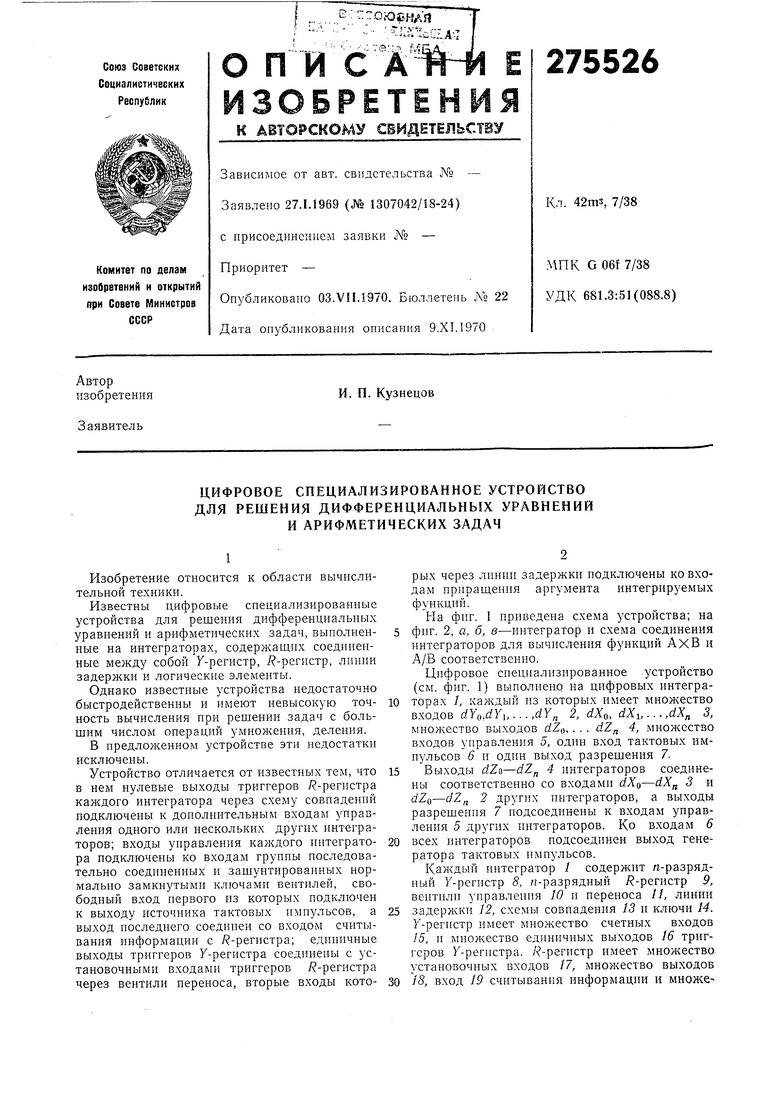

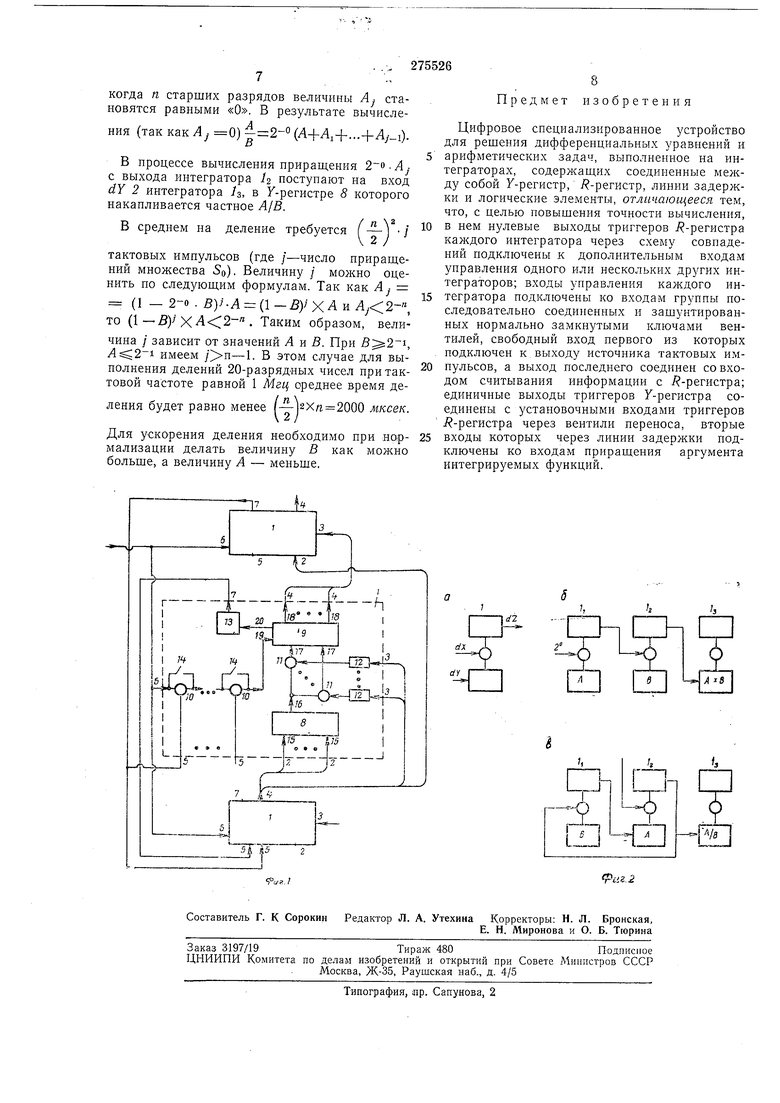

На фиг. 1 приведена схема устройства; на фиг. 2, а, б, в-интегратор и схема соединения интеграторов для вычисления функций АхВ и А/В соответственно.

Цифровое специализированное устройство (см. фиг. 1) выполнено на цифровых интеграторах 1, каждый из которых имеет множество входов dYo,dYb...,dY,, 2. dXo, dXi,...,dX 3, множество выходов dZf,,. . . dZ 4, множество входов управления 5, один вход тактовых импульсов 6 п один выход разрешения 7.

Выходы dZo-dZ 4 интеграторов соединены соответственно со входами 3 и (iZo-rfZ,, 2 других интеграторов, а выходы разрешення 7 подсоединены к входам управления 5 других интеграторов. Ко входам 6

всех интеграторов подсоединен выход генератора тактовых импульсов.

Каждый интегратор / содержит п-разрядный У-регнстр 8, /i-разрядный / -регистр 9, вентилн управления 10 п переноса //, линии

задержки 12, схемы совпадения 13 и ключи 14. У-регистр имеет множество счетных входов 15, и множество единичных выходов 16 триггеров У-регпстра. / -регистр имеет множество установочных входов 17, множество выходов

ство нулевых выходов 20 триггеров У -регистра. Счетные входы 15 1-регистра соединены с входами dYo-dY 2, а выходы 18 / -регистра - с выходами afZo-dZ 4. Входы dXo-dX 3 интеграторов подсоединены ко входам линий задержки 12, а выходы линий задержки 12 - к одному из входов вентилей иереноса 11. К другим входам вентилей нереноса 11 подсоединены выходы 16 У-регистра. Выходы вентнлей переноса 11 подсоединены к установочным входам / -регистра. Выходы 20 -Т -регистра подсоединены к входам схемы совпадения 13, а выход схемы совпадения 13 - к выходу разренления 7. Вентнли управления 10 соединены йежду собой последовательно, так что один вход каждого вентиля соединен с выходом предыдущего, причем вход первого вентиля подсоединен к входу 6, а выход последнего вентиля- к входу 19 считывания информации / -регистра. Вторые входы вентилей унравления соединены с одним из входов управления 5. Первый вход и выход каждого вентиля управления 10 связаны между собой через ключ 14, который в нормальном состоянии замкнут. Устройство работает следуюндим образом. В / -регистрах 9 и У-регнстрах 8 интеграторов 1 хранятся определенные числа Z и У, записанные в двоичной системе, причем их

I Y величина Z, --- 1. Двоичное число, храЛ/

иящееся в / -регистре 9, представляется в виде множества приращений онределеииых весов. Например, число 0,10101 представляется в виде трех приращений весов , н 2, эти приращения носледовательно выдаются с соответствующих выходов dZ 4 интеграторов 1 и поступают на входы dX 3 и dY 2 других интеграторов 1. Каждый интегратор 1 последовательно принимает приращения определенных весов на своих входах dXg-dX 3 и Й УО-dY 2 н перерабатывает их в приращения на выходах dZo-с 7„ 4. При этом на каждый из входов dXi 3 или rfFj 2 (где ,l,...,n) поступает приращение только веса 2-. Каждое приращение на входе dY (где ,l,...., п) поступает на i счетный вход 15 У-регистра 8, который является счетчиком с множеством счетных входов 15, и вызывает увеличение его содерл имого Y на величину 2--, т. е. действие У У+2-. Каждое нриращеиие на входе dXi.3 проходит через линии задержки 2, поступает на вентили переноса // и вызывает перенос содержимого У-регистра 8 в / -регистр 9 со сдвигом на i разрядов вправо.

Например, если в У-регистре 8 находилось число Уу, то приращение на входе dX 3 вызовет помещение в -регистр 9 числа Уу2-, округленного до п-го младщего разряда. После этого производится последовательная выдача приращений с выходов 4, начиная с приращения старщего веса.

Например, если в -регистре 9 лежит число 0,10101, то вначале с выхода aZj 4 интегратора / выдается нриращение веса , затем с его выхода dZs выдается нриращение 5 веса , и, наконец, с выхода dZ b выдается нриращение веса . При этом очередное приращение с выхода dZ 4 может быть выдано только после того, как будут произведены все действия, вызванные нредыдущим приращением на выходе dZ 4, а также всеми нриращениямн на выходах dZ 4 других интеграторов, порожденными этим предыдущим приращением. Далее приращение на один из входов dK 3 интегратора I может поступитьтоль5 ко после того, как все приращения будут выданы с выходов dZ 4. Это обеспечивается с помощью вентилей управления 10, схемы совпадения 13 и соединением выходов разрещения 7 одних интеграторов 1 с входами унрав0 ления 5 других.

Разрещающий потенциал на выходе схемы совпадения 13 появляется только при наличии нулей во всех разрядах -регистра 9, т. е. при Z 0. Эти разрещающие потенциалы с

5 выходов разрещения 7 интегратора / подаются на входы управления 5 других интеграторов и управляют прохождением импульса с выхода генератора тактовых импульсов X через последовательно соединенные вентили

0 унравления 10 на вход считывания информации 19 R-регистра 9. Импульс, ностунивщий на вход 19, вызывает выдачу очередного приращения (наибольщего веса) с одного из выходов ufZo-dZ 4.

5 Интеграторы / собираются в схемы (схемы набора), в которых выходы dZ 4 одних интеграторов подсоединены ко входам dX 3 и dY 2 других. Эти схемы определяют функцию, вычисляемую на специализированном устрой0 стве.

Выходы разрещения 7 одних интеграторов / соединены с входами управления 5 других определенным образом. Правила такого соединения определяются схемой набора интеграторов. При этом нодсоединение выходов разрещеиия 7 одного из интеграторов 1 ко входу управления 5 искомого интегратора / вызывает размыкание соответствующего ключа 14 (ключа 14, подключенного к венти0 лю 10, второй вход которого подсоединен к

искомому входу управления 5 интегратора).

Перед рассмотрением правил соединения

выходов разрещения 7 и входов управления 5

интеграторов / введем некоторые понятия.

5 Будем считать, что выход dZ 4 одного интегратора / подсоединен к входу dX 3 (или dY 2) другого интегратора 1, если каждый из выходов dZ 4 для t 0,Iп первого интегратора / подсоединен к соответствующему входу dX 3 (или dYi 2) второго интегратора /.

Назовем действия, вызываемые приращениями на входах dXn-dX 3 и 2, реализацией приращений соответственно по 5 входам dX 3 } dY 2. Будем считать, что приращение на выходе dZ 4 интегратора / реализовано, если оно реализовано но всем входам dX 3 и dY 2, к которым нодсоединен выход dZ 4.

Рассмотрим в схеме соединения интеграторов У некоторое отношение норядка. Будем считать, что иитегратор /i находится в отношении подчинения к интегратору Iz (т. е. li подчинен /2), если выход dl 4 интегратора 1 нодсоединен к входу dX 3 интегратора h. Обозначнм такое отношение и будем считать это отношение транзитивным, т. е. если и , то . В схеме соединения для каждого интегратора / существует два множества интеграторов (возможно пустых), первое - которым он подчинен, второе - которые подчинены ему. . Рассмотрим одно из правил подсоедпнення выходов разрешения 7 одних интеграторов 1 ко входам унравлення 5 других. К одному из входов управлепия 5 каждого интегратора / подсоединяются выходы разрешения 7 всех тех интеграторов 1, которые нодчинены искомому интегратору 1.

Благодаря такому соединению реализацня очередного нрнращения на выходе интегратора 1 возможна только при условии окончания действий реализации всех приращений на выходах ннтеграторов 1, которые подчинены искомому интегратору /.

Если выход C/Z 4 интегратора Д подсоединен к входам dX 3 нескольких интеграторов /, напрнмер 1 и 1, то выходы разрешення 7 интеграторов 1ч н 1 нодсоединяются ко входам управления 5 интегратора 1, а выход разрешения 7 одного из интеграторов 1 нлн /3 нодсоединяется ко входу унравлеиия 5, соответственно интегратора 1$ или 1-2. Пусть, например, выход разрешения 7 интегратора /2 подсоедииен ко входу управления 5 интегратора /3- Благодаря такому соединению реализация очередного нрнращеиия на выходе dZ 4 интегратора /i производится в следующей носледовательности. Вначале это приращение реализуется на входе dX 3 интегратора /2 и производится реализация всех приращений, вызванных искомым прнращеннем на выходе dZ 4 интегратора 1 и на выходах всех интеграторов 1, которые нодчинены интегратору /2. Затем аналогичный процесс нроизводится во множестве иитеграторов 1, которые нодчииены иитегратору /зТак как нриращения, постунающие на входы dXo-dXn 3 проходят через линию задержки 12, это обеспечивает еще одио правило реализации приращений, которое заключается в том, что, если выход dZ 4 одного интегратора 1 подсоединен ко входам d.X 3 и dY 2 нескольких ннтеграторов /, то вначале каждое приращение с выхода dZ 4 реализуется на входах dY 2 ннтеграторов 1 и только носле окончания этого действия на входах dX 3.

В качестве примеров рассмотрим схемы соединеиня ннтеграторов / для вычисления функцнй АхВ, А/В и .

Пример 1. Онерации умножения АхВ может быть вынолнено с помощью устройства, схема набора интеграторов / которого ноказана на фиг. 2,6.

Перед началом вычисления в 7-регистры 8 интеграторов Л, Iz и Is помещаются соответственно величины А, В и «О в виде двоичных кодов, т. е.

А а,2 + а,.2- + ... + а„-2-,

5 6о-2° + -2-1 + ... + &„-2-,

где (Зо, . . . , а„ н &о - - - , „6 {ОД}- Вычисление начннается с постунления прнращения веса 2 на вход dX 3 интегратора h. Это приращеппе вызывает перенос величины Л из

F-регистра 8 интегратора Л в У -регистр 9 и носледовательную реализацию приращений ,,..., а„-2 по входу dX 3 интегратора /2. Каждое прнращение на входе dXi 3 интегратора /2 (где t 0,l, . .. , я)

вызывает ноявленне на выходе dZ 4 интегратора 1-2 множества приращений суммарной

величины boai-2 -f &i. +...+ Ьп-иг

2, которые поступают на У-регистр-S интегратора 1з и носледовательно увеличивают его содержимое. В результате реализации всех приращений на входе dX 3 интегратора /2 в У-регистре интегратора /з накопится величина А В, округленная до п разрядов.

„./ « N

В среднем на умноженне треоуется -

2

тактовых имнульсов. Если делать частоту тактовых импульсов в 1 мгц, что вполне допустиМО при прнмененин полунроводниковых элементов, то среднее время умножения 20-разрядных чисел () будет равно 100 мксек. П р и м ер 2. Операция деления молсет

быть выполнена с помощью специализированного устройства, показанного на фиг. 2,8. Перед началом вычисления в У-регистры 8 интеграторов 1, Iz и /з машины помещаются соответственно делимое А, делитель В и число «О. Вычисление вызывается последовательным поступлением множества SQ приращений веса на вход dX 3 интегратора /2Каждое /-е нриращенне этого множества вызывает ноявление приращений суммарной

величины AJ-I на выходе интегратора /2, (где величина в У-регистре 8 интегратора /2 после реализации (/-1)-го приращеиия множества So). Величина умножается с помощью интегратора li

на величину В, и результат вычитается в интеграторе Iz из , т. е. Aj-Aj i - BX . Так как перед началом вычисления , то Aj A - BX2-°(...). Величина Л убывает с ростом /. Прокогда п старших разрядов величины Aj становятся равными «О. В результате вычисления (так как Aj 0) (.-.+Лу-:). В процессе вычисления приращения .Aj с выхода интегратора /2 поступают на вход dY 2 интегратора 1з, в 7-регистре 8 которого накапливается частное А/В. В среднем на деление требуется (-) / тактовых импульсов (где /-число приращений множества So). Величину / ыожио оценить по следующим формулам. Так как Л - (1 - 2-0 . В)}-А (1-ВУХА и , то (1-5ХхЛ 2-«. Таким образом, величина / зависит от значений А и В. При , имеем . В этом случае для выполнения делений 20-разрядных чисел при тактовой частоте равной 1 Мгц среднее время деления будет равно менее /-|2Х 2000 мксек. Для ускорения деления необходимо при нормализации делать величину В как можно больше, а величину А - меньше. 8 Предмет изобретения Цифровое специализированное устройство для решения дифференциальных уравнений и арифметических задач, выполненное на интеграторах, содержащих соединенные между собой У-регистр, / -регистр, линии задержки и логические элементы, отличающееся тем, что, с целью повышения точности вычисления, в нем нулевые выходы триггеров / -регистра каждого интегратора через схему совпадений подключены к дополнительным входам управления одного или нескольких других интеграторов; входы управления каждого интегратора подключены ко входам группы последовательно соединенных и зашунтированных нормально замкнутыми ключами вентилей, свободный вход первого из которых подключен к выходу источника тактовых импульсов, а выход последнего соединен со входом считывания информации с -регистра; единичные выходы триггеров У-регистра соединены с установочными входами триггеров -регистра через вентили переноса, вторые входы которых через линии задержки подключены ко входам приращения аргумента интегрируемых функций.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ АНАЛИЗАТОР ПОСЛЕДОВАТЕЛЬНОГО ТИПА | 1970 |

|

SU281025A1 |

| Устройство для цифрового дифференцирования | 1975 |

|

SU608145A1 |

| Круговой интерполятор для контурных систем программного управления станками | 1973 |

|

SU484502A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1968 |

|

SU218541A1 |

| Устройство для вычисления функции у= х | 1976 |

|

SU593210A1 |

| Число-импульсное устройство для вычисления обратного тригонометрического тангенса | 1983 |

|

SU1092498A1 |

| Вычислительное устройство | 1984 |

|

SU1170461A1 |

| АВТОРУЛЕВОЙ, РЕАЛИЗУЮЩИЙ ПРОПОРЦИОНАЛЬНО- ИНТЕГРАЛЬНО-ДИФФЕРЕНЦИАЛЬНЫЙ ЗАКОН УПРАВЛЕНИЯ | 1968 |

|

SU213943A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНЫХ КОДОВ ПРИРАЩЕНИЯ ФУНКЦИИ | 1968 |

|

SU208344A1 |

| ЭКСТРАПОЛЯТОР с ОКРУГЛЕНИЕМ ПРИРАЩЕНИЙдля | 1970 |

|

SU279192A1 |

Даты

1970-01-01—Публикация