Изобретение относится к радиотехнике, а именно к технике магнитной записи.

Известны устройства для магнитной записи, выполненые с времязадающей схемой, управляемой сигналами, поступающими от датчика, который, в свою очередь, в процессе воспроизведения информации управляет схемой «И, связанной с усилителем воспроизведения. Однако в таких устройствах возможно появление ложных 1ПОСЫЛОК информации .на выходе усилителя воспроизведения в момент подачи на него напряжения питания.

Цель изобретения-предотвращение появления ложных посылок информации.

Для этого в предлагаемом устройстве блок воспроизведения выполнен с дополнительной схемой «И, включенной между формнрователем и выходным каскадом и связанной другим входом с иоследовательно соединенными времязадающей схемой и цепью -запуска.

Кроме того, времязадающая схема выполнена на двух разнополярных транзисторах, база одного из которых проводимости р-п-р подключена к коллектору дугого транзистора проводимости п-р-п через последовательно соединенные резистор и конденсатор, общей точкой связанных с конденсатором це-пи запуска, подключенного к общей щцне схемы и блока воспроизведения, причем с этой же щиной через полный резистивный делитель соединб) коллектор первого из транзисторов, а через часть его-база второго.

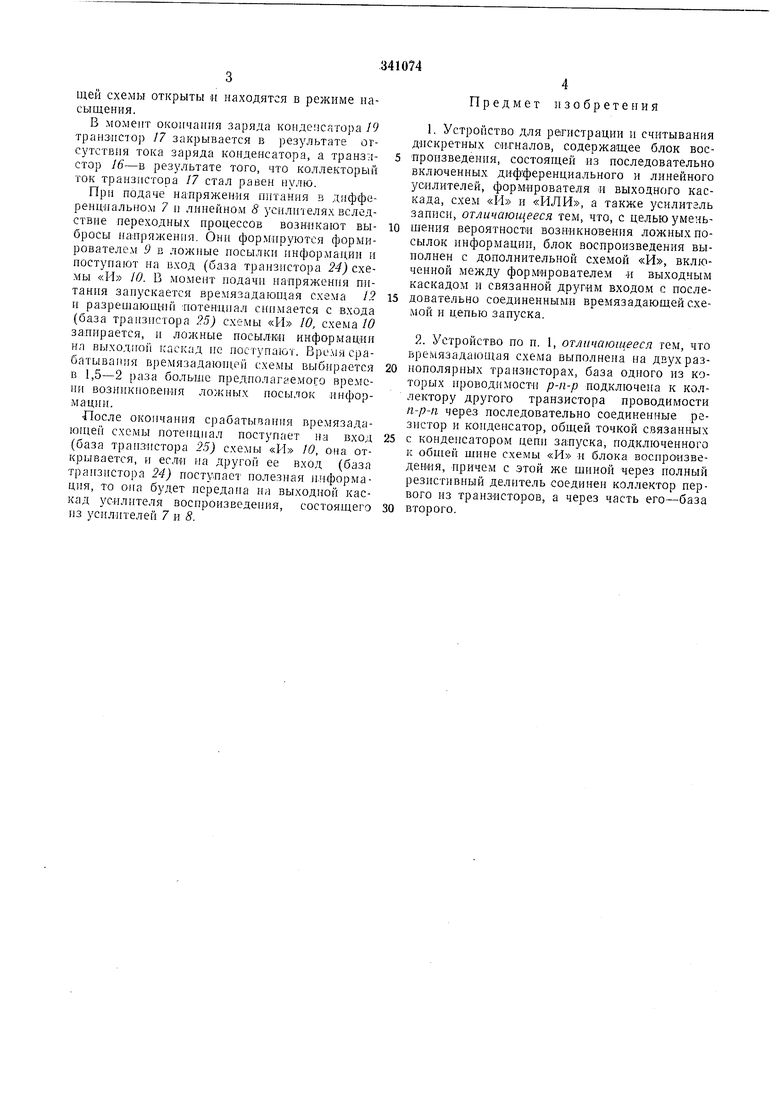

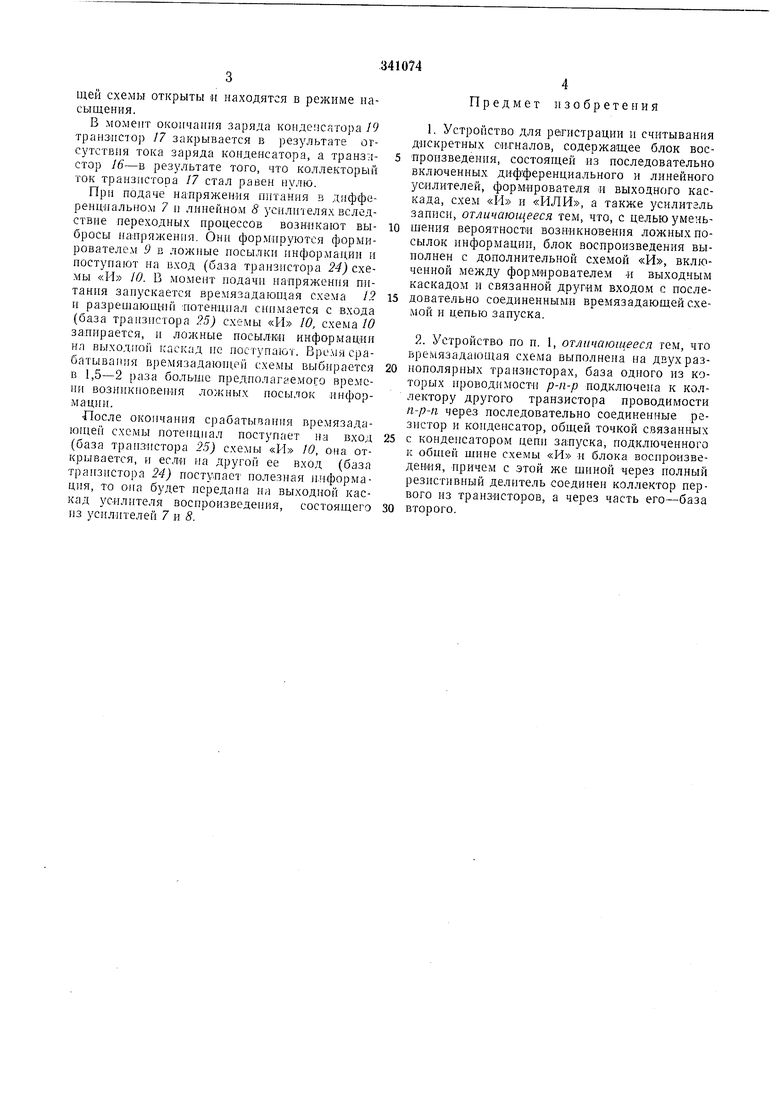

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2-электрическая

схема узлов схемы «И, времязадающей схемы и запускаюн1,ей цеин.

Устройство содержит леитоиротяжный механизм }, электропривод 2, магнитную головку 5, усилитель 4 записи, схемы «И 5 и 6,

дифференциальный усилитель 7, линейный усилитель 8, формирователь 9 воспроизведенной дискретной информации, схему «И 10, выходной каскад И, времязадающую схему 12, запускающую цепь 13, включатель 14 нанряжения питания, схему «ИЛИ 15.

Времязадающая схема 12 состоит из двух транзисторов 16 и 17, резистора 18, конденсатора 19 и резистора 20. В установивщемся ренсиме оба транзистора

закрыты, а конденсатор 19 разряжен через параллельно подключенные к нему резисторы 21 и 22.

В момент подачи напряжения нитания ироисходит заряд конденсатора 23. Ток конденситора, протекая через базовый переход транзистора 17, открывает его. Коллекторый ток транзистора 7 через резистор /S-поступает на базу транзистора 16 и открывает его. При этом начинается заряд конденсатора 19, во

щей схемы открыты и находятся в режиме насыщения.

В момент окончания заряда кондепсатора 19 транзистор /7 закрывается в результате отсутствия тока заряда конденсатора, а траизлстор 16-в результате того, что коллекторый ток транзистора 17 стал равен нулю.

При подаче напряжения питания в дифференциально.1 7 н линейном 8 усилителях вследствие переходных ироцессов возникают выбросы шшряжеиия. Они формируются формирователем 9 и ложиые посылки информации и иоступают на вход (база траизистора 24) схемы «И 10. В момент иодачи напряження питания заиускается времязадающая схема 12 и разрешающей лотенциал сипмается с входа (база транзистора 25) схемы «И 10, схема 10 забирается, и ложные иосылк« информации на выходно каскад ие поступают. Время срабатыва1)1я времязадаюиип схемы выбирается в 1,5-2 раза больше иредполагаемого вре.мсни возникновеиия ложных иосылок информации.

Лосле окопчаиия срабатывания времязадаюгцей схемы поте1щиал иоступает на вход (база траизистора 25) схемы «Pi 10, она открывается, и если на другой ее вход (база траизистора 24) поступает полезная и.иформация, то oira будет иередаиа на выходной каскад усилителя воспроизведения, состоящего из усилителей 7 и 8.

Предмет изобретепия

1. Устройство для регистрации и считывания дискретиых сигналов, содержащее блок воспроизведения, состоящей из последовательно включенных дифференциального и линейного усилителей, формирователя и выходного каскада, схем «И и «ИЛИ, а также усилитгль заииси, отличающееся тем, что, с целью уменьшения вероятности возникновения ложных посылок информации, блок восироизведения выполнен с дополнительной схемой «И, включенной между формирователем « выходным каскадом и связанной другим входом с последовательно соединенными времязадающей схемой и цепью запуска.

2. Устройство по п. 1, отлччаюги-веся тем, что времязадающая схема выполнена на двухразноиолярных транзисторах, база одного из которых проводимости р-п-р подключена к коллектору другого транзистора проводимости п-р-п через последовательно соединенные резистор и конденсатор, общей точкой связанных

с конденсатором ценн запуска, подключенного к обшей шине схемы «И и блока воспроизведения, причем с этой же шиной через иолный резистивиый делитель соединеи коллектор первого из транзисторов, а через часть его-база

второго.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1973 |

|

SU393804A1 |

| Импульсный стабилизатор напряжения | 1978 |

|

SU752297A1 |

| ГРОМКОГОВОРЯЩЕЕ ДУПЛЕКСНОЕ УСТРОЙСТВО | 1970 |

|

SU259162A1 |

| Многофазное реле минимального и максимального напряжения | 1980 |

|

SU904069A1 |

| ОДНОВИБРАТОР | 1972 |

|

SU345598A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-СЧИТЫВАНИЯ | 1972 |

|

SU345517A1 |

| ЖДУЩИЙ МУЛЬТИВИБРАТОР | 1973 |

|

SU364078A1 |

| ПЬЕЗОТРАНСФОРМАТОРНОЕ ЗАПОЛИШАЮЩЕЕ УСТРОЙМТ?|11е0-1ЕЛКГ1:: | 1972 |

|

SU331421A1 |

| Стабилизированный источник питания | 1979 |

|

SU836630A1 |

| ЖДУЩИЙ МУЛЬТИВИБРАТОРВПТБшл тттп | 1972 |

|

SU425322A1 |

to

Авторы

Даты

1972-01-01—Публикация