Изобретение относится к области вычислительной техники.

Известны устройства на биполярных транзисторах, например, разрядный формирователь, предназначенный для заниси информации в накопитель, усилитель считывания, предназначенный для воспроизведения сигнала, считанного с накопителя.

Особенности ввода - вывода информации у накопителя на МОП-структурах определяют разрядный формирователь и усилитель считывания как самостоятельные, раздельные устройства. Запись информации в элемент памяти (триггер накопителя на МОП-структурах) осуществляется подачей сигнала с разрядного формирователя по разрядной шине на сток МОП-транзистора плеча триггера, а считывание происходит по стоку того же МОПтранзистора. В качестве разрядного формирователя применяется схема эмиттерных повторителей на транзисторах п-р-п и р-п-р типов проводимостей, нагрузкой которых является межэлектродная емкость МОП-транзистора триггера - элемента памяти накопителя.

Наиболее распространенным устройством для считывания информации для накопителей на МОП-структурах является дифференциальный усилитель.

большое количество элементов; относительно большую величину потребляемой мошностн в статнческом режиме; два источника напряжения; необходимость дополнительных согласующих устройств для стыковки со следующим логическим модулем нз заданного класса; относительно больщое время задержки сигнала.

В предлагаемом устройстве совмещены функции записи и считывания;

потребляемая мощность в статнческом режиме но сравнению с существующими раздельными устройствами значительно ниже;

уменьшено суммарное число нснользуемых источников наиряження для обонх устройств; уменьшено число иснользуемых электроэлементов в блоке считывания нового устройства;

не требуется согласующего устройства блока считывания с последующим логическим элементом из заданного класса.

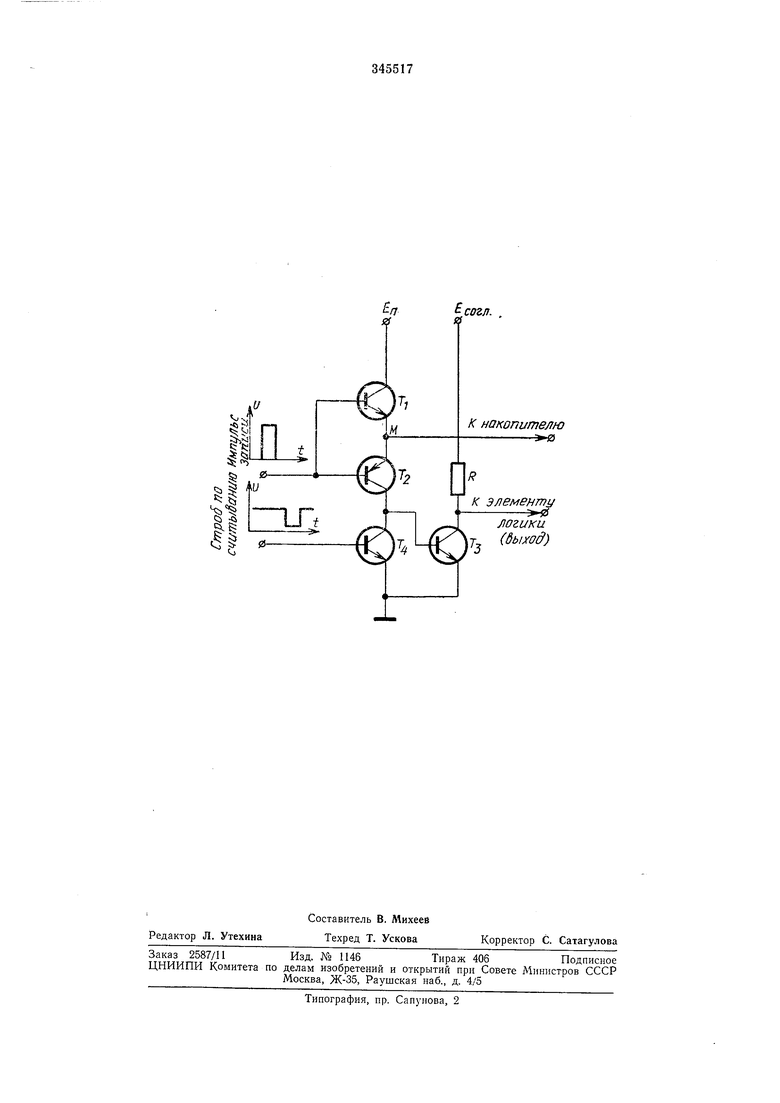

На чертеже представлена нрннцппнальная электрнческая схема устройства для запнсисчнтывания.

Схема содержнт 4 транзнстора н 1 резнстор. Транзисторы Ti(n-p-n) и Тг(р-п-р), выполняющие функцию заниси, объединены базами в общую точку. Коллектор транзнстора TI находится под потенциалом „ источника напряжения. Эмиттер транзнстора Т объедннен с эмиттером транзистора Т, общая точка транзисторов М соединена с разрядной шиной накопителя. Между стоком плеча триггера накопителя и разрядной шиной включен ключевой МОП-транзистор (на чертеже не показан, поскольку он входит как составной элемент в матрицу памяти на МОП-транзнсторах). Транзисторы Гз и Г/ п-р-п проводимости, выполняюш;ие функцнн воспроизведения и выделения считанного сигнала, соединены эмиттерами в общую , находящуюся под потенциалом общей шины источника напряжения. Коллектор транзистора TZ соединен с коллектором транзистора Т/ и базой транзистора Гз, в коллекторной цепи которого включен резистор R. Коллектор транзистора 7з находится под потенциалом согл. согласующего источника напряжения.

Устройство работает следующим образом.

Источник напряжения Ясогл., нитающнй транзистор Гз, выполняет функцию согласования по сигналу выхода блока считывания с последующим логическим элемеитом. Источник напряжения Ец является общим для накопителя и для устройства записи - считывания. За счет того, что на базы транзисторов Г1 и Гз в исходном режиме подается соответствующий уровень напряжения, транзистор TI находится в закрытом состоянии, а транзистор TZ-- в открытом.

Элемент памяти накопителя (триггер) имеет в исходном состоянии закрытый ключевой МОИ-транзистор, включенный между стоком плеча триггера накопителя и разрядной шиной, соединенной с эмиттерами транзисторов Т, и Гг.

Таким образом, в исходном состоянии через транзистор Гг не протекает ток ни по цепи транзистора Г ни по цепи электроэлементов триггера наконителя, т. е. нотребление мощности в статическом режиме почти отсутствует. Поскольку открытый транзистор Г/ включен последовательно с транзистором Гг, то и он не потребляет мощности в статическом режиме. При этом транзистор Гз закрыт, так как через его база - эмиттерный переход в статическом режиме не нротекает ток. В режиме записи информационной единицы в иаконитель на базы т анзисторов Т и Гг подается импульс записи. В результате транзистор Гг закрывается, а транзистор Т открывается. Через открытый транзистор Гь открытый ключевой МОП-транзистор и электроэлементы триггера накопителя течет ток записи, приводящий триггер в состояиие, противоположное нсходиому (нулевому)..

В режиме счнтываЕп-ш ключевой МОП-транзнстор также . Транзисторы TI и TZ находятся в исходном состоянин. На базу транзистора r/i подается строб, который совпадает по времени с сигналом, открывающим ключевой МОП-транзистор в разрядиой щиие, и

закрывает транзистор Ti.

Считанный ток протекает по цени: шина источника напряжения „, открытый МОПтранзистор плеча триггера накопителя, открытый ключевой МОП-транзистор, открытый

транзистор Гг, база - эмиттерный нереход транзистора Гз, шина источников напряжения. Ток, протекающий по база-эмиттериому переходу траизистора Гз, усиливается и с его коллектора подается на вход последующего

логического элемента. Поскольку считанный сигнал проходит через два транзистора TZ и Гз, задержка сигнала определяется только ими, тогда как в дифференциальном усилителе время задержки определялось большим

числом аиалогичных транзисторов.

ГI р е д м е т изобретения

Устройство для записи-считывания, содержащее два носледовательио соединенных траизистора записи, коллектор первого из которых соединен с зажимом питания, а его эмиттер - с эмиттером второго транзистора, отличающееся тем,. что, с целью совмещения в одном блоке функций записи и считывания и уменьшения оборудоваиия, устройство дополнительно содержнт два транзистора, один из которых базой подключен к коллектору второго транзистора записи и коллектором через резистор к зажиму согласующего источника иапряжеиия, а другой включен параллельно нсрвому и соединен коллектором с коллектором второго транзистора записи.

согл. s}

К накопителю

к элемент,

1

логики J (дыход)

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕКЛЮЧЕНИЯ ЗНАКОПЕРЕМЕННЫХ АНАЛОГОВЫХ СИГНАЛОВ | 1973 |

|

SU385287A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU343308A1 |

| РАЗРЯДНЫЙ ФОРМИРОВАТЕЛЬ | 1972 |

|

SU327586A1 |

| КЛЮЧ ПЕРЕМЕННОГО ТОКА | 1973 |

|

SU371685A1 |

| Авторегулируемый формирователь напряжения записи для электрически программируемых постоянных запоминающих устройств на КМОП-транзисторах | 1988 |

|

SU1631606A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ НА МОП-ТРАНЗИСТОРАХ | 1972 |

|

SU358722A1 |

| РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ ДЛЯ УПРАВЛЕНИЯ ЭЛЕКТРИЧЕСКИМ ШАГОВЫМ ДВИГАТЕЛЕМ | 1965 |

|

SU176000A1 |

| БАЛАНСНАЯ СХЕМА СРАВНЕНИЯ! | 1970 |

|

SU267209A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ ДЛЯ НАКОПИТЕЛЯ НА МДП-СТРУКТУРАХ | 1972 |

|

SU425331A1 |

Даты

1972-01-01—Публикация