Известны устройства для приема одиночных команд, содержащие приемник двоичных сигналов, блоки декодирования и исполнения, детектор качества, регистр сдвига, пороговый элемент. Такие устройства не обладают требуемой помехозащищенностью от ложного приема команд.

Целью изобретения является уменьшение вероятности ложного приема команд. Это достигается тем, что в устройство введены дополнительный резисторный сумматор и клапан, включенный между блоком декодирования и исполнительным блоком. При этом к управляющему входу клапана подключен выход порогового элемента, ко входу которого подключен выход резисторного сумматора, присоединенного входами к регистру сдвига, а ко входу регистра сдвига нодключен выход детектора качества.

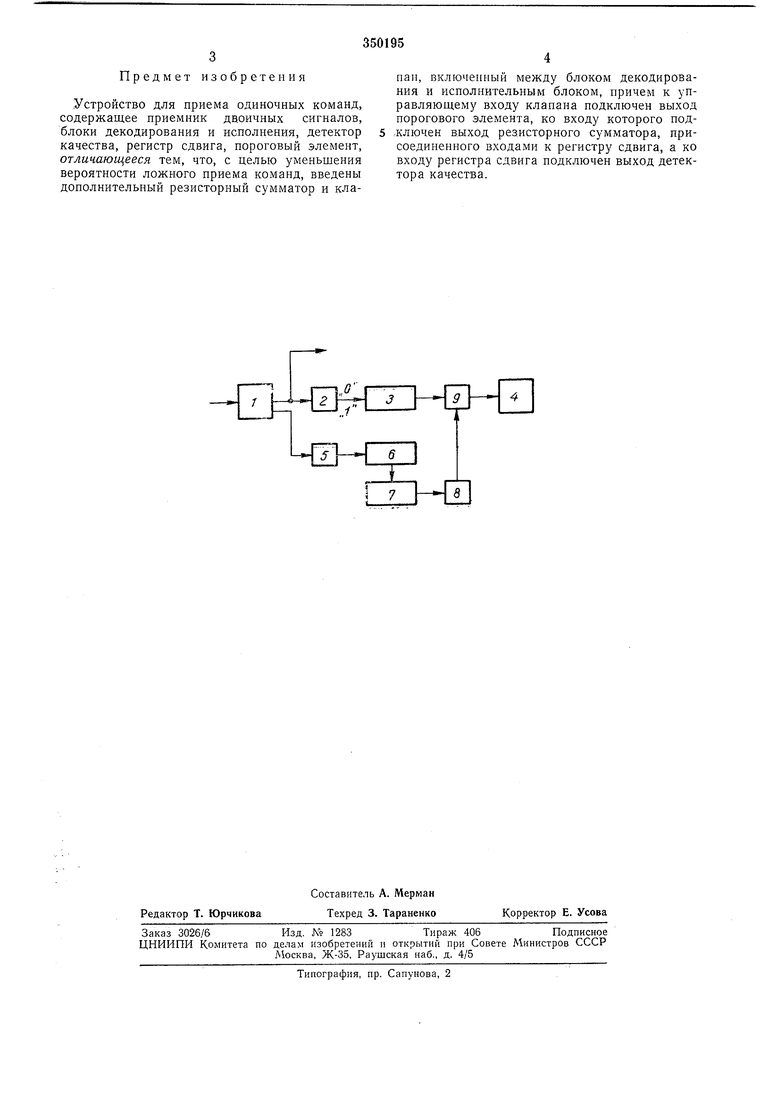

Па чертеже приведена блок-схема предлагаемого устройства.

Устройство содержит приемник / двоичных сигналов, схему 2 регистрации двоичных символов, блок 3 декодирования, исполнительный блок 4, детектор 5 качества, регистр 6 сдвига, резисторный сумматор 7, пороговый элемент 8 и клапан 9.

ющий регистр 6 сдвига только в тех случаях, когда двоичные сигналы принимаются неуверенно. Продвижение числа «1 в регистре осуществляется с частотой телеграфирования.

Длина регистра (число ячеек) равна или меньще длины кодограммы N (исключая точки, предназначенные для вхождения приемного устройства в тактовую синхронизацию). Таким образом, число «1, записанное в

ячейках регистра, всегда равно числу сигналов стираний, зафиксированных в принимаемой кодовой последовательности на отрезке в .V двоичных разрядов, предществующих последнему разряду.

Потенциальные выходы всех N ячеек регистра параллельно подключены на Л входов сумматора 7. С каждым тактом продвижения число импульсов, подаваемых на сумматор 7, равно числу «1 в регистре. При этом на выходе сумматора 7 формируется импульс, амплитуда которого пропорциональна числу «1 в регистре или, что то же, числу стираний на длине N двоичных разрядах. Этот импульс подается на пороговый элемент 8 и, если его

амплитуда превышает установленный порог, на клапан 9 выдается калиброванный импульс, закрывающий клапан на время одного такта. Если в этот такт с блока 3 декодирования выдается команда, то она на исполнительный

Предмет изобретения

Устройство для приема одиночных команд, содержащее приемник двоичных сигналов, блоки декодирования и исполнения, детектор качества, регистр сдвига, пороговый элемент, отличающееся тем, что, с целью уменьшения вероятности ложного приема команд, введены дополнительный резисторный сумматор и кланаи, включенный между блоком декодирования и исполнительным блоком, причем к управляющему входу клапана подключен выход порогового элемента, ко входу которого под5 .ключей вь1ход резисторного сумматора, присоединенного входами к регистру сдвига, а ко входу регистра сдвига подключен выход детектора качества.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для корреляционного приема дискретной информации | 1977 |

|

SU661839A1 |

| Устройство для приема одиночных команд | 1986 |

|

SU1350840A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1981 |

|

SU1840033A1 |

| Устройство для измерения отношения "сигнал-шум" канала связи | 1978 |

|

SU786020A1 |

| Устройство для приема избыточной информации | 1989 |

|

SU1786498A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Способ и устройство обработки ФТ сигнала с дискретной подстройкой фазы в экономичном режиме | 2019 |

|

RU2729042C1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКИХ КОДОВ, ИСПРАВЛЯЮЩИХ МНОГОКРАТНЫЕ ПАЧКИ ОШИБОК | 1967 |

|

SU200894A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

ГП-

Даты

1972-01-01—Публикация