Изобретение относится к технике передачи данных и может использоваться в системах с решающей обратной связью для приема информации, закодированной циклическим кодом, допускающим мажоритарную процедуру декодирования.

Для многоканальной аппаратуры с временным объединением (разделением) цифровых каналов связи и асинхронным вводом и выводом информации с различными линейными скоростями передачи сигналов очень важным является реализация в ней декодирующего устройства, которое обеспечивало бы защиту от ошибок при передаче информации с переменными параметрами и исправление многократных ошибок. При этом коэффициент ошибок Кош в трактах связи может достигать значений от 10-5 до

10-2. Причем значения Кош характеризуются как быстрыми, так и медленными изменениями. Для канала связи с медленными изменениями для защиты от ошибок целесообразно использовать адаптивное декодирование.

Одним из путей защиты является использование декодеров с обнаружением и исправлением ошибок при помощи корректирующих циклических кодов, допускающих мажоритарную процедуру декодирования [1, 2].

Из известных декодеров наиболее близким по технической сущности к предлагаемому изобретению является декодер с обнаружением и исправлением ошибок, описанный в [3].

Известный декодер с обнаружением и исправлением ошибок содержит последовательно соединенные первый элемент ИЛИ, регистр сдвига, первый ключ и вычислитель синдрома, а также сумматор по модулю два, счетчик сдвигов, счетчик исправлений, второй, третий, четвертый, пятый, шестой и седьмой ключи, при этом выходы регистра сдвига через сумматоры подключены к входам мажоритарного элемента, выход которого через второй ключ подсоединен к сигнальному входу третьего ключа, к управляющему входу которого и управляющим входам первого и четвертого ключей подсоединен первый выход счетчика сдвигов, второй и третий выходы которого подключены соответственно к управляющим входам пятого и шестого ключей, причем выход первого ключа соединен с сигнальным входом пятого ключа [3].

Однако известный декодер имеет недостаточную помехоустойчивость и точность декодирования.

Целью изобретения является повышение вероятности приема неискаженной кодовой комбинации и точности декодирования при работе по каналам связи с низким качеством, а также повышение помехоустойчивости работы устройства.

Поставленная цель достигается тем, что адаптивный декодер, содержащий последовательно соединенные первый элемент ИЛИ и регистр сдвига, первая группа выходов которого соединена со входами первого блока сумматоров по модулю два, выходы которого соединены со входами первого мажоритарного элемента, а также содержащий первый, второй, третий, четвертый, пятый, шестой и седьмой ключи, отличается тем, что в него введены демультиплексор, последовательно соединенные декодер первого типа кода и анализатор синдрома первого типа кода, последовательно соединенные декодер второго типа кода и анализатор синдрома второго типа кода, последовательно соединенные декодер третьего типа кода и анализатор синдрома третьего типа кода, блок управления режимами работы декодеров, счетчик стираний, второй элемент ИЛИ, восьмой и девятый ключи, анализатор качества канала связи (АККС), распределитель адаптивного декодера, блок элементов памяти и декодер качества канала (ДКК), при этом первый, второй и третий выходы демультиплексора подключены ко входам соответственно первого, второго и третьего ключей, а выходы первого, второго и третьего ключей подключены ко входам декодера первого типа кода, декодера второго типа кода и декодера третьего типа кода, первый, второй, третий и четвертый управляющие выходы блока управления режимами работы декодеров подключены соответственно к управляющим входам демультиплексора, первого, второго и третьего ключей, причем выходы первого, второго и третьего ключей подключены соответственно к первому, второму и третьему входам первого элемента ИЛИ, выход анализатора синдрома второго типа кода соединен с первым входом четвертого ключа, второй вход которого соединен с первым выходом счетчика стираний, второй выход которого соединен с первым входом пятого ключа, второй вход которого соединен с выходом анализатора синдрома третьего типа кода, выход анализатора синдрома первого типа кода соединен со входом шестого ключа, выходы четвертого, пятого и шестого ключей подключены соответственно к первому, второму и третьему входам второго элемента ИЛИ, выход первого мажоритарного элемента соединен со входом седьмого ключа, вторая группа выходов регистра сдвига подключена ко входам второго блока сумматоров по модулю два, выходы которого соединены со входами второго мажоритарного элемента, выход которого соединен со входом девятого ключа, выход регистра сдвига соединен со входом восьмого ключа, выходы седьмого, восьмого и девятого ключей подключены соответственно к первому, второму и третьему входам блока элементов памяти, выход которого соединен с приемником информации, первый выход АККС соединен с первым управляющим входом блока управления режимами работы декодеров, с управляющими входами шестого и восьмого ключей и с первым управляющим входом распределителя адаптивного декодера, второй выход АККС соединен со вторым управляющим входом блока управления режимами работы декодеров, с управляющими входами четвертого и девятого ключей и со вторым управляющим входом распределителя адаптивного декодера, третий выход АККС соединен с третьим управляющим входом блока управления режимами работы декодеров, с управляющими входами пятого и седьмого ключей и с третьим управляющим входом распределителя адаптивного декодера, первый и второй выходы ДКК подключены ко входам соответственно счетчика стираний и АККС, выход второго элемента ИЛИ соединен с управляющим входом блока элементов памяти, а первый, второй и третий выходы распределителя адаптивного декодера подключены к управляющим входам соответственно декодера первого типа кода, декодера второго типа кода и декодера третьего типа кода, при этом вход демультиплексора является входом адаптивного декодера, выходом которого является выход блока элементов памяти.

Сопоставительный анализ с прототипом показывает, что предлагаемый адаптивный декодер отличается наличием новых блоков: демультиплексора, декодера первого типа кода и анализатора синдрома первого типа кода, декодера второго типа кода и анализатора синдрома второго типа кода, декодера третьего типа кода и анализатора синдрома третьего типа кода, блока управления режимами работы декодеров, счетчика стираний, второго элемента ИЛИ, восьмого и девятого ключей, АККС, распределителя адаптивного декодера, блока элементов памяти и ДКК, а также изменением связей с остальными элементами схемы декодера, что способствовало повышению на 10-20 процентов по сравнению с прототипом помехоустойчивости работы декодера за счет обнаружения и исправления ошибок в принимаемой информации и обеспечения работы по каналам связи с тремя уровнями их качества (для пороговых значений ошибок Wп≤10-4, Wп≤5·10-3, Wп≤5·10-2).

Таким образом, заявляемый адаптивный декодер соответствует критерию изобретения "новизна". Сравнение заявляемого решения с другими техническими решениями показывает, что вновь введенные в предлагаемый адаптивный декодер элементы реализуемы, хорошо известны специалистам в данной области техники и дополнительного творчества, учитывая приведенные ниже пояснения, для их воспроизведения не требуется.

Данное решение существенно отличается от известных решений в данной области техники. Заявляемое решение явным образом не следует из уровня техники и имеет изобретательский уровень.

Это позволяет сделать вывод о соответствии технического решения критерию "существенные отличия".

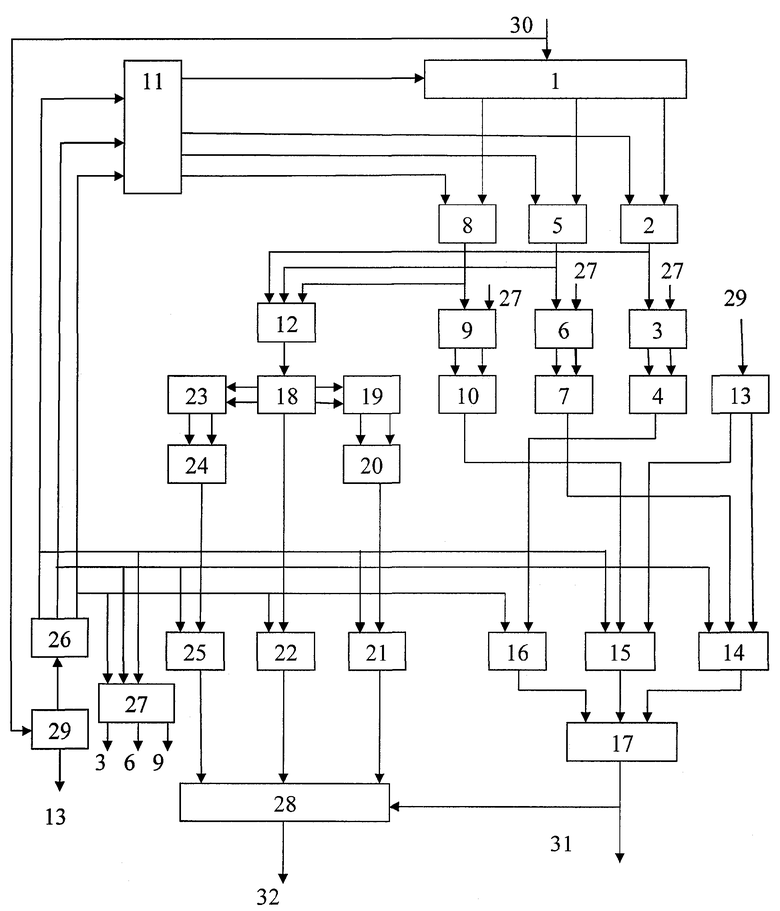

На чертеже представлена структурная электрическая схема адаптивного декодера.

Адаптивный декодер содержит демультиплексор 1, первый 2 ключ, декодер 3 первого типа кода, анализатор 4 синдрома первого типа кода, второй 5 ключ, декодер 6 второго типа кода, анализатор 7 синдрома второго типа кода, третий 8 ключ, декодер 9 третьего типа кода, анализатор 10 синдрома третьего типа кода, блок 11 управления режимами работы декодеров, первый 12 элемент ИЛИ, счетчик 13 стираний, четвертый 14 ключ, пятый 15 ключ, шестой 16 ключ, второй 17 элемент ИЛИ, регистр 18 сдвига, первый 19 блок сумматоров по модулю два, первый 20 блок мажоритарных элементов, седьмой 21 ключ, восьмой 22 ключ, второй 23 блок сумматоров по модулю два, второй 24 блок мажоритарных элементов, девятый 25 ключ, АККС 26, распределитель 27 адаптивного декодера, блок 28 элементов памяти, ДКК 29, вход 30 информации из канала связи, выход 31 сигнала «ошибка» и выход 32 к приемнику информации.

Первый, второй и третий выходы демультиплексора 1 подключены соответственно ко входам первого 2, второго 5 и третьего 8 ключей, а выходы первого 2, второго 5 и третьего 8 ключей подключены соответственно к первому, второму и третьему входам первого 12 элемента ИЛИ. Выход первого 2 ключа соединен со входом декодера 3 первого типа кода, выходы которого соединены со входами анализатора 4 синдрома первого типа кода, выход второго 5 ключа соединен со входом декодера 6 второго типа кода, выходы которого соединены со входами анализатора 7 синдрома второго типа кода, а выход третьего 8 ключа соединен со входом декодера 9 третьего типа кода, выходы которого соединены со входами анализатора 10 синдрома третьего типа кода.

Первый, второй, третий и четвертый управляющие выходы блока управления 11 режимами работы декодеров подключены соответственно к управляющим входам демультиплексора 1, первого 2, второго 5 и третьего 8 ключей. Выход анализатора 7 синдрома второго типа кода соединен с первым входом четвертого ключа 14, второй вход которого соединен с первым выходом счетчика 13 стираний, второй выход которого соединен с первым входом пятого ключа 15, второй вход которого соединен с выходом анализатора 10 синдрома третьего типа кода, выход анализатора 4 синдрома первого типа кода соединен со входом шестого ключа 16, а выходы четвертого 14, пятого 15 и шестого 16 ключей подключены соответственно к первому, второму и третьему входам второго 17 элемента ИЛИ.

Выход первого 20 мажоритарного элемента соединен со входом седьмого 21 ключа, вторая группа выходов регистра 18 сдвига подключена ко входам второго блока 23 сумматоров по модулю два, выходы которого соединены со входами второго 24 мажоритарного элемента, выход которого соединен со входом девятого 25 ключа, а выход регистра 18 сдвига соединен со входом восьмого 22 ключа. Выходы седьмого 21, восьмого 22 и девятого 25 ключей подключены соответственно к первому, второму и третьему входам блока 28 элементов памяти, выход которого соединен с приемником 32 информации. Первый выход АККС 26 соединен с первым управляющим входом блока 11 управления режимами работы декодеров, с управляющими входами шестого 16 и восьмого 22 ключей и с первым управляющим входом распределителя 27 адаптивного декодера, второй выход АККС 26 соединен со вторым управляющим входом блока управления 11 режимами работы декодеров, с управляющими входами четвертого 14 и девятого 25 ключей и со вторым управляющим входом распределителя 27 адаптивного декодера, третий выход АККС 26 соединен с третьим управляющим входом блока управления 11 режимами работы декодеров, с управляющими входами пятого 15 и седьмого 21 ключей и с третьим управляющим входом распределителя 27 адаптивного декодера. Первый и второй выходы ДКК 29 подключены ко входам соответственно счетчика 13 стираний и АККС 26, выход второго 17 элемента ИЛИ соединен с управляющим входом блока 28 элементов памяти, а первый, второй и третий выходы распределителя 27 адаптивного декодера подключены к управляющим входам соответственно декодера 3 первого типа кода, декодера 6 второго типа кода и декодера 9 третьего типа кода, при этом вход демультиплексора 1 является входом адаптивного декодера, выходом которого является выход блока 28 элементов памяти.

Демультиплексор 1 совместно с первым 2, вторым 5 и третьим 8 ключами предназначен для ввода информации из канала связи. Ключи 2, 5 и 8 выполняют роль коммутационных элементов, подключающих принятую информацию из канала связи на вход соответствующего декодера 3, 6 и 9. Они могут быть выполнены на основе схем «И».

Декодер 3 первого типа кода предназначен для декодирования поступающих из канала связи кодовых комбинаций кода типа (31, 25, 4).

Декодер 6 второго типа кода предназначен для декодирования поступающих из канала связи кодовых комбинаций кода типа (31, 15, 6).

Декодер 9 третьего типа предназначен для декодирования поступающих из канала связи кодовых комбинаций кода типа (31, 5, 16).

Декодеры содержат делитель принимаемой кодовой комбинации длины n (n, k) кода на образующий полином g(x) циклического кода. При этом если ошибок на длине кодовой комбинации нет в результате ее деления на образующий полином или ошибка не обнаружена (n, k) кодом, то значение синдрома равно нулю.

Работа указанных декодеров основана на оценке состояния канала связи по значению коэффициента ошибок Кош и выборе кодов, обеспечивающих обнаружение и исправление ошибок мажоритарным способом. При этом для канала связи с Кош=10-4÷10-5 выбран код (31, 25, 4), имеющий отношение выбранного кратного к числа ошибок в канале связи к длине n (n=31) кодовой комбинации k/n=0,8. Для канала связи с коэффициентом Кош=5·10-3÷10-4 использован код (31, 15, 6), имеющий отношение k/n=0,48, а для канала связи с Кош=10-3÷5·10-2 выбран код (31, 5, 16) с k/n=0,16.

Анализаторы 4, 7 и 10 синдрома (n, k) кода предназначены для анализа информации, поступающей из канала связи, вычисления синдрома для каждого типа кода и выработки сигнала «ошибка», с помощью которого осуществляется стирание искаженной кодовой комбинации.

Блок 11 управления режимами работы декодеров предназначен для управления демультиплексором 1 и первыми тремя ключами (2, 5 и 8) в процессе приема информации из канала связи.

Счетчик 13 стираний определяет порог ошибок, поступающих из канала связи, и управляет выводом информации к потребителю через коммутационные элементы - ключи 14 и 15.

Регистр 18 сдвига, первый 19 и второй 23 блоки сумматоров по модулю два, первый 20 и второй 24 мажоритарные элементы совместно с шестым 16, седьмым 21, восьмым 22 и девятым 25 ключами выполняют функции устройства исправления ошибок мажоритарным способом.

АККС 26 предназначен для определения пороговых значений коэффициента ошибок Кош на интервале времени Т путем подсчета количества ошибок и выработки управляющих сигналов для коммутационных элементов (ключей), блока 11 управления режимами работы и распределителя 27 адаптивного декодера.

Блок 28 элементов памяти содержит элементы памяти на 5, 15 и 25 разрядов для хранения в них информации о кодовых комбинациях и выдачи их потребителю. Блок 28 элементов памяти выполняет функции элемента задержки m принимаемых кодовых комбинаций на время анализа качества канала связи на интервале m кодовых комбинаций, что способствует исключению возможности выдачи потребителю искаженной комбинации в период анализа состояния канала связи.

Адаптивный декодер работает следующим образом.

Оптимальное сопряжение декодера с источником и приемником информации является одним из основных требований, обеспечивающих простоту реализации. Для последующего анализа возьмем циклические коды с длиной кодовой комбинации n=31, допускающих мажоритарную процедуру декодирования. При этом для канала связи с Кош=10-4÷10-5 возьмем код (31, 25, 4), а для канала связи с Кош=5·10-3÷10-4 код (31, 15, 6) и для канала связи с Кош=10-3÷5·10-2 код (31, 5, 16).

В процессе работы декодера АККС 26 на интервале времени Т определяет пороговые значения коэффициента ошибок (Wп≤10-4, Wп≤10-3, Wп<5·10-2) и, в зависимости от фиксированного значения порога, выдает сигнал блоку 11 управления режимами работы декодера, который, в свою очередь, выдает сигналы на коммутационные элементы - соответствующие ключи, подключающие соответствующий декодер (3, 6 или 9). Одновременно блок 11 управления режимами работы декодера выдает сигнал на распределитель 27 адаптивного декодера и демультиплексор 1.

При поступлении от ДКК 29 принятой из канала связи 30 информации о потоке ошибок, АККС 26 подсчитывает количество ошибок на длине Т и, если порог не превышает величину Wп≤10-4, то посредством элементов коммутации (ключей) подключается декодер первого типа кода (31, 25, 4).

Далее 31-элементная кодовая комбинация из канала связи поступает на вход демультиплексора 1 и коммутируется на один из трех его выходов. Затем через открытый сигналом с блока 11 управления первый ключ 2 кодовая комбинация поступает на вход анализатора 4 синдрома первого типа кода (31, 25, 4). В течение тридцати одного такта происходит вычисление синдрома при делении 31-элементной комбинации на полином g(x)=х6+х5+х3+х2+х+1. Если при этом анализатор 4 синдрома зафиксировал нулевой остаток [S(x)=0], то 25-элементная комбинация (k=25), которая одновременно записывалась в регистр 18 сдвига через первый 12 элемент «ИЛИ», считывается с выхода регистра 18 сдвига через открытый ключ 22 в блок 28 элементов памяти. Так как S(x)=0, то сигнал «ошибка» не вырабатывается и из блока 28 информационная последовательность (k=25) считывается в приемник 32 информации.

Если S(x)≠0, то анализатор 4 синдрома вырабатывает сигнал «ошибка» (31), который стирает искаженную 25-элементную комбинацию из блока 28 элементов памяти. Для обработки информации (31, 25, 4) кодом адаптивного декодера с помощью сигнала Wп≤10-4, выдаваемого с АККС 26, распределитель 27 вырабатывает необходимые временные подставки.

Если коэффициент ошибок Кош в канале связи достигает порогового значения Wп≤5·10-3, то аналогичным образом подключается анализатор 7 синдрома второго типа кода (31, 15, 6) и устройство исправления ошибок, реализованное на регистре 18 сдвига, сумматорах по модулю два (блок 19) и мажоритарном элементе 20 на восемь входов.

Если счетчик ошибок на длине п=31 зафиксировал порог wп≤2, то после деления на полином g(x)=x16+x15+x12+x7+x6+x5+x4+1 кода (31, 15, 6) в течение 31 такта фиксируется отсутствие ошибок (S(x)=0) и, одновременно, после заполнения регистра 18 сдвига осуществляется исправление ошибок в течение 31 такта при включении обратной связи. Только после этой процедуры кодовая комбинация (k=15) записывается в блок 28 элементов памяти и выдается сигнал, разрешающий ее передачу приемнику 32 информации. Если число ошибок не превысило двух, то исправленная кодовая комбинация после деления ее на полином, независимо от (S(x)≠0), выдается через блок 28 элементов памяти потребителю (приемнику 32 информации).

При работе адаптивного декодера кода (31, 15, 6) в режиме, когда величины

Wп≤5·10-3, wп≥2 и S(x)≠0, выдается сигнал 31 ошибка, который не разрешает выдачу комбинаций потребителю (приемнику 32 информации) и формируется сигнал «стирание» последней.

Аналогичным образом при Wп≤5·10-2 подключается декодер 9 третьего типа кода (31, 5, 16), состоящий из анализатора 10 синдрома, регистра 18 сдвига на 31 разряд с сумматорами по модулю два (блок 23) и мажоритарного элемента 24 на 16 входов. При этом, если при Wп≤5·10-2, wп≤5 и S(x)≠0, то сигнал ошибка не вырабатывается и кодовая комбинация считывается из блока 28 потребителю, а если

Wп≤5·10-2, wп>5 и S(x)≠0, то вырабатывается сигнал ошибка, стирающий искаженную кодовую комбинацию.

Рассмотрим подробнее алгоритм работы адаптивного декодера кода (31, 5, 16).

Кодовая комбинация кода (31, 5, 16) поступает из канала связи на вход демультиплексора 1 и через элементы коммутации - третий ключ 8 на вход анализатора 10 синдрома третьего типа и одновременно на вход регистра 18 сдвига. При этом 31-элементная кодовая комбинация в течение 31 такта записывается в анализатор 10 синдрома. При записи (сдвигах) осуществляется деление 31-элементной комбинации на образующий полином

g(x)=х26+х24+х22+х21+х20+х18+х17+х13+х12+х11+х10+х9+х6+х5+х3+1, в результате которого получается синдром S(x), имеющий значение нуль при отсутствии ошибок в 31-элементной комбинации и не равен нулю в случае наличия хотя бы одной ошибки в указанной комбинации.

При отсутствии ошибок анализатор 10 синдрома не выдает сигнал ошибка 31 и не запрещает выдачу 5-элементной информационной комбинации получателю (приемнику 32 информации) из блока 28 элементов памяти.

Одновременно с записью в анализатор 10 синдрома 31-элементная комбинация записывается в регистр 18 сдвига в течение 31 такта. В это время выход сигнала с мажоритарного элемента 24 закрыт с помощью девятого ключа 25 временной подставкой с распределителя 27 адаптивного декодера. Следующие 31 такт осуществляется пошаговый сдвиг 31-элементной комбинации в регистр 18 сдвига устройства исправления ошибок. При этом мажоритарный элемент 24, реализующий схему разделенных проверок относительно разряда а0, осуществляет исправление ошибок, то есть определяет значение разрядов а0, а1, а2 … по очереди. Во временной интервал, начиная с 32 такта, выход мажоритарного элемента 24 разблокируется временной подставкой с распределителя 27 с помощью ключа 25, и информационные элементы с а0 по а4, то есть 5 разрядов, записываются в ОЗУ. Затем на 31 такте закрывается выход мажоритарного элемента 25, обнуляется регистр 18 сдвига и анализатор 10 (вычислитель) синдрома третьего типа кода.

Счетчик ошибок на длине 31-элементной комбинации начинает счет с момента ввода указанной комбинации в регистр анализатора синдрома и устройства исправления ошибок. При этом, если количество ошибок в комбинации на длине n=31 не превышает пяти (5), то поступает сигнал, разрешающий считывание из блока 28 элементов памяти 5-элементной комбинации получателю (приемнику 32) информации. А если количество стираний на длине n=31 превышает значение пять (5), то счетчик ошибок разрешает с помощью ключа 14 выдачу сигнала «ошибка», поступающего из анализатора 10 синдрома третьего типа (S(x)≠0) для формирования сигнала стирание 5-элементной комбинации из блока 28 элементов памяти.

Таким образом, в зависимости от количества ошибок, фиксируемых счетчиком на длине 31 такта, происходит адаптация режимов исправления и обнаружения ошибок к состоянию канала связи. При этом за счет введения анализаторов синдрома и устройства исправления ошибок (регистра сдвига 18, сумматоров по модулю два 19 и 23, мажоритарных элементов 20 и 24) мажоритарным способом реализуются все возможности кода (31, 5, 16) по обнаружению ошибок.

На основании вышеизложенного алгоритма работы адаптивного декодера были определены с использованием известных методов его вероятностные характеристики.

Коды (31, 15, 6), (31, 5, 16), (31, 25, 4), при использовании их на каналах связи с коэффициентом ошибок Кош=5·10-2÷10-4, обеспечивают вероятность необнаруженной ошибки Рно в пределах 5·10-10÷ 3·10-11, а вероятность неисправленной ошибки Рош.ад на длине n=31 такт в пределах 4·10-3÷3·10-4 (1-Рно=0,996÷0,9997).

При введении режимов адаптивного декодирования и выбранных порогах адаптации wп≤5 для кода (31, 5, 16) и р=5·10-2 было получено значение вероятности Рно=1,4·10-5, а Рош.ад≈6·10-8.

Для кода (31, 15, 6) при р=10-3 и wп≤3 получены значения вероятностей Рно=1,8·10-5, а Рош.ад≈9,2·10-9.

Для кода (31, 25, 4) при р=10-4 получены значения вероятностей Рно=3·10-4, а Рош.ад≈3·10-11.

Результаты расчетов показали, что полученные значения вероятностей являются достаточными для устойчивой работы устройств асинхронного ввода (вывода) информации в смысле защиты от ошибок команд согласования скоростей и сведения к практическому минимуму сбоя фазы в широком диапазоне ошибок в канале связи.

Источники информации

1. Колесник В.Д., Мирончиков Е.Г. Декодирование циклических кодов. - М.: Связь, 1968.

2. Элементы теории передачи дискретной информации. Под редакцией Л.П.Пуртова. - М.: Связь, 1972.

3. SU, авторское свидетельство №563717, кл. Н03К 13/32, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для адаптивного мажоритарного декодирования телемеханических дублированных сигналов | 1987 |

|

SU1453599A2 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации с порогом определения неисправляемой ошибки | 2015 |

|

RU2610684C1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации | 2015 |

|

RU2613760C2 |

| УСТРОЙСТВО КОРРЕКЦИИ ОШИБОК С РАСШИРЕННЫМ НАБОРОМ РЕШАЮЩИХ ПРАВИЛ И УЧЕТОМ АДАПТИВНОГО СИГНАЛА СТИРАНИЯ | 2005 |

|

RU2309553C2 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Устройство для мажоритарного декодирования при трехкратном повторении кодовой комбинации | 1985 |

|

SU1305876A1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ ДАННЫХ, ПЕРЕДАВАЕМЫХ С ИСПОЛЬЗОВАНИЕМ БЛОЧНЫХ РАЗДЕЛИМЫХ КОДОВ, ОТ ИМИТИРУЮЩИХ ДЕЙСТВИЙ ЗЛОУМЫШЛЕННИКА | 2019 |

|

RU2738789C1 |

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

Изобретение относится к технике передачи данных, в частности к адоптивным декодерам мажоритарного декодирования. Техническим результатом является повышение вероятности приема неискаженной кодовой комбинации и точности декодирования при работе по каналам связи с низким качеством, а также повышение помехоустойчивости работы устройства. Технический результат достигается тем, что адаптивный декодер дополнительно содержит: демультиплексор, декодер первого типа кода и анализатор синдрома первого типа кода, декодер второго типа кода и анализатор синдрома второго типа кода, декодер третьего типа кода и анализатора синдрома третьего типа кода, блок управления режимами работы декодеров, счетчик стираний, второго элемента ИЛИ, восьмого и девятого ключей, анализатор качества канала связи, распределитель адаптивного декодера, блок элементов памяти и декодер качества канала. 1 ил.

Адаптивный декодер, содержащий последовательно соединенные первый элемент ИЛИ и регистр сдвига, первая группа выходов которого соединена со входами первого блока сумматоров по модулю два, выходы которого соединены со входами первого мажоритарного элемента, а также содержащий первый, второй, третий, четвертый, пятый, шестой и седьмой ключи, отличающийся тем, что в него введены демультиплексор, последовательно соединенные декодер первого типа кода и анализатор синдрома первого типа кода, последовательно соединенные декодер второго типа кода и анализатор синдрома второго типа кода, последовательно соединенные декодер третьего типа кода и анализатор синдрома третьего типа кода, блок управления режимами работы декодеров, счетчик стираний, второй элемент ИЛИ, восьмой и девятый ключи, анализатор качества канала связи (АККС), распределитель адаптивного декодера, блок элементов памяти и декодер качества канала (ДКК), при этом первый, второй и третий выходы демультиплексора подключены ко входам соответственно первого, второго и третьего ключей, а выходы первого, второго и третьего ключей подключены ко входам декодера первого типа кода, декодера второго типа кода и декодера третьего типа кода, первый, второй, третий и четвертый управляющие выходы блока управления режимами работы декодеров подключены соответственно к управляющим входам демультиплексора, первого, второго и третьего ключей, причем выходы первого, второго и третьего ключей подключены соответственно к первому, второму и третьему входам первого элемента ИЛИ, выход анализатора синдрома второго типа кода соединен с первым входом четвертого ключа, второй вход которого соединен с первым выходом счетчика стираний, второй выход которого соединен с первым входом пятого ключа, второй вход которого соединен с выходом анализатора синдрома третьего типа кода, выход анализатора синдрома первого типа кода соединен со входом шестого ключа, выходы четвертого, пятого и шестого ключей подключены соответственно к первому, второму и третьему входам второго элемента ИЛИ, выход первого мажоритарного элемента соединен со входом седьмого ключа, вторая группа выходов регистра сдвига подключена ко входам второго блока сумматоров по модулю два, выходы которого соединены со входами второго мажоритарного элемента, выход которого соединен со входом девятого ключа, выход регистра сдвига соединен со входом восьмого ключа, выходы седьмого, восьмого и девятого ключей подключены соответственно к первому, второму и третьему входам блока элементов памяти, выход которого соединен с приемником информации, первый выход АККС соединен с первым управляющим входом блока управления режимами работы декодеров, с управляющими входами шестого и восьмого ключей и с первым управляющим входом распределителя адаптивного декодера, второй выход АККС соединен со вторым управляющим входом блока управления режимами работы декодеров, с управляющими входами четвертого и девятого ключей и со вторым управляющим входом распределителя адаптивного декодера, третий выход АККС соединен с третьим управляющим входом блока управления режимами работы декодеров, с управляющими входами пятого и седьмого ключей и с третьим управляющим входом распределителя адаптивного декодера, первый и второй выходы ДКК подключены ко входам соответственно счетчика стираний и АККС, на который от ДКК поступает информация о потоке ошибок из канала связи, выход второго элемента ИЛИ соединен с управляющим входом блока элементов памяти, а первый, второй и третий выходы распределителя адаптивного декодера подключены к управляющим входам соответственно декодера первого типа кода, декодера второго типа кода и декодера третьего типа кода, при этом вход демультиплексора является входом адаптивного декодера, выходом которого является выход блока элементов памяти.

| Декодер | 1975 |

|

SU563717A1 |

| Адаптивное декодирующее устройство | 1979 |

|

SU797068A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ ПОМЕХОУСТОЙЧИВЫМ КОДОМ С ПЕРЕМЕННЫМИ ПАРАМЕТРАМИ | 2004 |

|

RU2260246C1 |

| US 6591390 В1, 2003.07.08 | |||

| US 6511280 В1, 2003.01.28 | |||

| Р.МОРЕЛОС-САРАГОСА, Искусство помехоустойчивого кодирования | |||

| Методы, алгоритмы, применение | |||

| - М.: ТЕХНОСФЕРА, 2005, с.60-67. | |||

Авторы

Даты

2010-01-20—Публикация

2008-05-26—Подача