Изобретение относится к области аналогоцифрового преобразования и может быть использовано в прецизионных кодирующих и декодирующих преобразователях для точного деления напряжения в отнощении 2 : 1.

Известное устройство для получения отношения двух напряжений состоит из двух делителей, образующих мостовую схему, в диагональ которой включен компаратор. Плечи делителей содержат потенциометры, один из которых является задающим, а другой - отрабатывающим. Ползунок последнего кинематически связан с валом двигателя, якорная цепь которого запитана через контакты поляризованного реле, используемого в качестве компаратора.

Однако в таком устройстве точность деления напряжения в заданном отношении ограничивается относительной неточностью резисторов, образующих делители, и погрешность деления не может быть снижена до величины, меньшей технологической неточности резисторов плеч делителей.

меньше относительной неточности резисторов, образующих делители.

Это достигается тем, что входы одного из делителей подключены к источнику входного напряжения через контакты реле, а выходы компаратора соединены с логической схемой, связанной с двумя цифровыми управляемыми сопротивлениями, включенными соответственно в одно из плеч каждого делителя.

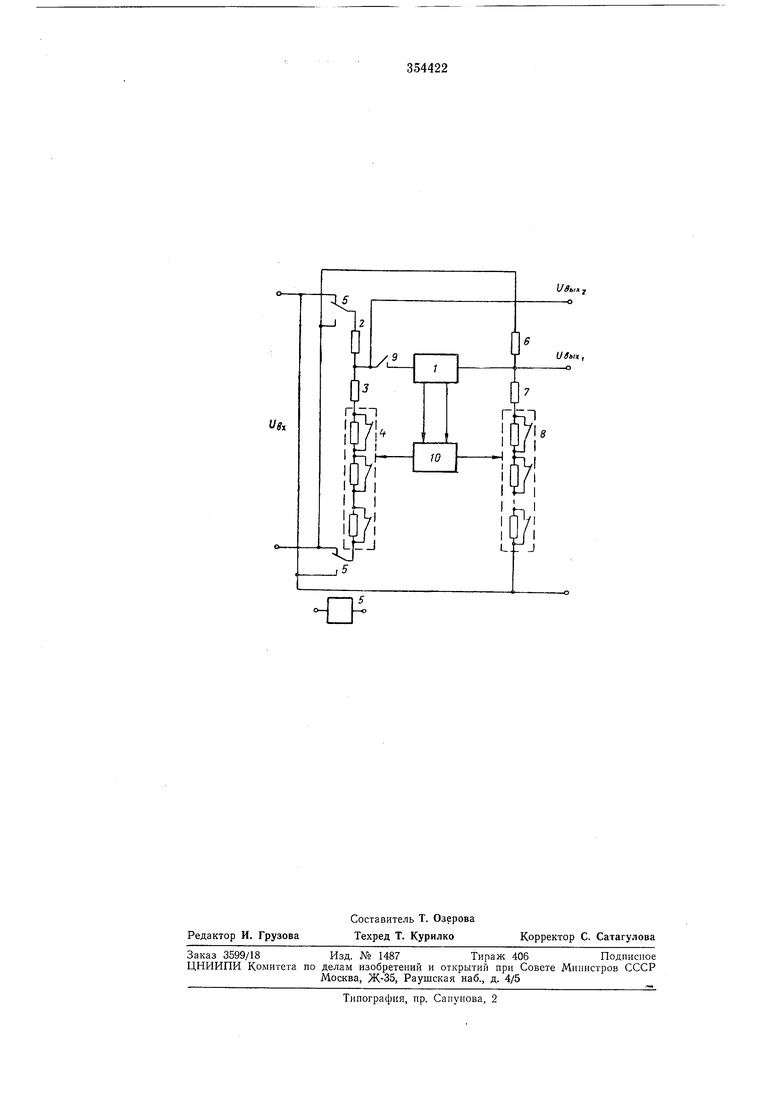

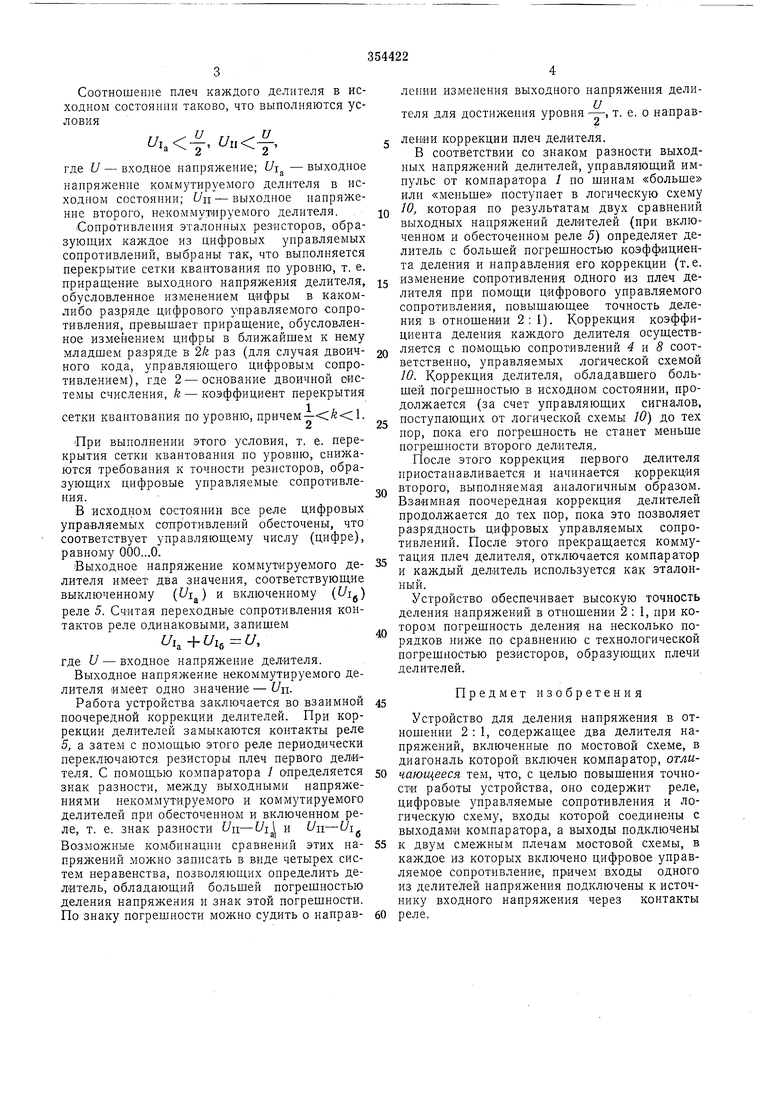

На чертеже показана блок-схема устройства. Предлагаемое устройство содержит два делителя, образующие мостовую схему, в диагональ которой включен компаратор /. Плечи

одного из делителей, состоящего из резисторов 2, 3 и цифрового управляемого сопротивления (ЦУС) 4, подключены к источнику входного напряжения через контакты реле 5 (переключатели). Второй (некоммутируемый)

делитель образован резисторами 6, 7 и цифровым управляемым сопротивлением 8. Компаратор / включен параллельно нормально открытым контактам реле 9. Выходы компаратора соединены с входами логической схемы 10, выходы которой связаны с обмотками реле, входящими в состав цифровых управляемых сопротивлений 4 и 8. Логическая схема 10 содержит два триггера, дешифратор и два регистра, управляюшие состоянием соСоотношение плеч каждого делителя в исходном состоянии таково, что вынолняются условияJJ л , , где и - входное напряжение; t/i. - выходное напряжение коммутируемого делителя в исходном состоянии; L/u -. выходиое напряжение второго, некоммутйруемого делителя. Сопротивления эталонных резисторов, образующих каждое из цифровых управляемых сопротивлений, выбраны так, что выполняется перекрытие сетки квантования по уровню, т. е. приращение выходного напряжения делителя, обусловленное изменением цифры в какомлибо разряде цифрового управляемого сопротивления, превышает приращение, обусловленное изменением цпфры в ближайшем к нему младшем разряде в 2/г раз (для случая двоичного кода, управляющего цифровым сопротивлением) , где 2 - основание двоичной системы счисления, k - коэффициент перекрытия сетки квантования по уровню, причем- ;1. При вынолнении этого условия, т. е. перекрытия сетки квантования по уровню, снижаются требования к точности резисторов, образующих цифровые управляемые сопротивления. В исходном состоянии все реле цифровых управляемых сапротивлений обесточены, что соответствует управляющему числу (цифре), равному 000...0. Выходное напряжение коммутируемого делителя имеет два значения, соответствующие выключенному (i) и включенному (ig) реле 5. Считая переходные сопротивления контактов реле одинаковыми, запишем ,fJ, где и - входное напряжение делителя. Выходное напряжение некоммутируемого делителя имеет одно значение - Uu. Работа устройства заключается во взаимной поочередной коррекции делителей. При коррекции делителей замыкаются контакты реле 5, а затем с помощью этого реле периодически переключаются резисторы плеч первого делителя. С помощью компаратора / определяется знак разности, между выходными напряжениями некоммутируеморо и коммутируемого делителей при обесточенном и включенном реле, т. е. знак разности Un-Ui и Uu--i/i Возможные коМбинацни сравнений этих напряжений можно записать в виде четырех систем неравенства, позволяющих определить делитель, обладающий большей погрешностью деления напряжения и знак этой погрешности. По знаку погрешности можно судить о направлении изменения выходного напряжения делителя для достижения уровня -, т. е. о налравленйи коррекции плеч делителя. В соответствии со знаком разности выходных напряжений делителей, управляющий импульс от компаратора 1 по шинам «больше или «меньше поступает в логическую схему W, которая по результатам двух сравнений выходных напряжений делителей (при включенном и обесточенном реле 5) определяет делитель с большей погрешностью коэффициента деления и направления его коррекции (т.е. изменение сопротивления одного из плеч делителя при помощи цифрового управляемого сопротивления, повыщающее точность деления в отношении 2:1). Коррекция коэффициента деления каждого делителя осуществляется с помощью сопротивлений 4 и 8 соответственно, управляемых логической схемой 10. Коррекция делителя, обладавшего большей погрешностью в исходном состоянии, продолжается (за счет управляющих сигналов, поступающих от логической схемы 10) до тех пор, пока его погрешность не станет меньше погрешности второго делителя,. После этого коррекция первого делителя приостанавливается и начинается коррекция второго, выполняемая аналогичным образом. Взаимная поочередная коррекция делителей продолжается до тех пор, пока это позволяет разрядность цифровых управляемых сопротивлений. После этого прекращается коммутация плеч делителя, отключается компаратор и каждый делитель используется как эталонный. Устройство обеспечивает высокую точность деления напряжений в отнощении 2 : 1, при котором погрещность деления на несколько порядков ниже по сравнению с технологической погрешностью резисторов, образующих плечи делителей. Предмет изобретения Устройство для деления напряжения в отношении 2:1, содержащее два делителя напряжений, включенные по мостовой схеме, в диагональ которой включен компаратор, отличающееся тем, что, с целью повыщения точности работы устройства, оно содержит реле, цифровые управляемые сопротивления и логическую схему, входы которой соединены с выходами компаратора, а выходы подключены к двум смежным плечам мостовой схемы, в каждое из которых включено цифровое управляемое сопротивление, причем входы одного из делител-ей напряжения подключены к источнику входного напряжения через контакты реле.

t/л,

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ МЕТАНА И ДРУГИХ ГОРЮЧИХ ГАЗОВ | 1991 |

|

RU2013565C1 |

| Устройство для измерения изменений сопротивления | 1982 |

|

SU1022059A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Устройство для деления напряжений | 1979 |

|

SU830412A1 |

| Устройство для преобразования сигналов резистивных датчиков в цифровой код | 1973 |

|

SU481130A1 |

| Цифровой измерительный неуравновешанный мост | 1978 |

|

SU789767A1 |

| АЭРОЛОГИЧЕСКИЙ РАДИОЗОНД | 1999 |

|

RU2162238C1 |

| Преобразователь температуры в цифровой код | 1980 |

|

SU892234A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ ИЗОЛЯЦИИ СЕТЕЙ ПОСТОЯННОГО ТОКА | 1991 |

|

RU2026561C1 |

| Устройство для деления напряжений | 1976 |

|

SU604003A1 |

Даты

1972-01-01—Публикация