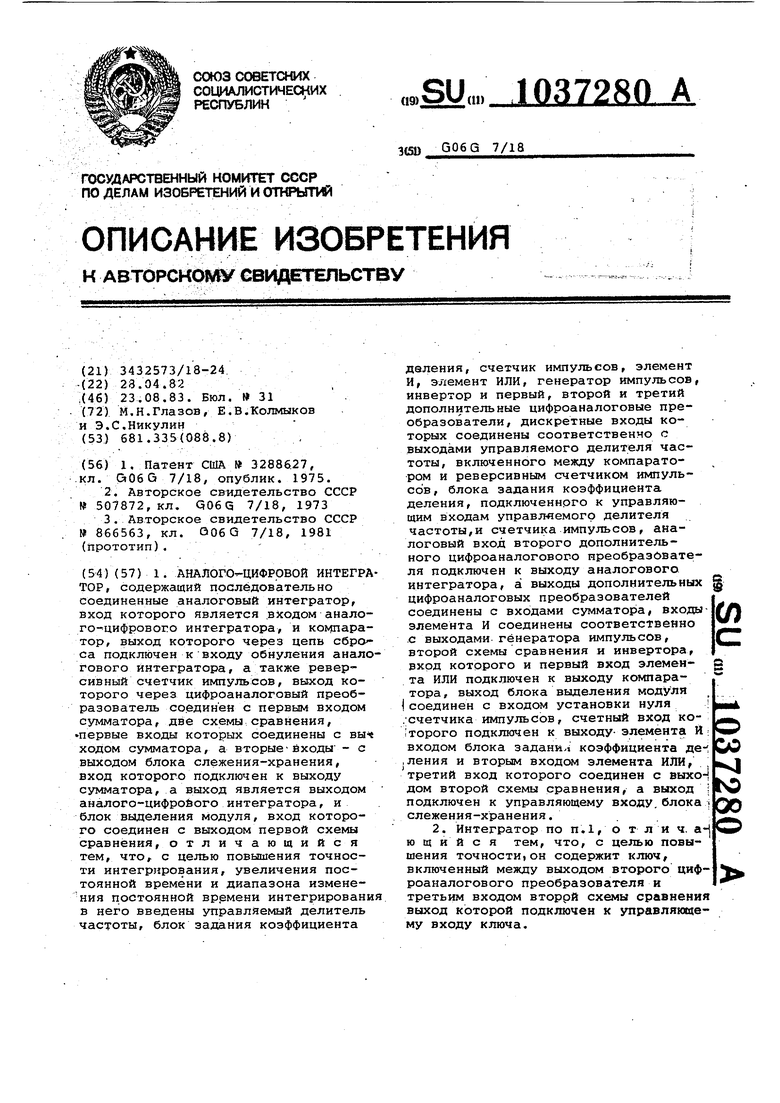

Изобретение относится к автоматике, предназначено для формирования напряжения, пропорционального интег- . ралу от входного сигнала, и может не- пользоваться в системах автоматического управления различными технологичес: ими процессами и объемами, когда тр1ебуются большие постоянные интегрирования..

Известны устройства для интегрирования , содержащие реверсивный счетчик иг/1пульсов, цифроаналоговый преобразователь и преобразователь напряжение частота, выполненный на основе ана.логового интегратора и компаратора СП-.15

Недостатком таких устройств является то , что вследствие сбоев счетчика под действием случайных помех и перерывов в подаче питания происходит разрушение информации, накоп- 20 ленной интегратором, что может при- водить к аварийным последствиям, а потому во многих случаях совершенно недопустимо.

Известен аналого-цифровой интегра-25 тор, в котором наряду с указанными элементами и цифроаналоговым преобразователем с выходным сумматором, второй вход которого подключен к -выходу аналогового интегратора, приме- ... иен контурвосстановления инфор: 1ации, содержащий последовательно включенные блоки слежения-хранения, выявления модуля, сравнения и логическую схему управления режимами работы блока слежения-хранения С2.35

Недостатком этого интегратора яв-. ляется погрешность интегрирования, связанная с неравенством квантов напряжения на выходах аналогового интегратора и цифроаналогового преоб- 40 разователя. Это обусловлено как погрешностями цифроаналогового преобразователя, в частностинепостоя.нством его шага квантования, так и неточностью релейных элементов в преобра- 45 зователе напряжение-частота, осуществляющих квантование интеграла входного сигнала. В результате в моменты сброса аналогового интегратора (в точках квантования) возникают скачки сп напряжения на выходе интегратора, что снижает точность интегрирования. Это затрудняет использование интегратора/ в особенности в устройствах дифференцирования медленно меняк)1цихпя сигналов, когда интегратор включается в обратную связь усилителя с большим коэффициентом усиления.

Наиболее близким к изобретению по технической сущности является аналого-цифровой интегратор, содер- 60 жащий последовательно соединенные аналоговый интегратор, компаратор, реверсивный счетчик импульсов, цифроаналоговый преобразователь, сум- . матор и блок слежения-Хранения, две 65

схемы сравнения, первые входы которых соединены с выходом сумматора, а вторые входы - с выходом блока слежения-хранения, два блока выделения модуля, второй блок слежения-хране-ния, ,а также логические элементы И, И-НЕ и сложения по модулю два,соответствующим образом соединенные между, собой и с другими элементами схемы. Благодаря введению в данное устройство контура сглаживания выходного напряжения обеспечивается повышение точности работы устройства за счет уменьшения составляющей погрешности, обусловленной непостоянством шага квантования цифроаналогового преобразователя 3j.

Недостатком известного интегратора является .наличие погрешности в ре- хранения и при интегрировании малых напряжений, когда в промежутках между импу.льсами на входе счетчика блок слежения-хранения в контуре формирования сигнала коррекции изменяет свое выходное напряжение из-за дрейфа используемого в нем операционного усилителя, утечек, конденсатора .и других дестабилизирующих факторов. Наряду со снижением точности это не позволяет использовать принцип деления частоты импульсов на входе Счетчика, обеспечивающий получение достаточно больших и легко перестраиваемых по необходимым законам постоянных интегрирования.

Целью изобретения является повышение точности интегрирования, увеличение постоянной времени и Диапазона изменения постоянной времени интегрирования.

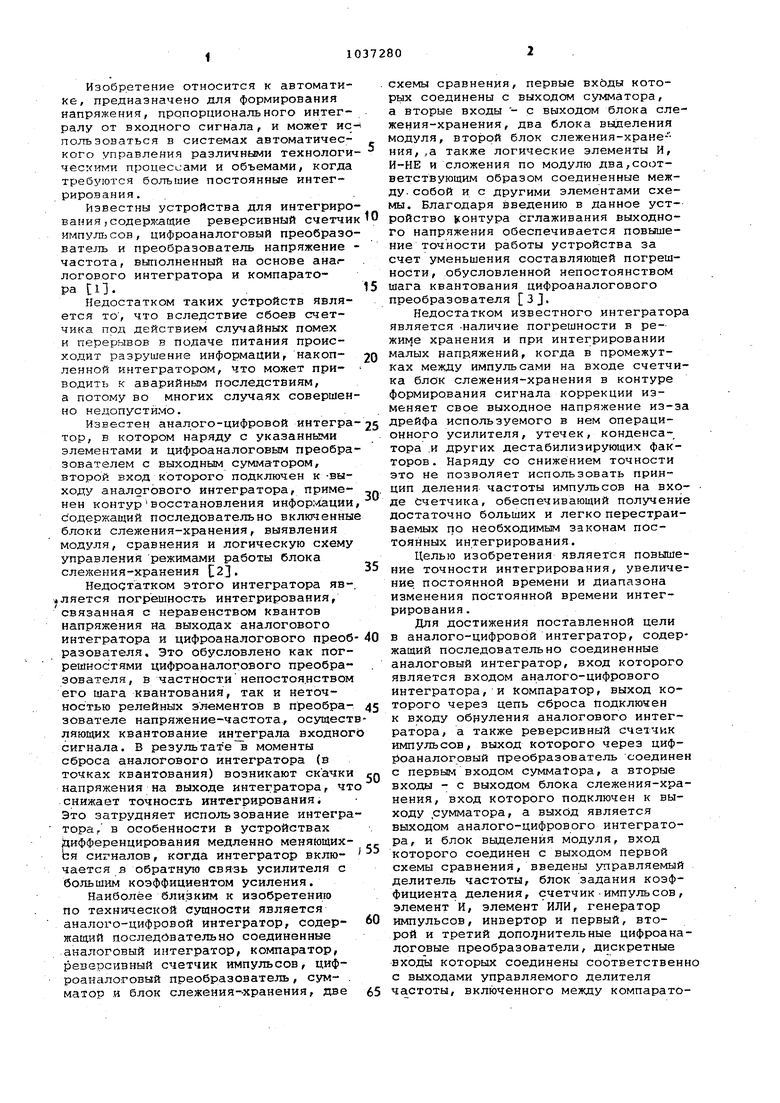

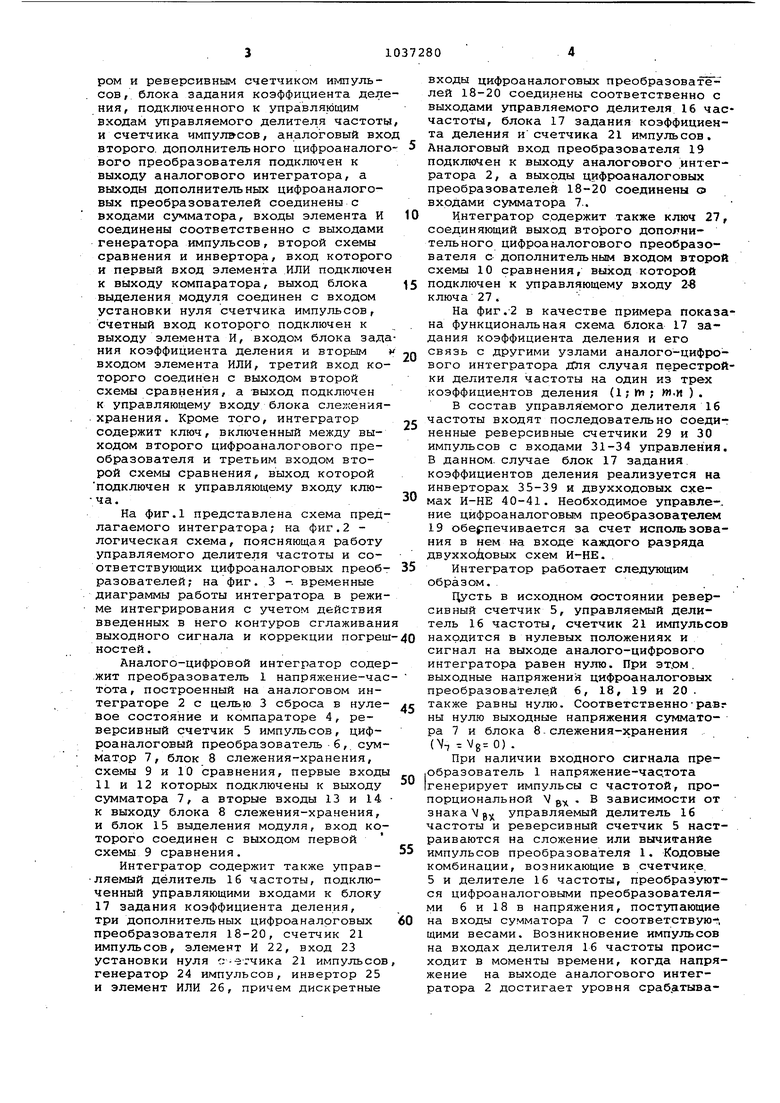

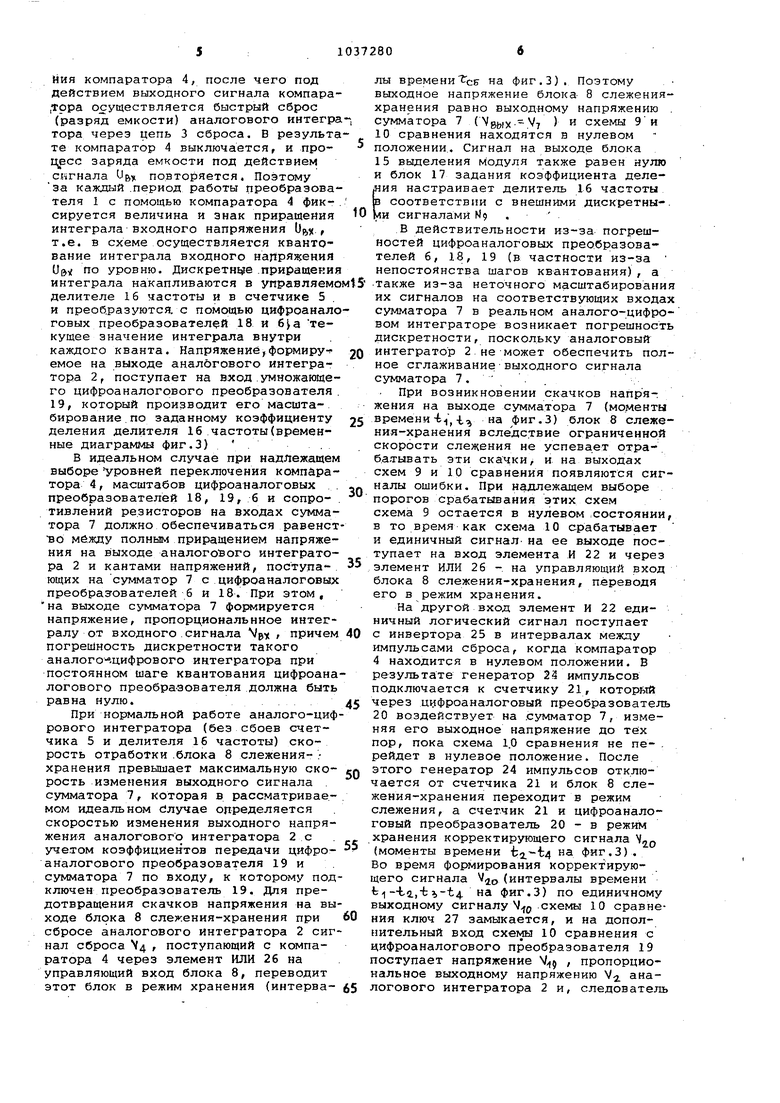

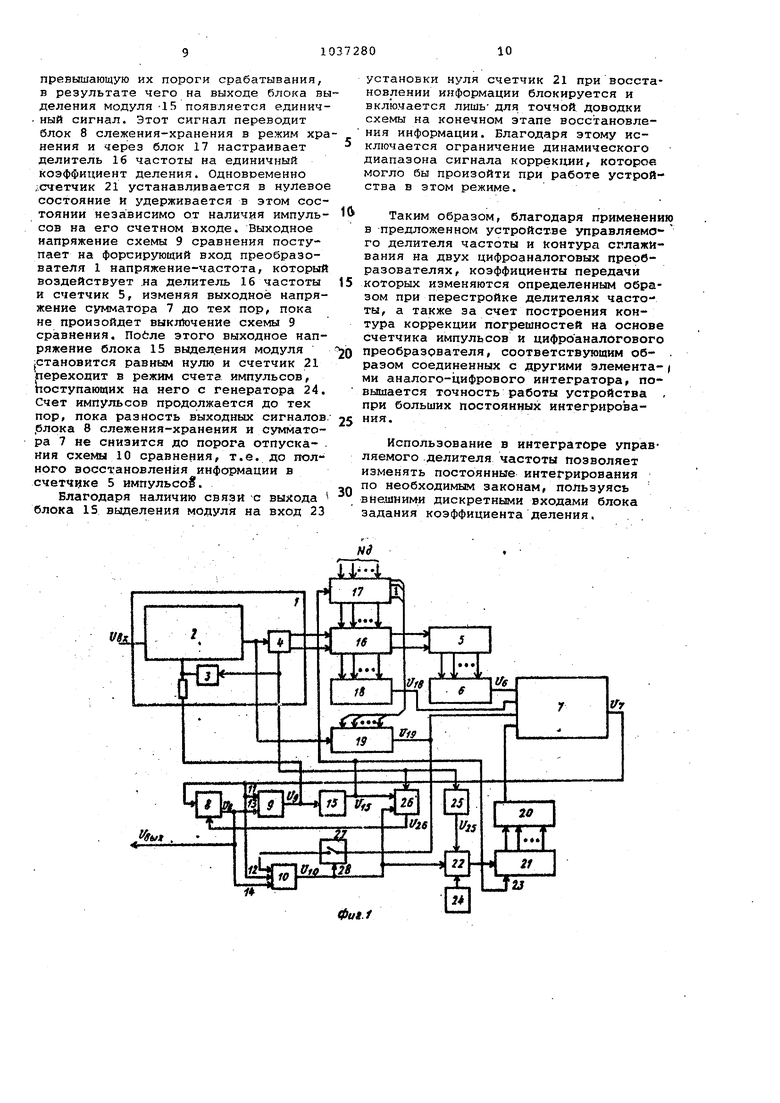

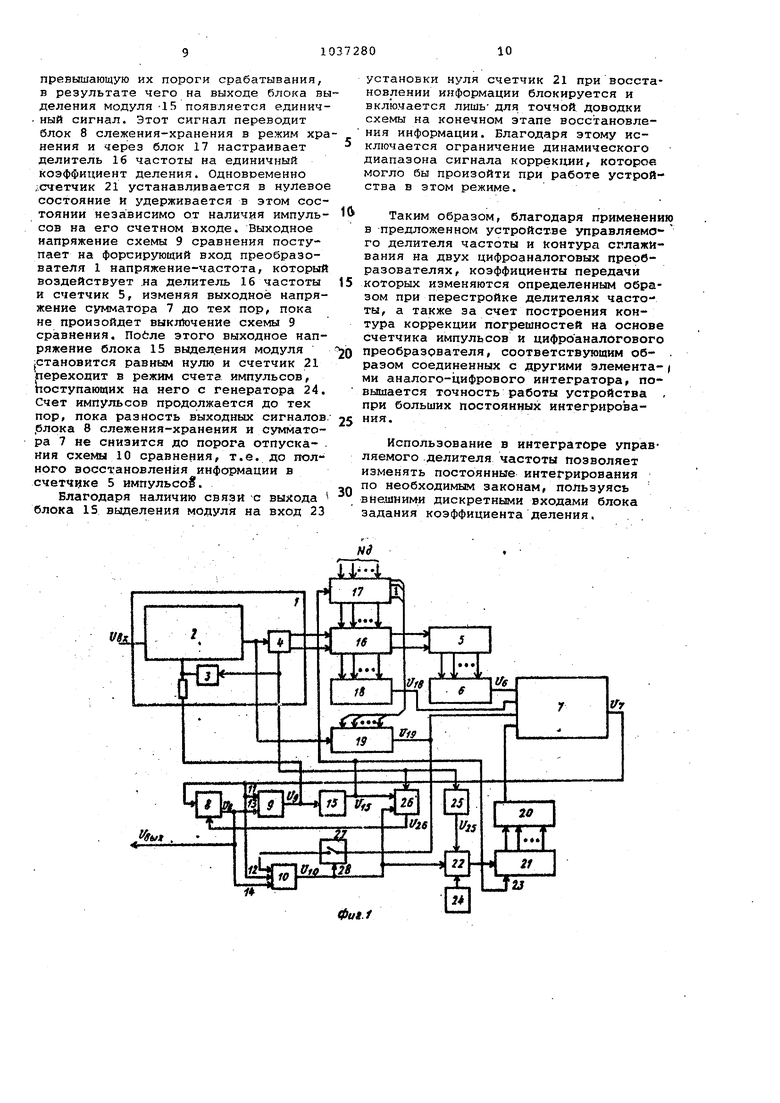

Для достижения поставленной цели в аналого-цифровой интегратор, содержащий последовательно соединенные аналоговый интегратор, вход которого является входом аналого-цифрового интегратора, и Компаратор, выход которого через цепь сброса подключен к входу обнуления аналогового интегратора, а также реверсивный счетчик импульсов, выход которого через цифроаналогрвЫй ПреОбразовате.пь соединен с первым входом сумматора, а вторые входы - с выходом блока слежения-хранения, вход которого подключен к выходу сумматора, а выход является выходом аналого-цифрового интегратора, и блок выделения модуля, вход которого соединен с выходом первой схемы сравнения, введены управляемый делитель частоты, блок задания коэффициента деления, счетчик.импульсов, элемент И, элемент ИЛИ, генератор импульсов, инвертор и первый, второй и третий допо 1нительные цифроаналоговые преобразователи, дискретные входы которых соединены соответственн с выходами управляемого делителя частоты, включенного между компаратором и реверсивным счетчиком импульсов, блока задания коэффициента деле ния, подключенного к управляющим входам управляемого делителя частоты и счетчика импулвсов, аналоговый вхо второго, дополнительного цифроаналого вого преобразователя подключен к выходу аналогового интегратора, а выходы дополнительных цифроаналоговых преобразователей соединены с входами сумматора, входы элемента И соединены соответственно с выходами генератора импульсов, второй схемы сравнения и инвертора, вход которог и первый вход элемента ИЛИ подключе к выходу компаратора, выход блока выделения модуля соединен с входом установки нуля счетчика импульсов, Счетный вход которого подключен к выходу элемента И, входом блока зад ния коэффициента деления и вторым входом элемента ИЛИ, третий вход которого соединен с выходом второй схемы сравнения, а -выход подключен к управляющему входу блока слежения. хранения. Кроме того, интегратор содержит ключ, включенный между выходом второго цифроаналогового преобразователя и третьим входом второй схемы сравнения, выход которой подключен к управляющему входу ключа. На фиг.1 представлена схема предлагаемого интегратора; на фиг . 2 логическая схема, поясняющая работу управляемого делителя частоты и соответствующих цифроаналоговых преобразователей; на фиг. 3 -. временные диаграммы работы интегратора в режиме интегрирования с учетом действия введенных в него контуров сглаживани выходного сигнала и коррекции погреш ностей. Аналого-цифровой интегратор содер жит преобразователь 1 напряжение-час тота, построенный на аналоговом интеграторе 2 с целью 3 сброса в нулевое состояние и компараторе 4, реверсивный счетчик 5 импульсов, цифроаналоговый преобразователь б,, сумматор 7, блок 8 слежения-хранения, схемы 9 и 10 сравнения, первые входы 11 и 12 которых подключены к выходу сумматора 7, а вторые входы 13 и 14 к выходу блока В слежения-хранения, и блок 15 выделения модуля, вход которого соединен с выходом первой схемы 9 сравнения. Интегратор содержит также управляемый делитель 16 частоты, подключенный управляющими входами к блоку 17 задания коэффициента деления, три дополнительных цифроаналоговых преобразователя 18-20, счетчик 21 импульсов, элемент И 22, вход 23 установки нуля с:- гчика 21 импульсов генератор 24 импульсов, инвертор 25 и элемент ИЛИ 26, причем дискретные входы цифроаналоговых преобразовате- лей 18-20 соединены соответственно с выходами управляемого делителя 16 часчастоты, блока 17 задания коэффициента деления исчетчика 21 импульсов. Аналоговый вход преобразователя 19 подключен к выходу аналогового интегратора 2, а выходы цифроаналоговых преобразователей 18-20 соединены о входами сумматора 7.. Интегратор содержит также ключ 27, соединяющий выход второго дополнительного цифроаналогового преобразователя с дополнительным входом второй схемы 1C сравнения, выход которой подключен к управляющему входу 2-8 ключа 27. На фиг.2 в качестве примера показана функциональная схема блока 17 за Дания коэффициента деления и его связь с другими узлами аналого-цифрового интегратора для случая перестройки делителя частоты на один из трех коэффициентов деления {1; Itr ; Wi.K ) . В состав управляемого делителя 16 частоты входят последовательно соединенные реверсивные счетчики 29 и 30 импульсов с входами 31-34 управления. В данном, случае блок 17 задания коэффициентов деления реализуется на инверторах 35-39 и двухходовых схемах И-НЕ 40-41. Необходимое управле-. ние цифроаналоговым преобразователем 19 обеспечивается за счет использования в нем н-а входе каждого разряда двуххо 1овых схем И-НЕ. Интегратор работает следующим образом. Цусть в исходном оостоянии реверсивный счетчик 5, управляемый делитель 16 частоты, счетчик 21 импульсов находится в нулевых положениях и сигнал на выходе аналого-цифрового интегратора равен нулю. При эхом, выходные напряжения цифроаналоговых преобразователей 6, 18, 19 и 20 . также равны нулю. Соответственноравг ны нулю выходные напряжения сумматора 7 и блока 8 - слежения-хранения (V-,). При наличии входного сигнала пре.образователь 1 напряжение-частота генерирует импульсы с частотой, пропорциональной V gy . В зависимости от знакаVg управляемый делитель 16 частоты и реверсивный счетчик 5 настраиваются на сложение или вычитание импульсов преобразователя 1. Кодовые комбинации, возникающие в счетчике. 5 и делителе 16 частоты, преобразуются цифроаналоговыми преобразователями 6 и 18 в напряжения, поступающие на входы сумматора 7 с соответствую-, щими весами. Возникновение импульсов на входах делителя 16 частоты происходит в моменты времени, когда напряжение на выходе аналогового интегратора 2 достигает уровня срабатывайия компаратора 4, после чего под действием выходного сигнала компара,трра осуществляется быстрый сброс {разряд емкости) аналогового интегра тора через цепь 3 сброса. В результате компаратор 4 выключается, и процесс заряда емкости под действием сигнала повторяется. Поэтому за каждый .период работы преобразователя 1 с помощью компаратора 4 фиксируется величина и знак прирашейия интеграла входного напряжения 0.,у., т.е. в схеме осуществляется квантование интеграла входного наряжения Uuv по уровню. Дискретн1#е .приращения интеграла накапливаются в управляемо делителе 16 частоты и в счетчике 5 и преобразуются, с помощью цифроаналоговых преобразователей 18 и текущее значение интеграла внутри каждого кванта. Напряжение,формируемое на выходе аналогового интегратора 2, поступает на вход.умножающего цифроаналогового преобразователя . 19, который производит его масштабирование, по заданному коэффициенту деления делителя 16 частоты(временные диаграммы фиг.З) . .

В идеальном случае при надлежащем выборе уровней переключения компаратора 4, масштабов цифроаналоговых

.. преобразователей 18, 19, б и сопротивлений ре.зисторов на входах сумматора 7 должно обеспечиваться равенство мбжду полным приращением напряжения на выходе аналогового интегратора 2 и кантами напряжений, поступающих на сумматор 7 с цифроаналоговых преобразователей 6 и 18. При этом, на выходе сумматора 7 формируется напряжение, пропорциональнное интегралу от входного .сигнала /рх / причем погрешность дискретности такого аналого-.цифрового интегратора при постоянном шаге квантования цифроаналогового преобразователя должна быть равна нулю.

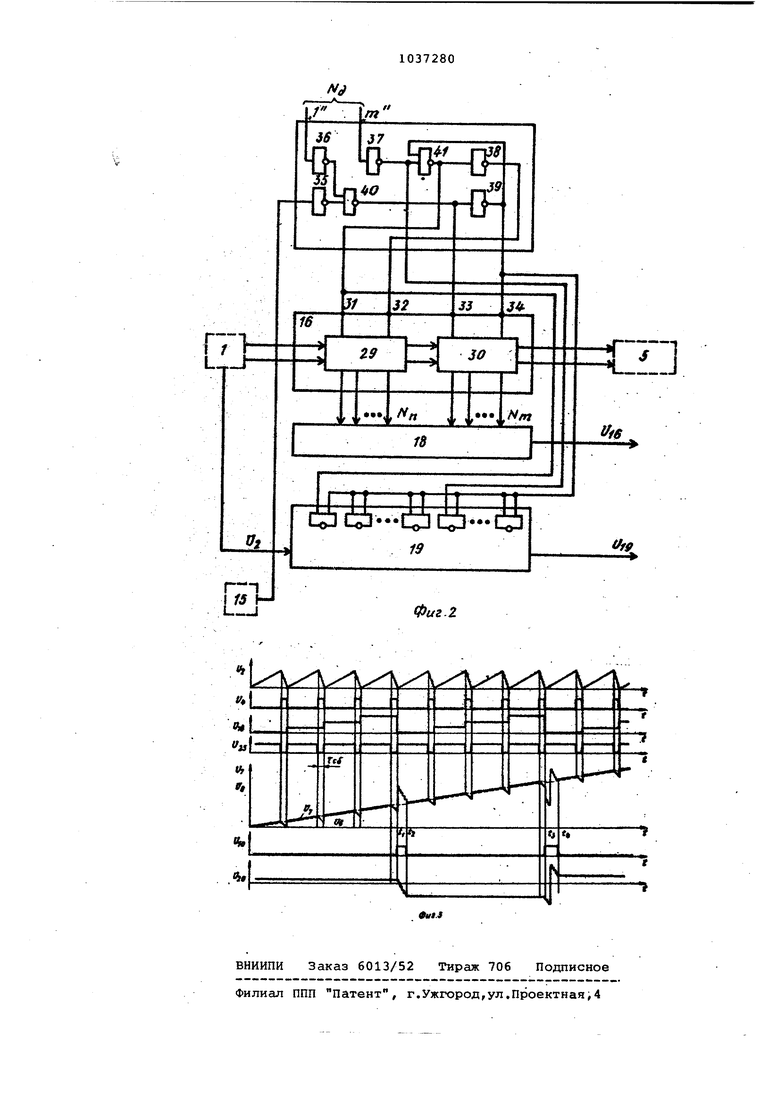

При нормальной работе аналого-цифрового интегратора (без сбоев счетчика 5 и делителя 16 частоты) скорость отработки .блока 8 слежения- .хранения превышает максимальную скорость изменения выходного сигнала . сумматора 7, которая в рассматривае.мом идеальном Случае определяется скоростью изменения выходного напряжения аналогового интегратора 2с . учетом коэффициентов передачи цифроаналогового преобразователя 19 и сумматора 7 по входу, к которому подключен преобразователь 19. Для предотвращения скачков напряжения на выходе блока 8 слежения-хранения при сбросе аналогового интегратора 2 сигнал сброса 4 поступающий с компаратора 4 через элемент ИЛИ 26 на управляющий вход блока 8, переводит этот блок в режим хранения (интервалы времениtcs на фиг.З) , Поэтому выходное напряжение блока 8 слеженияхранения равно выходному напряжению сумматора 7 (йь1Х 7 ) и схемы 9и 10 сравнения находятся в нулевом положении. Сигнал на выходе блока 15 выделения модуля также равен нулю и блок 17 задания коэффициента деле|Ния настраивает делитель 16 частоты р соответствии с внешними дискретными сигналами М

В действительности из-за погрешностей цифроаналоговых преобразова телей б, 18, 19 (в частности из-за непостоянства шагов квантования), а также из-за неточного масштабировани их сигналов на соответствующих входа сумматора 7 в реальном аналого-цифровом интеграторе возникает погрешност дискретности, поскольку аналоговый интегратор 2 не может обеспечить полное сглаживание выходного сигнала сумматора 7. . .

При возникновении скачков напрят жения на выходе сумматора 7 (моменты времени-tV, i Фиг.З) блок 8 слежения-хранения вследс.твие ограниченной скорости слежения не успевает отрабатывать эти скачки, и на выходах схем 9 и 10 сравнения появляются сигналы ошибки. При надлежащем выборе порогов срабатывания этих схем схема 9 остается в нулевом .состоянии в то время как схема 10 срабатывает и единичный сигнаЛ на ее выходе поступает на вход элемента И 22 и через элемент ИЛИ 26 - на управляющий вход блока 8 слежения-хранения, п.ереводя его в режим хранения.

На другой вход элемент И 22 единичный логический сигнал поступает с инвертора 25 в интервалах между импульсами сброса, когда компаратор 4 находится в нулевом положении. В результате генератор 24 импульсов подключается к счетчику 21, который через цифроаналоговый преобразователь 20 воздействует на .csT /iMaTOp 7, изменяя его выходное напряжение до тех пор, пока схема 1,0 сравнения не пе- . рейдет в нулевое положение. После этого генератор 24 импульсов отключается от счетчика 21 и блок 8 слежения-хранения переходит в режим слежения, а счетчик 21 и цифроаналоговнй преобразователь 20 - в режим хранения корректирующего сигнала (моменты времени Ь.-Ьд на фиг.З). Во время формирования корректирующего сигнала (интервалы времени t-i-ta.,i:%-t4 на фиг.З) по единичному выходному сигналу схемы 10 сравнения ключ 27 замыкается, и на дополнительный вход схемы 10 сравнения с дифроаналогового преобразователя 19 поступает напряжение , пропорциональное выходному напряжению V. аналогового интегратора 2 и, следователь

но пропорциональное текущему эначению интегратора входного .напряжений.

С учетом наличия на входе схемы 10 с эавнения указанной добавки отпускание схемы 10 (моменты времени , i2,;4 фиг.З) происходит, когда выходное напряжение сумматора 7 становится равным сумме напряжений Ve Vg и V( . Благодаря этому во время формирования корректирующего сигнала сохраняется информация о текущем зна- чении интегратора от V и тем самым повышается точность устройства.

Таким образом, скачки напряжения яа выходе сумматора 7, обусловленные указанньзми погрешностями, не пр.оходят15 на выход интегратора, поскольку они компенсируются с помоооэю специально введённого корректирующего контура, содержащего.счетчик 21,.цифроаналоговый преобразователь 20 и генераг .JQ ТОР 24, -который подключен к дополнит тельному ВХОДУ .сумматора 7. Коррек-. тирующее воздейстэиё, вырабатываемое этим контуром, сохраняется неизменным до поступления, следущего имп.ульса 25 на управляемый делитель .16 частоты, т.е. до получения очередного кванта интеграла от. входного сигнгша. При; этом обновление коррек.тирующего воздейств.йя происходит лишь в том.слу-.-чае, если на вхрдах схемы Ю сравне- ния возйикает ошибка, превышающая. . ее порог чувствительности. В противном случае корректирующее воздействие сохраняется неизменные. . .

В отличие от известной схемы 35 аналого-цифрового.интегратора корректирующее воздействие, вырабатывавемое предложенным устройством, . сохраняется CKOJHJ угодно долго , Это позволяет существенно повьясить точг 40 ность аналого-цифровых, интеграторов с большими постоянными интегрирования (при весьма малых частотах следоват ния импульсов) . Повьа аение точности . достигается не только в режимах. 45 интегрирования, но и в .режимах.хранения, что имеет практическое зна-. чение для астатических систем автоматического управления Возможность сколь угодно длительного хранения ,« корректирующего воздействия, позволяет существенно увеличить постоянную, интегрирования путем введения .в . . интегратор управляемого делите:ля час- тоты. , . . .. «е

Приведенная на фиг.2 рхема вклю- чения управляемого делителя 16 част тоты обеспечивает перестройку делителя по внешним сигналам блока 17 (входы , т)- .на один из трех,. коэффициентов деления 1;т; т-п . При нулевых сигналах на входах Ч h vyj блока 17 и нулевом сигнё1Лё со схемы 9 сравнения логические.элементы 35-41 формируют на входах 31 . и 33 делителя 16 частоты нулевые 5

сигналы, а на входах 32 и 34 - единичные. При этом реверсивные счетчики. 29 и 30 импульсов имеют коэффициенты еления соответственно и и i , а

общий коэффициент деления частоты составляет n-w . Выходные KJy, и yvt с выходов счетчиков 29 и 30 преобразуются цифроаналоговым проеобразователем 18 в ступенчатое напряжение, имеющее и-W квантов в каждом. . периоде повторении и амплитуду, экви валентную одному,кванту основного цифроаналогового преобразователя 6. В этом.случае цифроаналоговый преобразователь 19 имеет минимальный коэффициент передачи (так как нулевой. сигнал воздействует лишь на младодаий

разряд), и масштаб напряжения . соответствует одному кванту цифроаналогового преобразователя 18 (v.)

Н г

Если сигнал на входе VH.блока 17 принимает единичное значение, то сигналы на входах 31 и.32 делителя 16 частоты изменяют свои значения, и счетчик 29 настраибается на единичный коэффициент деления, причем выходной код Ну, становится равным нулю. При этом общий коэффициент деления частоты делителя 16 становится, равными, число квантов в периоде повторения напряжения также уменьшается до м (при той же амплитуде), а цифроаналоговый преобразователь 19 настраивается по нулевому сигналу со схемы. И-НЕ 41 на коэффициент передачи fff« , в результате .чего происходит соответствукадее увеличение масштаба напряжения

Когда сигнал на входе i блока 17 имеет единичное значение, счетчики 20 и 30 работают с коэффициентами деления, {явными 1, и их выходные коды N, иЫп равны нулю. Это соответствует нулевс «у значению выходного напряжения преобразователя 18 ( V;f0 0) и максим.альнсяу(у коэффициенту передачи преобразователя 19 ( : Vj ) , так как на все разряды последнего поступает нулевой сигнал с выхода инвертора 39.

Следовательно, в предложенной схеме обеспечивается фо{ 1ирование двух напряжений (ступенчатого с преобразователя 18 и пилообразного с преобразователя 19), которые позволяют сгладить ступенчатое напряжение основного цифроаналогового преобразователя 6 при всех возможных коэффициентах деле ния частоты, згщаваемых внешними дискретными сигналами.

Рассмотрим теперь работу аналогоцифрового интегратора при сбоях реверсивного счетчика 5, вызванных, например, действием случайных помех. При этом из-за ограниченной скорости . отработки блока 8 слежения-хранения сигналы на входах обеих схем 9 и 10 сравнения отличаются на величину. Превышающую их пороги срабатывания, в результате чего на выходе блока в деления модуля -15 появляется единич . ный сигнал. Этот сигнал переводит блок 8 слежения-хранения в режим хр нения и через блок 17 настраивает делитель 16 частоты на единичный коэффициент деления. Одновременно ;.счетчик 21 устанавливается в нулево состояние и удерживается в этом состоянии независимо от наличия импульсов на его счетном входе. Выходное напряжение схемы 9 сравнения поступает на форсирующий вход преобразователя 1 напряжение-частота, который воздействует .на делитель 16 частоты и счетчик 5, изменяя выходное напряжение сумматора 7 до тех пор, пока не произойдет выкл5очение схемы 9 сравнения. Побле этого выходное напряжение блока 15 выделения модуля ртановится равньм нулю и счетчик 21 переходит в режим счета импульсов, поступающих на него с генератора 24. Счет импульсов продолжается до тех пор, пока разность выходных сигналов .блока 8 слежения-хранения и сумматора 7 не снизится до порога отпускания схемы 10 сравнения, т.е. до полного восстановления информации в счетчике 5 импульсов. Благодаря наличию связи с выхода блока 15 выделения модуля на вход 23 установки нуля счетчик 21 при восстановлении информации блокируется и включается лишь- для точной доводки схемы на конечном этапе восстановления информации. Благодаря этому исключается ограничение динамического диапазона сигнала коррекции, которое могло бы произойти при работе устройства в этом режиме. Таким образом, благодаря применению в предложенном устройстве управляемого делителя частоты и контура сглаживания на двух цифроаналоговых преобразователях, коэффициенты передачи которых изменяются определенным образом при перестройке делителях частоты, а также за счет построения контура коррекции погрешностей на основе счетчика импульсов и цифроаналогового преобразователя, соответствующим об- . разом соединенных с другими элемента-( ми аналого-цифрового интегратора, повышается точность работы устройства , при больших постоянных интегрирования. Использование в интеграторе управляемого .делителя частоты позволяет изменять постоянные интегрирования по необходимым законам, пользуясь внешним:и дискретными входами блока задания коэффициента деления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой интегратор | 1978 |

|

SU805345A1 |

| Аналого-цифровой интегратор | 1980 |

|

SU866563A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1425832A1 |

| Аналого-цифровой интегратор | 1979 |

|

SU813456A2 |

| Аналого-цифровой интегратор | 1988 |

|

SU1534473A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Логарифмический преобразователь | 1982 |

|

SU1042035A2 |

| Преобразователь напряжения в код | 1988 |

|

SU1547061A1 |

| Аналого-цифровой интегратор | 1977 |

|

SU682908A2 |

| Интегрирующее устройство | 1985 |

|

SU1300500A1 |

1. АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР, содержащий последовательно соединенные аналоговый интегратор, вход которого является входом аналого-цифрового интегратора, и компаратор, выход которого через цепв сбрсмса подключен к входу обнуления аналогового интегратора, а также реверсивный счетчик импульсов, выход которого через цифроаналоговый преобразователь соединен с первым входом сумматора, две схемы сравнения, первые входы которых соединены с ВЫЧ ходом сумматора, а вторые-входы - с выходом блока слежения-хранения, вход которого подключен к выходу сумматора, а выход является выходом аналого-цифройого интегратора, и блок выделения модуля, вход которого соединен с выходом первой схемы сравнения, отличающийся тем, что,, с целью повышения точности интегрирования, увеличения постоянной времени и диапазона изменения постоянной вр.емени интегрирования в него введены управляемый делитель частоты, блок задания коэффициента деления, счетчик импульсов, элемент И, элемент ИЛИ, генератор импульсов, инвертор и первый, второй и третий дополнительные цифроаналоговые преобразователи, дискретные входы которых соединены соответственно с выходами управляемого делителя частоты, включенного между компаратором и реверсивным счетчиком импульсов, блока задания коэффициента деления, подключенного к управляющим В1ходам управляемого делителя частоты,и счетчика импульсов, аналоговый вход второго дополнительного цифроаналогового преобразователя подключен к выходу аналогового интегратора, а выходы дополнительных цифроаналоговых преобразователей (О соединены с входами сумматора, входыэлемента И соединены соответственно .с выходами, генератора импульсов, второй схемы сравнения и инвертора, вход которого и первый вход элемента ИЛИ подключен к выходу компаратора, выход блока выделения модуля соединен с входом установки нуля -i .счетчика импульсов, счетный вход коэ :о .торого подключен к выходу- элемента И: входом блока заданий коэффициента де,ления и вторым входе элемента ИЛИ, Ч третий вход которого соединен с выхоЮ X) дом второй схемы сравнения, а выход i подключен к управляющему входу.блокаi слежения-хранения. о 2. Интегратор по п.1, о т ли ч. аЧ ю щ и и с я тем, что, с целью повышения точности,он содержит ключ, включенный между выходом второго цифроаналогового преобразователя и третьим входом вторрй схемы сравнения выход которой подключен к управляющему входу ключа.

Фи.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3288627, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-08-23—Публикация

1982-04-28—Подача