1

Известны устройства для декодирОваНИ.я «елинейных КОДОВ с исиользовайием матричных дешифраторов, IB которых для декодирования каждого кодового вектора приа аняют «нвходовую схему со1В1падения. Очевидно, что число П-1ВХОД01ВЫХ схем С0|владе1ния ражно числу декодируемых В-акторов. Число п-1входо1вых cxeiM еоанадения |МОЖна значительно сократить, т. К. IB |рассматри1ваел1ых кодах значительная часть 1СИМВОЛ01В кодовых векторов может быть представле«а кодовыми ;кольцами. Так, например, первые п - 1 символов кодовых векторов МОгут быть представлены четырьмя кодовыми кольцами: -О-, -10111000101, -I-, -01000111010-

Следовательно, в любо1М кодовом векторе inepiBbiie п-I -символов 1на некотором сдвиге будут совпадать с .одним из кодовых колец. Для правильного декодирования кодовых векторов достаточно обеспечить в лрием-ном реiFHCTpe Иосле его заполнения циклическую перестановку первых п-1 ic и MB о лов и отдельно сдвиг последнего символа. В этом случае число «-ВХОДОВЫХ схем совпадения равно числу КОДО1ВЫХ колец.

Целью изобретения является расширение функциональных в.оз;можностей из1вестных устройств и |0нижение аопаратурных затрат.

Для достижения цели предлагаемое устройство содержит коммутирующий элемент, выход (п-1)-го разряда приемного регистра через н. 3. «перекидной контакт ком.мутирую-щего элемента соединен со входом первого разряда приемного регистра, через н. р. перекидной контакт KOiMмутирующего элемента -

со, 1входом П.-ГО разряда приемного регистра

н через замкнутый контакт - с выходом п-го

разряда приемного регистра.

Коды, образованные квадратичными вычета1ми, .являются разновидностью кодо1В Плоткина. Свойства квадратичных вычетов ло модулю простого числа р 1поз1воляют строить нелинейные коды, обладающие большой корректирующей спосо1бностью. Рассмотрим код, образованный квадратичными вычетами по модулю npQCTOiro числа . В этом случае числа 1, 3, 4, 5, 9 являются квадрагичнымн вычета1ми, а числа 2, 6, 7, 8, 10 - невыяетами. Квадратичные вычеты, а также мисло

определяют номера позиций символов «1 ,в исходном векторе длины , т. е. 10111000101. Остальные векторы длины п-1 находят трансляцией символов вдоль последов ат ел ьн о ст и:

10111000101

11011100010 01101110001

01110001011 Кодовые векторы длины п р-{-1 12 получают из найденных путем стрипи-сьпв айия ипра1ва € M:BOvioiB «О. Учитывая, что к коду прииадлежит нулевой .вектор, получим двенадцать иооДОвых векторов, образующих п-ервО|е подмножество:

000000000000

ilOlllOOOlOlO

110111000100 {)

011011100010

011100010110

Кодовые еакторы (второго 1подмнож1е ства получают из вектОров первого подмножества {) пу|Тем 1при1бавлеиия к ним по М|0дулю два единичного вактора 111 1, а именно

111111111111

010001110101

001,000111011 ()

100100011101

100011101001

Подмножества (} и () задают код, который содержит 24 двенадцатиразрядных вектора .С минимальным кодовым расстоянием, ра1В(нЫ|М 6. Полунеиный -код является «елииейным.

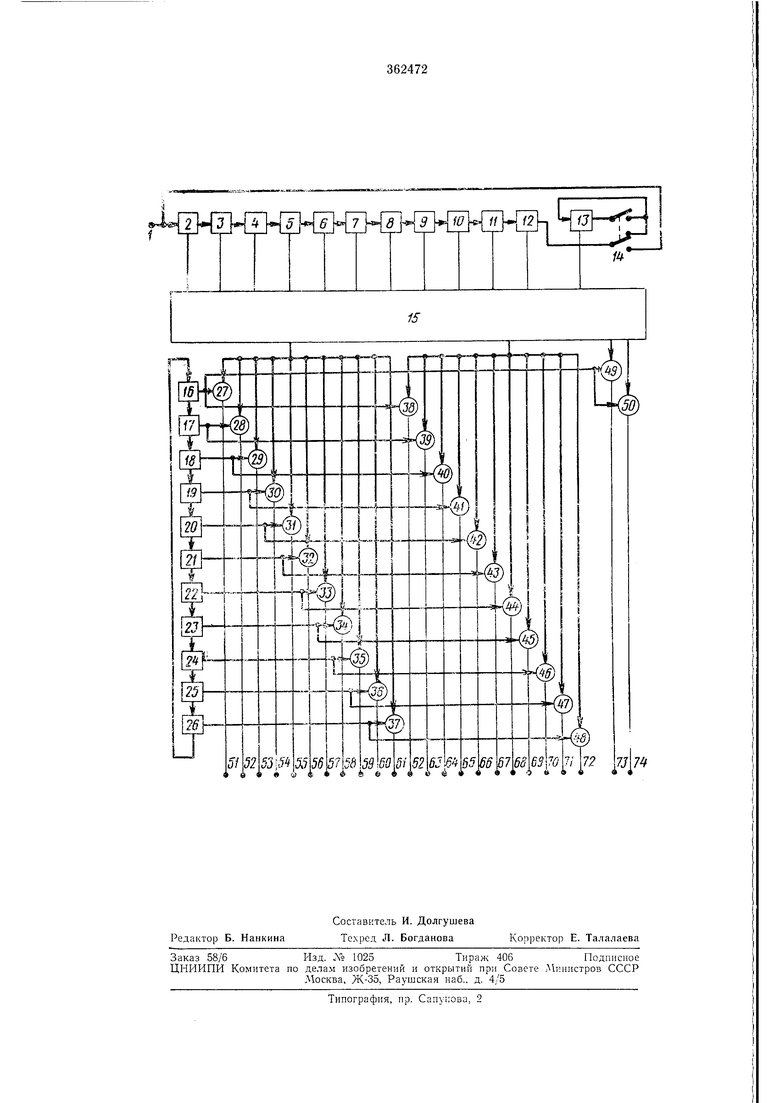

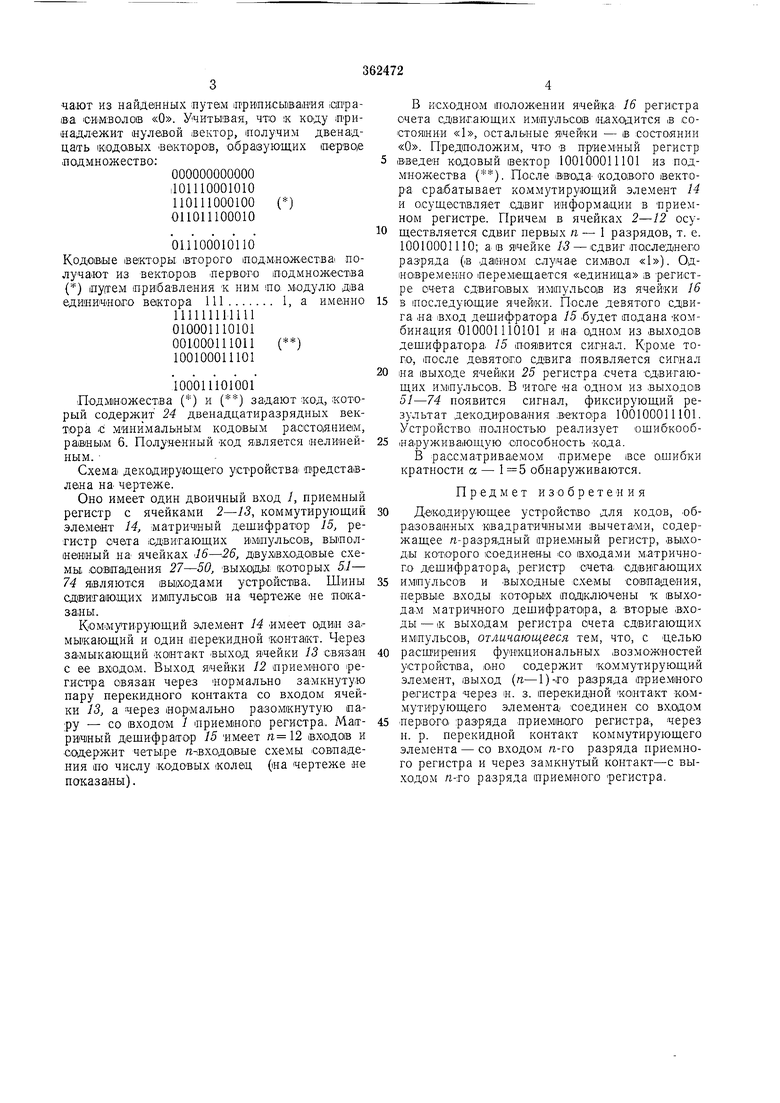

Схема декодирующего устройства представлена на чертеже.

Оно имеет один двоичный вход /, приемный регистр с ячейками 2-13, коммутирующий элемент 14, матричный дешифратор 15, регистр счета сдвигающих импульсов, выполиенный на ячейках 16-26, двух/входовые схемы .совпадения 27-50, выходы которых 57- 74 являются выводами устройства.. Шины сдвитающих импульсов на чертеже не поасазаны.

Ком:мути.рующий элем.ент 14 имеет один за.мыкающий и один перекидной контакт. Через за.мыка.ющий контакт выход ячейки 13 связан с ее вх1одо,м. Выход ячейки 12 приемного регист ра связан через нормально замкнутую пару перекидного контакта со входом ячейки 13, а через нормально разомкнутую пару - со входом 1 приемного регистра. Матриганый дешифратор 15 имеет входо1В и .содержит четыре п- входо|вые схемы Совпадения но числу кодовых колец (на чертеже не показаны).

В исходном положении ячейка 16 регистра счета сдвигающих импульсов находится в состоянии «1, остальные ячейки - в состО|Янии «О. Предположим, что в приемный регистр

введен кодовый вектор 100100011101 из по.дмноЖества (). После ввода кодового BieKToРа срабатывает коммутирующий элемент 14 и осуществляет ,сд1виг информации в приемном регистре. Причем в ячейках 2-12 осуществляется сдвиг первых п - 1 разрядов, т. е. 10010001110; а IB ячейке 13 - сдвиг последнего разряда (iB .данном случае символ «1). Однов.ремен1но перемещается «единица в регистре очета сдвиГОвых и мпульсов из ячейки 16

в последующие ячейки. Йосле девятого сдвига на вход дешифратора 15 ,будет по.дана комбина.ция .010001110101 и на однол из выходов дешифра.тора 15 появится сигнал. Кроме того, после девятого сдвига появляется сигнал

на выходе ячейки 25 регистра .счета сдвигающих импульсов. В итоге на о.дном из выходов 51-74 появится сигнал, фиксирующий результат .декодирования .вектора 100100011101. Устройства полностью реализует ошибкообна.руживаю.щую .способность кода.

В ра.ссматривасмом примере все ощибки кратности а - обнаруживаются.

Предмет изобретения

Декодирующее устройство для кодов, образованных квадратичными вычетами, содержа.щее га-разрядный приемный регистр, вьиходы которого соединены со 1В.хо.дами м.атричного дешифратора, регистр счета, сдвигающих

импульсов и выходные схемы сов;падения, первые .входы которых 1под|ключены к выхода.м матричного дешифра.тора, а вторые входы-к выходам регистра очета сдвигающих импульсов, отличающееся тем, что, с целью

расширения функциональных возможностей устройства, оно содержит коммутирую.щи.й эле;мент, выход (п-1)-го разряда приемного реги1стра через IH. з. перекидной к.онтакт коммутирующего элемента- соединен со входом

первого разряда приемного регистра., через н. р. перекидной контакт коммутирующего элемента - со входом га-го разряда приемного регистра и через замкнутый контакт-с выХО.ДОМ га-го разряда приемного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОДИНОЧНЫХ ОШИБОК | 1973 |

|

SU363979A1 |

| Логическое запоминающее устройство | 1976 |

|

SU610174A1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| ВСЕСОЮЗНАЯ I | 1971 |

|

SU304582A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU265186A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ДЛЯ ЦИКЛИЧЕСКИХ | 1970 |

|

SU261460A1 |

| Устройство для перестановочного декодирования циклических кодов | 1973 |

|

SU552716A1 |

| Логическое запоминающее устройство | 1977 |

|

SU733024A1 |

| СПОСОБ ТРАНСЛЯЦИОННОГО УСЛОЖНЕНИЯ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ В ВИДЕ КОДОВ КВАДРАТИЧНЫХ ВЫЧЕТОВ, СУЩЕСТВУЮЩИХ В ПРОСТЫХ ПОЛЯХ ГАЛУА GF(p), И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2669506C1 |

| ДЕШИФРАТОР КОРРЕКТИРУЮЩЕГО КОДА В КАНАЛЕ | 1971 |

|

SU308509A1 |

Авторы

Даты

1973-01-01—Публикация