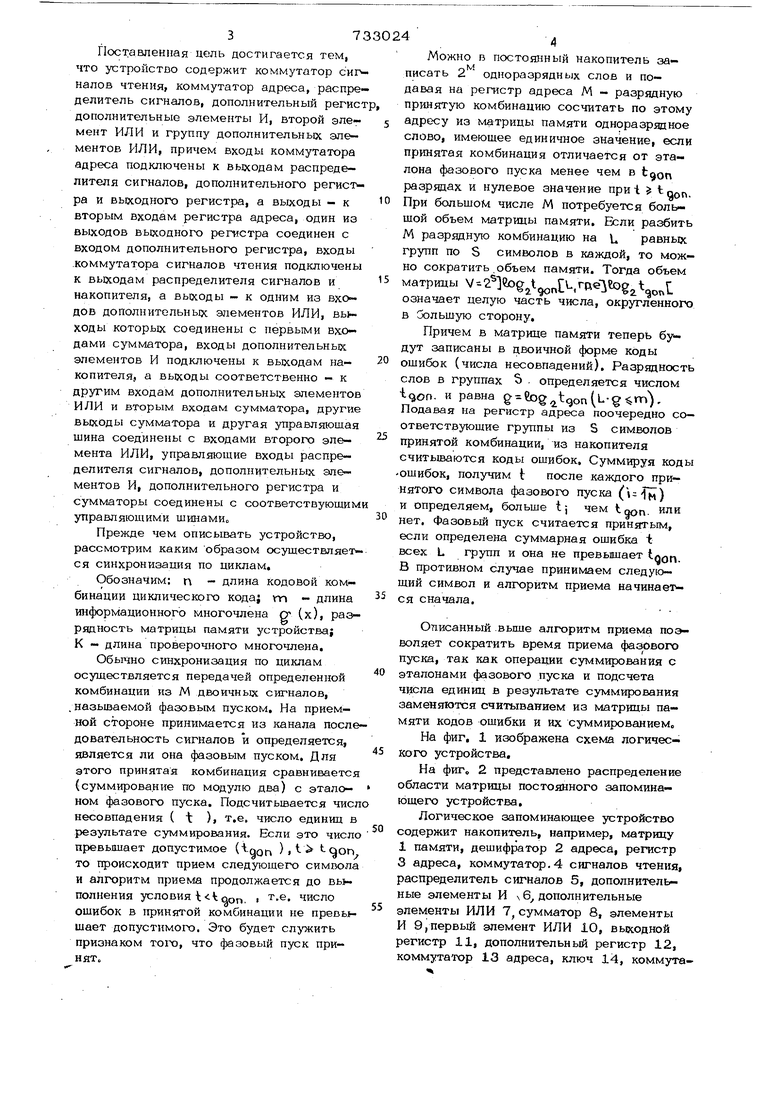

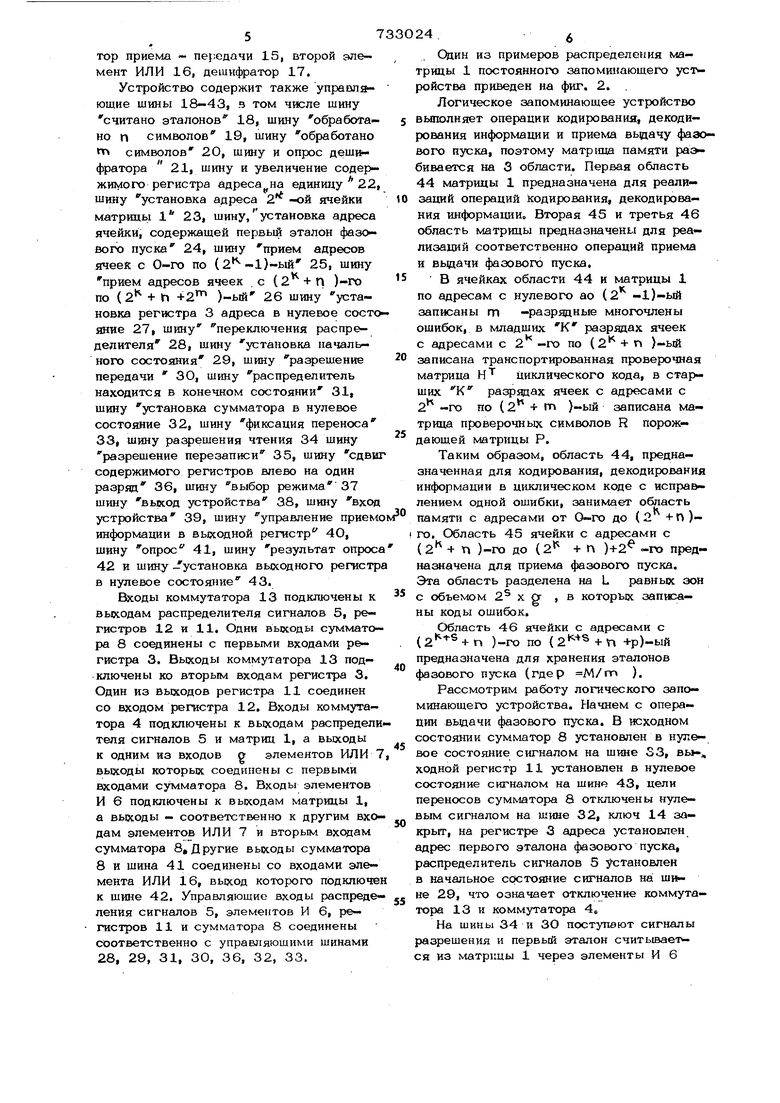

Изобретение относится к запоминающим устройствам. Известно запоминающее устройство, содержащее блоки памяти, каждый из которьвс кранит определенное количество .одноразрядных слов и включает в себя блок дещифрации адреса, регистра слова, управляющие логические блоки, сдвига- тель, элементы И прямого чтения , элементы И чтения содержимого ячейки памяти на счетные входы регистра слова элементы И чтения старшего разряда ячейки памяти на младший разряд регистра слова , блок анализа содержимого регистра слова ij . Недостатком этого запоминающего уст ройства являет низкое бьстродействие при реализации операций как кодировани5 декодирования, так и приема и вьщачи фазового пуска.. Из известных устройств наиболее близ ким по технической сущности к данному. изобретению является логическое запоминающее устрюйство, содержащее последовательно соединенные регистр адреса, дещифратор адреса и накопитель, дополнительный дешифратор, соединенный с регистром адреса, первые входы которого соединены с одними из выходов сумматора, элементы И, первые входы коюрых подключены к выходам сумматора, вторые- к одной из управляющих шин, а выходы - к входам выходного регистра, ключ, соединенный с выходным регистром, коммутатор приема-вьщачи, выход которого подключен к одному из входов первого элемента ИЛИ, выход которого соединен с управляющим входом дешифратора адреса 2 . Недостатком известного устройства является невозможность выполнения в нем операций синхронизации по циклам. Целью изобретения является расширение области применения устройства за счет обеспечения возможности выполнения в нем операций синхронизации по циклам. 373 Поставленная цель достигается тем, что устройство содержит коммутатор сигналов чтения, коммутатор адреса, распределитель сигналов, дополнительный регист дополнительные элементы И, второй элемент ИЛИ и группу дополнительных элементов ИЛИ, причем вкодЫ коммутатора адреса подключены к выходам распределителя сигналов, дополнительного регистра и выходного регистра, а выходы - к вторым входам регистра адреса, один из выходов выходного регистра соединен с входом дополнительного регистра, входы .коммутатора сигналов чтения подключены к выходам распределителя сигналов и накопителя, а выходы - к одним из входов дополнительных элементов ИЛИ, выходы которых соединены с первыми входами сумматора, входы дополнительных элементов И подключены к выходам накопителя, а выходы соответственно - к другим входам дополнительных элементов ИЛИ и вторым входам сумматора, другие выходы сумматора и другая управляющая шина соединены с входами второго элемента ИЛИ, управляющие входы распределителя сигналов, дополнительных элементов И, дополнительного регистра и сумматоры соединены с соответствующим управляющими шинами Прежде чем описывать устройство, рассмотрим каким образом осуществляется синхронизация по циклам. Обозначим; п - длина кодовой комбинации циклического кода; m - длина информационного многочлена О (х), разрядность матрицы памяти устройства; К - длина проверочного многочлена. Обычно синхронизация по циклам осуществляется передачей определенной комбинации из М двоичных сигналов, .называемой фазовым пуском. На приемной стороне принимается из канала после довательность сигналов и определяется, является ли она фазовым пуском. Для этого принятая комбинация сравнивается (суммирование по модулю два) с эталоном фазового пуска, Подсчитьшается чис несовпадения ( t ), т,е, число единиц в результате суммирования. Если это числ превышает допустимое (доп ) Д -9° то происходит прием следующего символа и алгоритм приема продолжается до вь полнения условия . число ошибок в принятой комбинации не превь шает допустимого. Это будет служить признаком TO1XI, что фазовый пуск принят. Можно в постоянный накопитель записать 2 одноразрядных слов и подавая на регистр адреса М - разрядную принятую комбинацию сосчитать по этому адресу из матрицы памяти одноразрядное слово, имеющее единичное значение, если принятая комбинация отличается от эталона фазового пуска менее чем в разрядах и нулевое значение при tgon. При большом числе М потребуется большой объем матрицы памяти. Если разбить М разрядную комбинацию на U равных групп по S символов в каждой, то можно сократить объем памяти. Тогда объем матрицы V--2 1 og tgo u;rReitog tg t означает целую часть числа, округленного в Схэльшую сторону. Причем в матрице памяти теперь будут записаны в двоичной форме коды ошибок (числа несовпадений). Разрядность слов в группах S . определяется числом . и равна g tog,j, (L-g ш). Подавая на регистр адреса поочередно соответствующие группы из S символов принятой комбинации, из накопителя считьшаются коды ошибок. Суммируя коды ошибок, получим t после каждого принятого символа фазового пуска {«-Тй) и определяем, больше tj чем t нет. Фазовый пуск считается принятым, если определена суммарная ощибка t всех L групп и она не превышает tgon. В противном случае принимаем следующий символ и алгоритм приема на чинается сначала. Описанный .выше алгоритм приема поэволяет сократить время приема фазового пуска, так как операции суммирования с эталонами фазового пуска и подсчета числа единиц в результате суммирования заменяются считыванием из матрицы памяти кодов ошибки и их суммированием. На фиг, 1 изображена схема логического устройства. На фиГо 2 представлено распределение области матрицы постоянного запоминающего устройства. Логическое запоминающее устройство содержит накопитель, например, матрицу 1 памяти, дешифратор 2 адреса, регистр 3 адреса, коммутатор.4 сигналов чтения, распределитель сигналов 5, дополнительные элементы И 6 дополнительные элементы ИЛИ 7, сумматор 8, элементы И 9,первый элемент ИЛИ 10, выходной регистр 11, дополнительный регистр 12, коммутатор 13 адреса, ключ 14, коммутатор приема - передачи 15, второй элемент ИЛИ 16, дешифратор 17. Устройство содержит также управляющие шины 18-43, в том числе шину считано эталонов 18, шину обработано п символов 19, шину обработано fn символов 20, шину и опрос деш фратора 21, шину и увеличение содержимого регистра адреса на единицу 22 шину установка адреса 2 ой ячейки матрицы 1 23, шину,установка адреса ячейки, содержащей первый эталон фазового пуска 24, шину прием адресов ячеек с 0-го по ()-ый 25, шину прием адресов ячеек с (2 + П )-го по (2 + h +2 )-ый 26 шину установка регистра 3 адреса в нулевое сост яние 27, шину переключения распределителя 28, шину установка начального состояния 29, шину разрешение передачи 30, шину распределитель находится в конечном состоянии 31, шину установка сумматора в нулевое состояние 32, шину фиксация переноса 33, шину разрешения чтения 34 шину разрешение перезаписи 35, шину сдви содержимого регистров влево на один разряд 36, шину выбор режима 37 вькод устройства 38, шину вход устройства 39, шину управление прием информации в выходной регистр 40, шину опрос 41, шину результат опрос 42 и шину - установка выходного регистр в нулевое состояние 43. Входы коммутатора 13 подключены к вькодам распределителя сигналов 5, регистров 12 и 11. Одни выходы суммато ра 8 соединены с первыми входами регистра 3. Выходы коммутатора 13 подключены ко вторым входам регистра 3. Один из выходов регистра 11 соединен со входом регистра 12. Входы коммутатора 4 подключены к выходам распредел теля сигналов 5 и матриц 1, а выходы к одним из входов о элементов ИЛИ выходы которых соединены с первыми входами сумматора 8. Входы элементов И 6 подключены к выходам матрицы 1, а выходы - соответственно к другим вхо дам элементов ИЛИ 7 и вторым входам сумматора 8, Другие выходы сумматора 8 и шина 41 соединены со входами элемента ИЛИ 16, выход которого подключе к шине 42. Управляющие входы распреде ления сигналов 5, элементов И 6, ре- гистров 11 и сумматора 8 соединены соответственно с управляющими шинами 28, 29, 31, 30, 36, 32, 33. 246 Один из примеров распределения матрицы 1 постоянного запомииаюшего yci ройства приведен на фиг. 2. . Логическое запоминающее устройство выполняет операции кодирования, декодирования информации и приема вьцачу фазового пуска, поэтому матртщ памяти разбивается на 3 области. Первая область 44 матрицы 1 предназначена для реали- заций операций кодирования, декодирования информации. Вторая 45 и третья 46 область матрицы предназначены для реализаций соответственно операций приема и вьщачи фазового пуска. В ячейках области 44 и матрицы 1 по адресам с нулевого ао (2 -1)-ый записаны m -разряднью многочлены ошибок, в младших К разрядах ячеек с адресами с 2 -го по (2 + п )-ый записана транспортированная проверочная матрица Н циклического кода, в старших К разрядах ячеек с адресами с 2 -го по (2 m }-ый записана ма- трица проверочных символов R порождающей матрицы Р. Таким образом, область 44, предназначенная для кодирования, декодирования информации в циклическом коде с исправлением одной ошибки, занимает область памяти с адресами от О-го до (2 +П)го. Область 45 ячейки с адресами с (2 + г )-го до (2 + П )+2 -го предназначена для приема фазового пуска. Эта область разделена на L равных зон с объемом 2 X. , в которьк записаны коды ошибок. Область 46 ячейки с адресами с ( + п )-го по { + П +р)-ый предназначена для хранения эталонов фазового пуска (гдер М/гг ). Рассмотрим работу логического запоминающего устройства. Начнем с операции выдачи фазового пуска. В исходном состоянии сумматор 8 установлен в нулевое состояние сигналом на шине 33, , ходной регистр 11 установлен в нулевое состояние сигналом на шине 43, цели переносов сумматора 8 отключены нулевым сигналом на шине 32, ключ 14 закрьпг, на регистре 3 адреса установлен адрес первого эталона фазового пуска, распределитель сигналов 5 установлен в начальное состояние сигналов на шине 29, что означает отключение коммутатора 13 и коммутатора 4. На шины 34 и ЗО поступают сигналы разрешения и первый эталон считывает. я из матрицы 1 через элементы И 6 на сумматор 8, На Ш1шу 35 поступает управляющий сигнал, и содержимое сумматора 8 через элементы И 9 перепись вается в выходной регистр 11, На шину 36 поступает сигнал и содержимое стар шего разряда выходного регистра 11 поступа:ет на шину 38. Подсчет числа вьцанных символов с выходного регистра 11 происходит следующим образом. Регистр 3 адреса устанавливается в нулевое состояние подачей сигналов на шину 27. На шину 22 подаются сигналы счета Проверка количества вьианных символов производится опросом дешифратора 17 при подаче сигналов на шину 21. На шине 20 появляется единичный сигнал, если вьдано m символов фазового пуска. При передаче последуюших эталонов фазового нуска на регистре 3 адреса уста навливается адрес 1 эталона и программным путем производится модификация адреса. Число вьщанных эталонов определяется опросом дешифратора 17 (на шине 18 появляется единичный сигнал, если вьщаны все эталоны). Аналогично рассмотрим операцию пр№ема фазового пуска. В исходном состоянии ключ 14 открыт, сумматор 8 устано лен внулевое состояние, цепи переноса подключены и сумматор 8 вьшолняет рол арифметического сум.матора, распредели тель сигналов 5 установлен в начальное состояние, коммутатор 15 отключен. Подачей сигнала на шину 28 распределитель сигналов устанавливается в первое положение. На шину 3fc подается сигнал и содержимое регистров 11 и 12 сдвигается влево на один разряд. На шину 4О поступает сигнал и символ информации поступает по шине 39 и через .ключ 14 записывается в младший разрад выходного регистра 11.,Коммутатор 13 адреса подключает выходы регистра 12 (распределитель 5 в первом состоя ии) к входам регистра 3 адреса. На шину 26 подается сигнал и содержимое первой группы из S - разрядов регистра 12 переписывается в регистр 3 адреса. При подаче на шину 34 сигнала из матр цы 1 считается код ошибки и через коммутатор 4, установленный в первое сос тояние, через элементы ИЛИ 7 поступае на счетные входы сумматора 8. Производится опрос элемента ИЛИ 16 подачей сигнала на шину 41. При нулевом сш иале на шине 42, т.е. ошибка меньше допустимой, производится опрос следующих разрядов репютров 12 и 11. Для этого распределитель сигналов 5 устанавливается в следуюшее состояние подачей сигнала на шину 28. Коммутатор 13 подключает выходы следуюшей группы разрядов регистров 12 и 11 и осушествляется проверка числа ошибок в этой группе, как это было показано выше, суммарная ошибка {. накапливается в сумматоре 8. Процесс приема фазового пуска продолжается до окончания просмотра всей группы разрядов регистра 12 и 11, единичньй сигнал на шине 31, при условии, что суммарная ошибка не превышает числа допустимых ошибок tgon , т.е. нал, чие нулевого сигнала на шине 42. Если в процессе обработки на шине 42 появится единичный сигнал, т.е. число ошибок превьюит допустимое, то алгоритм приема фазового пуска начинается с самого начала . . Выполнение операций кодирования, де- кодирования информации в циклическом коде подробно изложено в (Ц). Кратко опишем выполнение операции кодирования информации в циклическом коде данным логическим запоминающим устройством, ддя получения комбинации циклического кода нужно умножить строки матрицы проверочных символов R, порождающей матрицы на коэффициенты информационного многочлена п (х) и результаты произведений сложить. в исходном состоянии коммутатор 15 находится в положении вьдача, ключ 14 закрыт, в регистре 3 адреса установлен 2 -ой ячейки матрицы 1, сумматор 8 установлен в нулевое состояние, цепи переноса отключены, в выходном регистре 11 записана информационная последовательность, распределитель сипналов 5 установлен в начальное положение, На шину 36 подается сигнал и содержимое регистров 12 и 11 сдвигается влево на один разряд, и символ информационной последовательности поступает на шину 38 и одновременно через коммутатор 15 и.элемент ИЛИ 10 на вход дешифратора 2 и если символ единичный, то из матрицы 1 считьшается один из многочленов проверочных символов порождающей матрицы и через элементы И 6 (на шине ЗО-единичньш сигнал) запись, вается в сумматор 8, На шину 21 подается сигнал и проверяется условие вьдачи т информационных символов из выход- 9 но го регистра 11, о чем будет сеидетел ствовать сигнал на шине 20, Если вьда меньше m символов, то есть на шине 20 отсутствует сигнал, то содержимое регистра 3 адреса увеличивается на единицу, для этого на шину 21 подается сигнал и далее нродолжается вьщача информационных символов из выходного р& гистра 11 и считьшания многочленов про верочньк символов из матрицы 1, котор суммируются по модулю два с содержим сумматора 8. Бели вьвдано m символов, то на шине 20 появляется сигнал, то ес из выходного регистра 11 будет вьщана вся информационная последовательность, а в сумматоре 8 будет записан многочлен проверочных символов кодовой последовательности На шину 35 поступает сигнал.и многочлен проверочных символов переписывается через элемент И 9 в выходной регистр 11 из сумматора 8, причем проверочные символы заполняют К старших разрядов выходного регистра 11 а содержимое младших разрядов не имеет значения. При дальнейшем поступлении импульсов сдвига на шину 36 проверочные смиволы поступают на шину 38, Пос ле каждого такта сдвига опрашивается дешифратор 17 подачей на шину 21 сиг нала и проверяется условие вьдачи П, символов кодовой последовательности, о чем .будет свидетельствовать сигнал на шине 19. Бзли условие не выполняется , то продолжается вьщача проверочных символов, в противном случае кодирование заканчивается В описанном устройстве расширена область применения за счет операций синхронизации по циклам и, таким образом, совмещены в одном устройстве функ ции кодирование-декодирования и синхронизации по циклам. Это позволяет уменЕ шить аппаратурные затраты на 20-30% и повысить регулярность устройства. Формулаизобретения Логическое запоминающее устройство содержашее пocлeдoвiaтeльнo соединённью регистр адреса, дешифратор адреса и накопитель, дополнительньп регистр, соединенный с регистром адреса, первые 24 ,входы которого соединены с одними из выходов сумматора, элементы И, первые входы которых подключены к выходам сумматора, вторые - к одной из управляющих шин, а выходы - ко входам вь ходного регистра, ключ, соединенный с выходным регистром, коммутатор приема- вьщачи, выход которого подключен к одному из входов первого элемента ИЛИ, выход которого соединен с управляюшим входом дешифратора адреса, о т л и чающееся тем, что, с целью расширения области применения устройства за счет обеспечения возможности вьшол- нения в нем операций синхронизации по циклам, оно содержит коммутатор сигналов чтения, коммутатс адреса, распределитель сигналов, дополнительный регистр, дополнительные элементы И, второй эле- мент ИЛИ и группу дополнительных элементов ИЛИ, причем входы коммутатора адреса подключены к выходам распределителя сигналов, дополнительного регистра и выходного регистра, а вькоды - ко вторым входам регистра адреса, один из выходов выходного регистра соединен со входом дополнительного регистра, входы комкгутатора сигналов чтения подключены к выходам распределителя сигналов и накопителя, а выходы - к одним из входов дополнительных элементов ИЛИ, выходы которых соединены с первыми входами сумматора, входы дополнительных элементов И подключены к выходам накопителя, а выходы - соответственно к другим входам дополнительньк элементов ИЛИ и вторым входам сумматора, другие входы сумматора и другая управляющая шина соединены со входами второго элемента ИЛИ, управляющие входы распределителя сипшлов, дополнительных элементов И, ДОПОЛНИ ельного регистра и сумматоры соединены с соответствующими управляющими шишами , Источники информации, Припятью во внимание при экспертизе 1,Авторское свидетельство СССР № 553682, кл. О-11 С 15/ОО, 1976. 2,Авторское свидетельство СССР NO 610174, кл. О- 11 С 15/00, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| Логическое запоминающее устройство | 1976 |

|

SU610174A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для исправления стираний | 1989 |

|

SU1633498A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для редактирования информации | 1981 |

|

SU980099A1 |

Авторы

Даты

1980-05-05—Публикация

1977-12-13—Подача