1

Известны буферные запоминающие устройства для управляемой системы телесвязи с записанной программой, содержание управляющий вычислительный блок, входной и выходной регистры.

Недостаток известных устройств состоит в том, что они имеют усложненное схемное рещение применительно к режиму работы с задержкой адресации.

С целью обеспечения работы с задержкой адресации при одновременном упрощении и уменьщения требуемой емкости накопления в предлагаемое устройство включен ряд ячеек памяти, входные цени которых соединены с регистрирующим счетчиком, генератором син хронизирующих импульсов и входным регистром, а выходные цепи ячеек памяти связаны со считывающим счетчиком и выходным регистром, при этом генератор синхронизирующих импульсов соединен с одними входами первых адресных регистрирующих цепей, другие входы которых связаны с выходом регистрирующего счетчика, а выход входного регистра связан с одними входами вторых адресных регистрирующих цепей, другие входы которых соединены с выходом регистрирующего счетчика, причем каждая пара адресных регистрирующих цепей связана с соответствующей ячейкой памяти, имеющей на выходе цепь восстановления, другой вход которой связан с выходом считывающего счетчика, вход которого, в свою очередь, соединен через схему «ИЛИ с генератором синхронизирующих импульсов, причем выходы всех считывающих цепей соединены через соответствующую схему «ИЛИ с выходным счетчиком и со считывающим счетчиком

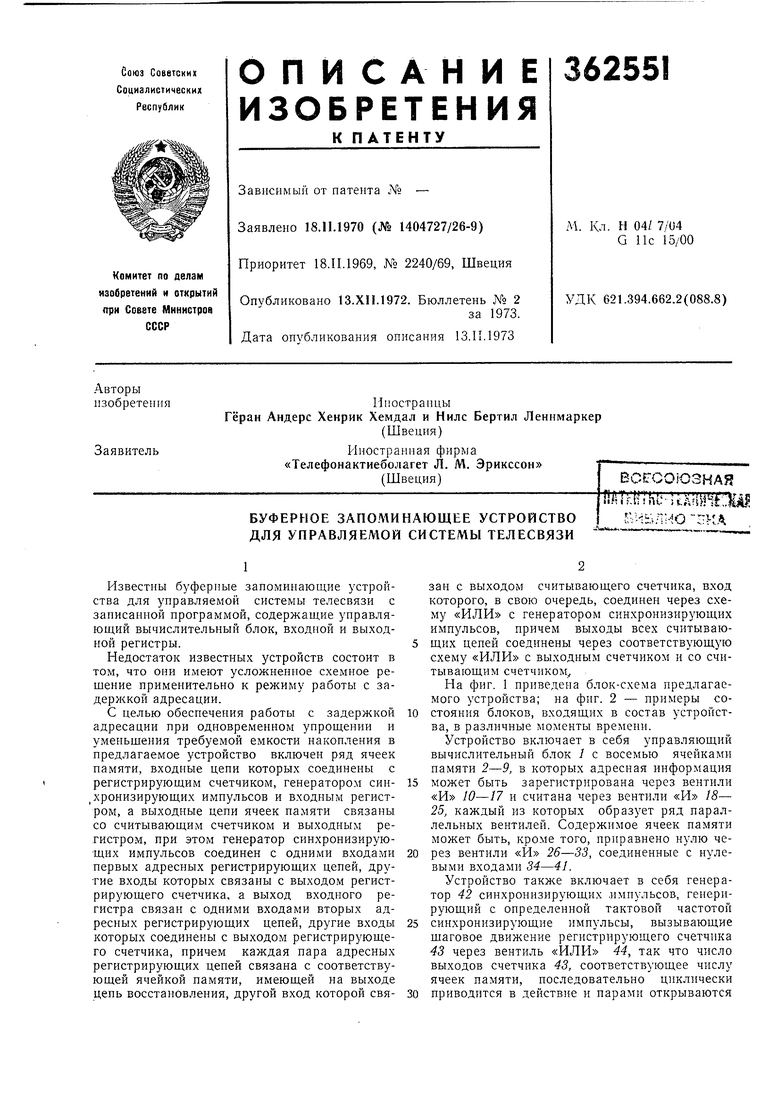

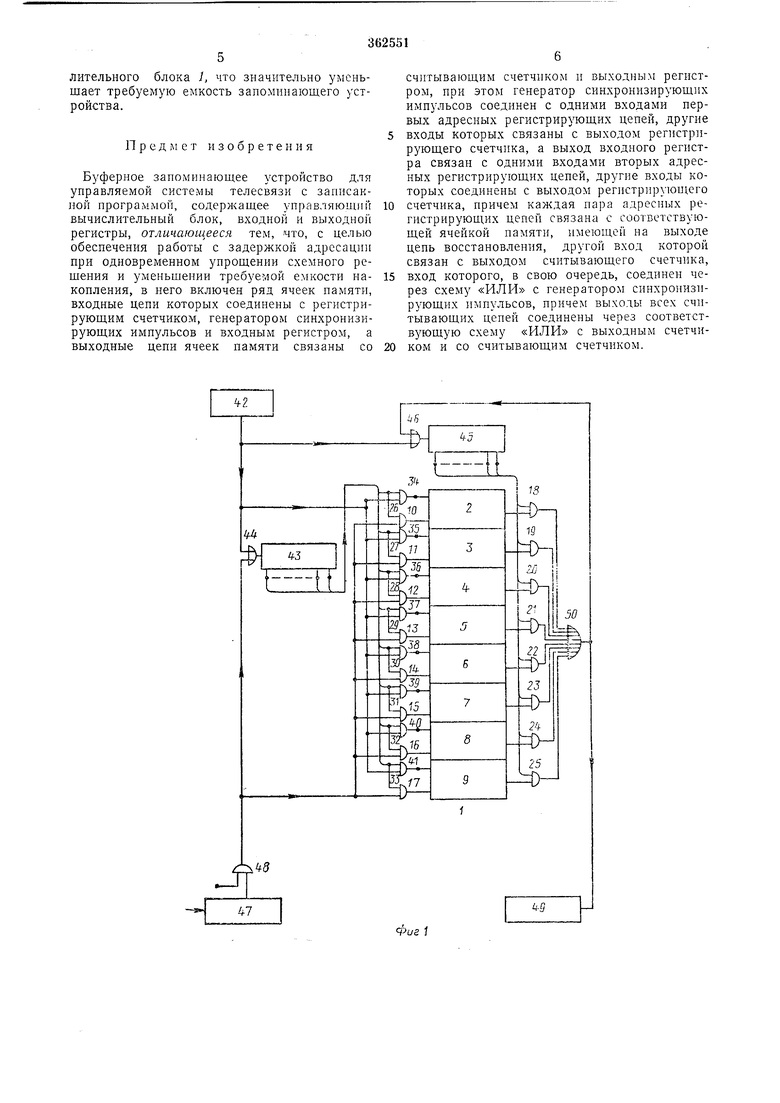

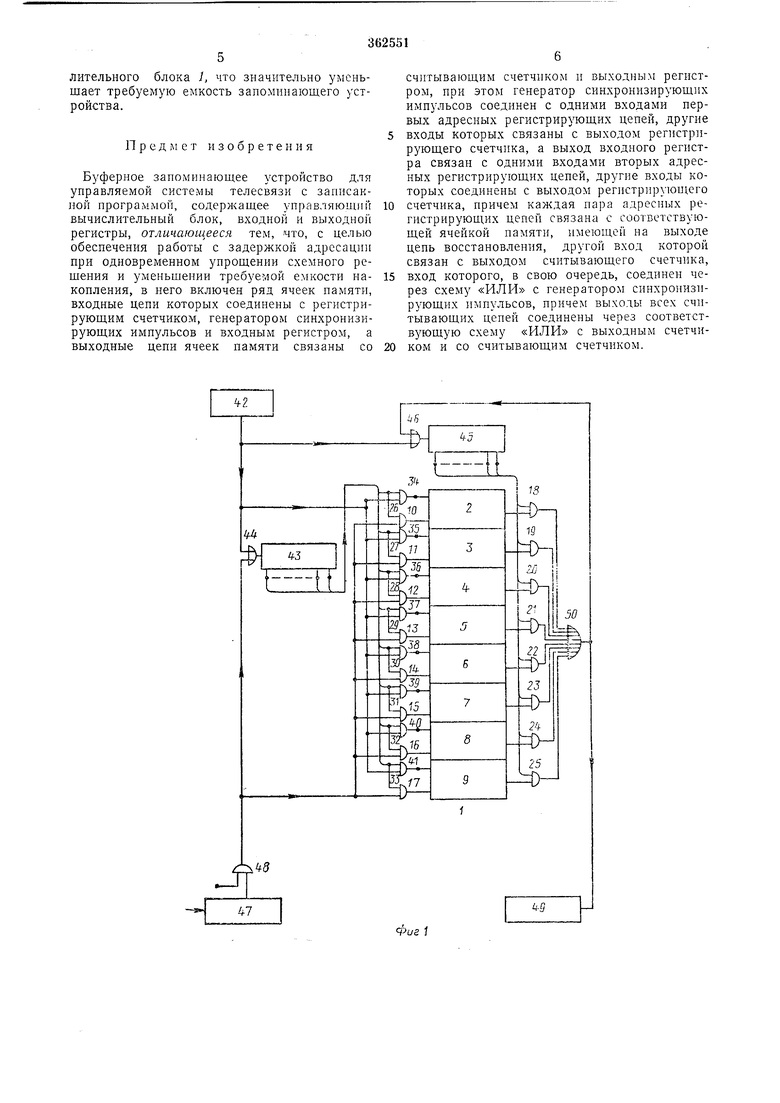

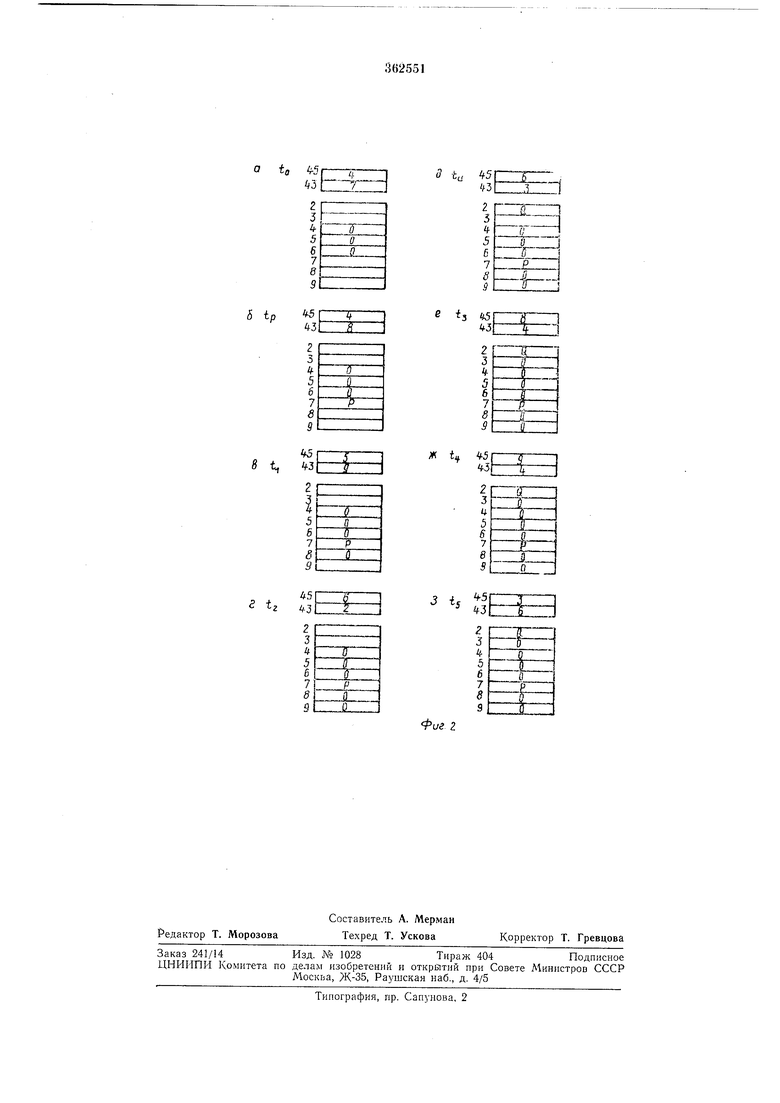

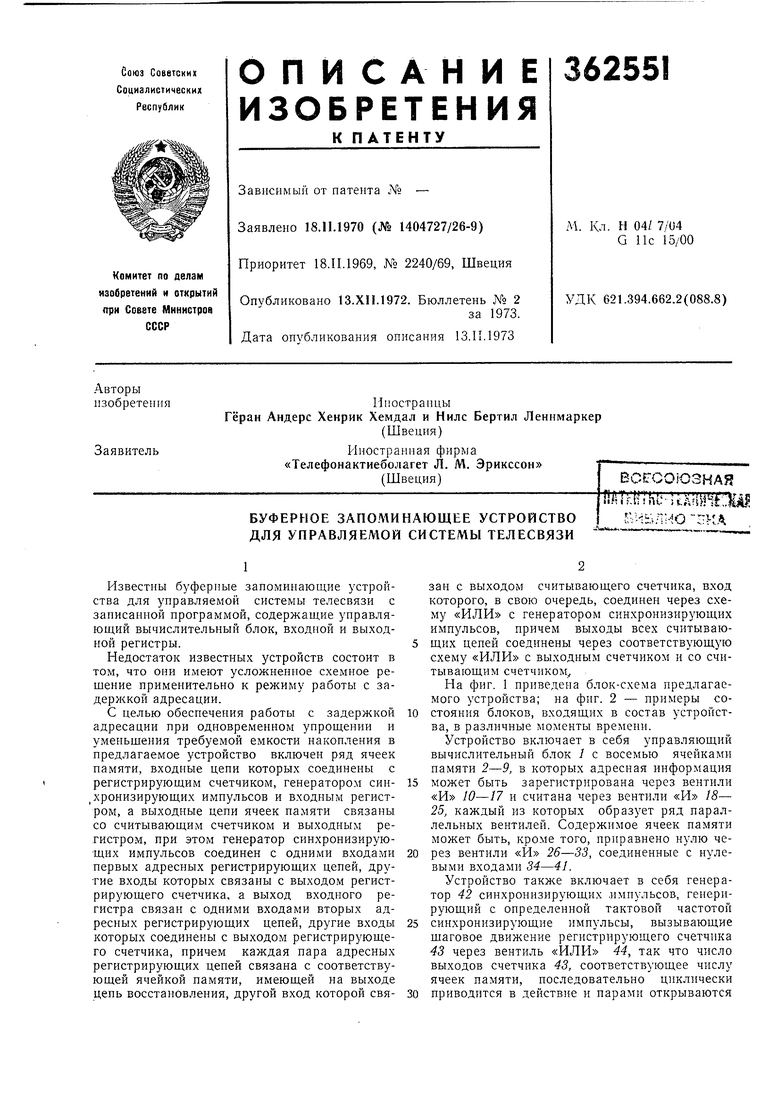

Иа фиг. 1 приведена блок-схема предлагаемого устройства; на фиг. 2 - примеры состояния блоков, входящих в состав устройства, в различные моменты времени.

Устройство включает в себя управляющий вычислительный блок 1 с восемью ячейками памяти 2-9, в которых адресная информация

может быть зарегистрирована через вентили «И 10-17 и считана через вентили «И 18- 25, каждый из которых образует ряд параллельных вентилей. Содержимое ячеек памяти может быть, кроме того, приравнено нулю через вентили «И 26-33, соединенные с нулевыми входами 34-41.

Устройство также включает в себя генератор 42 синхронизирующих .импульсов, генерирующий с определенной тактовой частотой

синхронизирующие импульсы, вызывающие щаговое движение регистрирующего счетчика 43 через вентиль «ИЛИ 44, так что число выходов счетчика 43, соответствующее числу ячеек памяти, последовательно циклически

приводится в действие и парами открываются

вентили 10-17 и 26-33, кроме того, генерирующие синхронизирующие импульсы вызывают щаговое движение считывающего счетчика 45 через вентиль «ИЛИ 46, в результате чего циклически приводятся в действие выходы считывающего счетчика 45 и открываются вентили «И 18-25. Генератор 42 синхронизирующих импульсов также соединяется с одним входом вентилей «И 26-33, соединенных с нулевыми входами 34-41 ячеек памяти 2-9, тем самым синхронизирующий импульс устанавливает ячейку памяти, указанную регистрирующим счетчиком 43, в нулевое состояние.

Другой вход вентилей 10-17 соединяется с выходом входного регистра 47 через вентиль «И 48, в результате адресная информация может быть зарегистрирована от регистра в ячейке памяти, указанной регистрирующим счетчиком 43. Эта адресная информация состоит из нескольких двоичных чисел, которые передаются через ряд параллельных проводников и вентилей, представленных на фиг. 1 одним вентилем и одним проводником, та.кже соединенным с другим входом вентиля «ИЛИ 44, и регистрация адресной информации вызывает щаговое перемещение регистрирующего счетчика 43. Выходы вентилей 10-17 соединяются с выходным регистром 49 через вентиль.«ИЛИ 50. В выходном регистре 49 адреса, зарегистрированные от входного регистра, могут быть иереданы с определенной задержкой. Выходы вентилей 10-17 соединяются с другим входом вентиля «ИЛИ 46, тем самым считывание адреса вызывает щаговое продвижение считывающего счетчика 45.

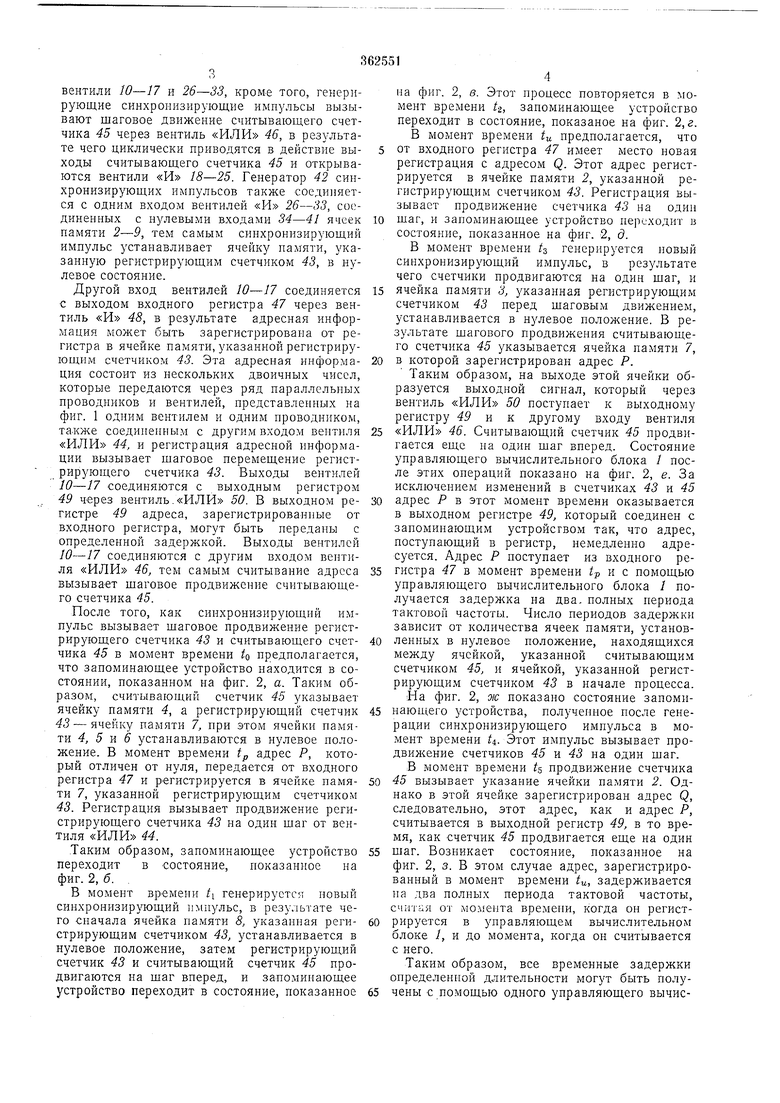

После того, как синхронизирующий имцульс вызывает щаговое продвижение регистрирующего счетчика 43 и считывающего счетчика 45 в момент времени /о предполагается, что запоминающее устройство находится в состоянии, показанном на фиг. 2, а. Таким образом, считывающий счетчик 45 указывает ячейку памяти 4, а регистрирующий счетчик 43 - ячейку памяти 7, при этом ячейки памяти , 5 и 5 устанавливаются в нулевое положение. В .момент времени tp адрес Р, который отличен от нуля, передается от входного регистра 47 и р егистрируется в ячейке памяти 7, указанной регистрирующим счетчиком 43. Регистрация вызывает продвижение регистрирующего счетчика 43 на один шаг от вентиля «ИЛИ 44.

Таким образом, запоминающее устройство переходит в состояние, показанное на фиг. 2, б. ,

В момент времени ti генерируется новый синхронизирующий имнульс, в результате чего сначала ячейка памяти 8, указанная регистрирующим счетчиком 43, устанавливается в нулевое положение, затем регистрирующий счетчик 43 и считывающий счетчик 45 продвигаются на шаг вперед, и запоминающее устройство переходит в состояние, показанное

на фиг. 2, в. Этот процесс повторяется в момент времени /а, запоминающее устройство переходит в состояние, показаное на фиг. 2, г.

В момент времени tu предполагается, что от входного регистра 47 имеет место новая регистрация с адресом Q. Этот адрес регистрируется в ячейке памяти 2, указанной регистрирующим счетчиком 43. Регистрация вызывает продвижение счетчика 43 на один шаг, и запоминающее устройство перс-ходит в состояние, показанное на фиг. 2, д.

В момент времени /з генерируется новый синхронизирующий импульс, в результате чего счетчики продвигаются на один щаг, и ячейка памяти 3, указанная регистрирующим счетчиком 43 перед шаговым движением, устанавливается в нулевое положение. В результате шагового продвижения считывающего счетчика 45 указывается ячейка памяти 7, в которой зарегистрирован адрес Р.

Таким образом, на выходе этой ячейки образуется выходной сигнал, который через вентиль «ИЛИ 50 поступает к выходному регистру 45 и к другому входу вентиля «ИЛИ 46. Считывающий счетчик 45 продвигается еще па один шаг вперед. Состояние управляющего вычислительного блока / после этих операций показано на фиг. 2, е. За исключением изменений в счетчиках 43 и 45 адрес Р в этот момент времени оказывается в выходном регистре 49, который соединен с запоминающим устройсгвом так, что адрес, поступающий в регистр, немедленно адресуется. Адрес Р поступает из входного регистра 47 в момент времени р и с помощью управляющего вычислительного блока / получается задержка на два, полных периода тактовой частоты. Число периодов задержки зависит от количества ячеек памяти, установленных в нулевое положение, находящихся между ячейкой, указанной считывающим счетчиком 45, и ячейкой, указанной регистрирующим счетчиком 43 в начале процесса.

На фиг. 2, ж показано состояние запоминающего устройства, полученное после генерации синхронизирующего импульса в момент времени t. Этот импульс вызывает продвижение счетчиков 45 и 43 па один шаг.

В момент времени ts продвижение счетчика 45 вызывает указание ячейки памяти 2. Однако в этой ячейке зарегистрирован адрес Q, следовательно, этот адрес, как и адрес Р, считывается в выходной регистр 49, в то время, как счетчик 45 продвигается еще на один щаг. Возникает состояние, показанное на фиг. 2, 3. В этом случае адрес, зарегистрированный в момент времени tu, задерживается на два полных периода тактовой частоты, считая от вре.мепи, когда он регистрируется в управляющем вычислительном блоке /, и до момента, когда он считывается с него.

Таким образом, все временные задержки определенной длительности могут быть получены с помощью одного управляющего вычислительного блока /, что значительно уменьшает требуемую емкость запоминающего устройства.

Предмет и з о б р е т е н н я

Буферное запоминающее устройство для управляемой системы телесвязи с записанной программой, содержащее управляюпип вычислительный блок, входной и выходной регистры, отличающееся тем, что, с целью обеспечения работы с задержкой адресации при одновременном упрощении схемного рещения и уменьщении требуемой емкости накопления, в него включен ряд ячеек памяти, входные цепи которых соединены с регистрирующим счетчиком, генератором синхронизирующих импульсов и входным регистром, а выходные цепи ячеек памяти связаны со

считывающим счетчиком и выходным регистром, при этом генератор синхронизирующих импульсов соединен с одними входами первых адресных регистрирующих цепей, другие входы которых связаны с выходом регистрирующего счетчика, а выход входного регистра связан с одними входами вторых адресных регистрирующих цепей, другие входы которых соединены с выходом регистрирующего счетчика, причем каждая пара адресных регистрирующих цепей связана с соответствующей ячейкой памяти, имеющей на выходе цепь восстановления, другой вход которой связан с выходом считывающего счетчика, вход которого, в свою очередь, соединен через схему «ИЛИ с генератором синхронизирующих импульсов, причем выходы всех считывающих цепей соединены через соответствующую схему «ИЛИ с выходным счетчиком и со считывающим счетчиком.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УПРАВЛЕНИЯ БЛОКОМ ПЕРЕДАЧИ ДВОИЧНЫХ СИГНАЛОВ В ЭЛЕКТРОННОЙ СИСТЕМЕ | 1973 |

|

SU363267A1 |

| УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU367426A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ИНФОРМАЦИОННОГО ВЗАИМОДЕЙСТВИЯ ОБЪЕКТОВ ПРОВЕДЕНИЯ ВЫБОРОВ И РЕФЕРЕНДУМОВ | 2005 |

|

RU2287188C1 |

| СИСТЕМА ПОДДЕРЖАНИЯ ИНФОРМАЦИОННОЙ ИДЕНТИЧНОСТИ ТЕРРИТОРИАЛЬНО-РАСПРЕДЕЛЕННЫХ БАЗ ДАННЫХ АВИАКОМПАНИИ | 2005 |

|

RU2291482C2 |

| Счетчик фотонов | 1988 |

|

SU1520356A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ЭЛЕКТРОННОГО ГОЛОСОВАНИЯ ГАС "ВЫБОРЫ" | 2005 |

|

RU2291483C1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА АКТИВНОГО ВИДЕО | 1999 |

|

RU2173883C2 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА УЧЕТА УЧАСТНИКОВ ГОЛОСОВАНИЯ | 2005 |

|

RU2289848C1 |

| Устройство для отображения информации | 1985 |

|

SU1328840A2 |

Фиг 1

5 ip

s t.

Авторы

Даты

1973-01-01—Публикация