(5) ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР

1

Изобретение относится к управляющим системам с программным управлением и может быть использовано для логического управления станками и автоматическими линиями.

Известен пpoгpaммиpye й контроллер, содержащий центральный процессор, программируемый блок памяти, устройство, сканирующее содержимое памяти, и функциональные блоки входных сигналов, выходных сигналов, таймеров, счетчиков неразрушаемой памяти, оперативной памяти Сканирующее устройство обеспечивает последовательный вывод кодов, содержащихся в блоке памяти и выдачу их в процессор и на функциональные блоки Л .

Недостатком его является отсутствие защиты входных цепей контроллера от дребезга контактов, помех и пропадания напряжения питания входных цепей, т.е. низкая достоверность ввода информации в процессор.

Наиболее близким техническим решением к предлагаемому является устройство программного управления, которое содержит генератор, счетчик, запоминающее устройство, процессор, се5 лекторы, дешифраторы, линейки вентилей И входных сигналов, блок формирования выходных сигналов с элементами И,

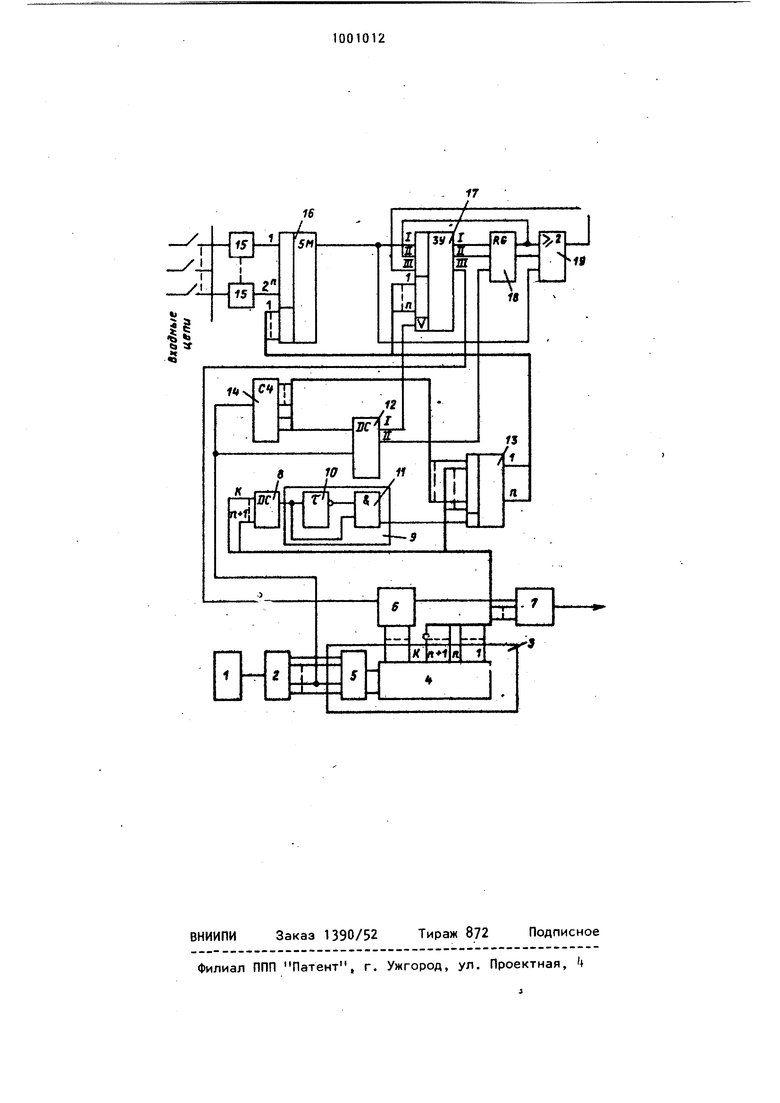

О Генератор обеспечивает счетчик тактовыми импульсамиi Счетчик формирует на выходах коды, по которым последовательно из запоминающего устройства считываются коды команд, которые по5 ступают на схему, состоящую из селекторов и дешифраторов. Эта схема обеспечивает открывание линеек вентилей И входных сигналов по командам из запоминающего устройства. Сигнал с выхо20да вентилей поступает в процессор. В зависимости от сигнала и команды, поступающей в процессор, последний формирует сигналы управления для блока 310 .. - в а f i-i л ы X о д н ы X с и г н а л с в с эле Медост/гг ком изасспог-о усройства П1 ограммного управлен1- я является отл.тслвие защиты от дребезжа контак гов, помех и пропадания нйпряжения питаг-L -1 входных цепей, т ев, низкая помехоу; ойчивесть устройства. Для устранения этого недостатка на всех входах необходимо устанавливать элементь защиты, что в целом увеличивает количество электронного оборудова ния пропорционально количеству входов устройства Liejib изобретения - повышение помехоус гой ЧИ8ОСТИ контроллера, Поставленная цель достигается теМ; а программируе№1Й контроллер, содержащий элементы согласования соединенные с входами контроллера, последовательно соединенные генерато импульсов, программный счетчик и пер вое запоминающее устройство, управляющие выходы которого подключены к вычислительному блоку, а адресные выходы -к адресным входам блока формироеателя выходных сигналов, подклю 4cH ioro информационным входом к выхо ду вычислительного блока; а выходом к выходу контроллера, введены первый второй дешифраторы, формирователь |-п-Г1ульсов , адресный счетчик, кс/ммутатор, мультиплексор, второе запомина 0iii,ee устоойстзо, регистр памяти и |ажоритарк:ый элемент, информационные входы мультиплексора соединены с выходами элементов согласования а адресные входы - с адресными вxoдa и второго запоминающего устройства и выходами коммутатора 5 первые информационные входы которого соединены с выходами всех разрядов здресного счетчика,, а вторые информаги-юннье входы - с адресными выходами п :рвого запсмиi-iaroiuero устройства и с входами первого дешифратора, выходами подключенного через формирователь импул сов к управля ощему входу коммутатора счетный вход адресного сметчика соединен с выходом одного из разрядов про граммного счетчика и с первым входом второго дешифратора, агорой вход ко торого соединен с выходом одного из разрядов адресного счетцика,, первый выход - с управляющим входом второго запоминающего устройства, а второй выход - с управляющим входом регистра памяти, подключенного информационными входами к первым выходам второ24го запоминающего устройства, ьторой выход которого соединен с информационным входом вычислительного блока, первый информационный вход - с выходом мультиплексора и одним из входов мажоритарного элемента, второй информационный -вход - с одним из выходов регистра памяти, а третий информационный зход - с выходом мажоритарного элемента, подключенного вторыми входами к выходам регистра памяти. Такойпрограммируелый контроллер обладает повышенной помехоустойчивостью, так как заключение о значении входного сигнала делается на основании трех выборок сигнала, разнесенных во 13ремени, На чертеже приведена структурная схемз контроллера. Программируемый контроллер содержит генератор 1 импульсов, программный счетчик 2, первое запоминающее устройство (ЗУ,1 3, состоящее из многоразрядных ячеек k памяти и схемы 5 выборки многоразрядных кодов, вычислительный блок 6, блок 7 формирования выходных сигналов, первый дешифратор 8, формирователь 9 импульсов, содержащий элемент 10 задержюи и элемент И 11, второй дешифратор 12, коммутатор 13, адресный счетчик 14, элементы 15 согласования, мультиплексор 16, второе запоминающее устрой ство (ЗУ) 17, регистр 18 памяти, мажоритарный элемент 19 Программируемый контроллер работает следующим образом. Генератор 1 формирует импульсы, которые с его выхода поступают на вход счетчика 2, На выходах счетчика 2 фор14ируется код, который подается на управляющие входы схемы 5, обеспечивающей выдачу содержимого из ячеек , код адреса которой установлен на входах схемы 5. Каждый следующий импульс устанавливает на выходах счетчика 2 новый адрес и так до тех пор, пока будет считано содержимое всех ячеек. Затем и,икл считывания повторяется. На выходах ЗУ 3 последовательно формируются коды команд, которые состоят из двух частей: кода адреса и кода операции. Код операции поступает на управляю1цие входы блока 6, код адреса - на адресные входы блока 7, дешифратора 8 и коммутатора 13, блок 6 реализует логическую функцию над операндом поступающим на его вход 5 с выхода второго ЗУ 17, и операндом, хранящимся в памяти вычислитель ного блока 6, в соответствии с кодом операции на его управляющих входах. Результат операции подается с выхода блока 6 в блок 7, который по .команде из ЗУ 3 принимает операнд и формирует выходной сигнал, соответствующий значению операнда на том выходе адрес которого поступает в ЗУ 3. Мультиплексор 16 обеспечивает выбор входа, номер которого соответствует коду адреса, задаваемого адресным счетчиком Н, и подключение второго двоичного сигнала к выходу мультиплексора 16, Элементы 15, например оптроны, обеспечивают развязку входных цепей контроллера и преобразование сигналов с параметрами входных цепей в сигналы с параметрами элементной базы контроллера. ЗУ 17 содержит три одинаковые строки ячеек памяти. Количество ячеек памяти в каждой строке равно количеству входных цепей (2), где п - количество разрядов в коде адреса. Номера трех ячеек памяти, в которых происходит одновременная запись или считывание информации, определяются кодом на адресных входах второго ЗУ 17. Импульс записи, поступающий с выхода 1 дешифратора 12 производит запись информации в ячейки второго ЗУ 17: в ячейку, подключенную к входу 1 - с выхода мультиплексора 1б, ячейку, подключенную к входу Г1 - с выхода первого разряда регистра 18 памяти, в ячейку, подключенную к вхо ду HI - с выхода элемента 19. Между импульсами записи ЗУ 17 работает в режиме чтения, и импульсами с выхода дешифратора 12 происходит запись в д разряда регистра 18 содержимого двух ячеек ЗУ 17. После окончания импульса записи в регистр 18 на входах элемента 19 присутствует информация о сигнале во входной цепи, полученная в три момен та времени О , Т , 2Т ,i от стоящей дру от друга на время , где Т - пе риод следования импульсов на выходах дешифратора 12, Элемент 19 передает на выход то значение сигнала, которое присутствует на боль .шинстве входов (двух или трех). В сл чае присутствия во входной цепи помехи в течение времени меньшего TQ только одно из трех значений сигнала на входе элемента 19 неверно и на 12А вход ЗУ 17 передается правильный сигнал о состоянии входной цепи, т.е. происходит селективное подавление помехи. При смене кодов на адресных входах мультиплексора 1б и ЗУ 17 сигналы о состоянии всех входных цепей после обработки в элементе 19 периодически записываются в третью строчку ЗУ 17. Передача информации из ЗУ 17 в блок 6 осуществляется под управлением специальной команды из ЗУ 3Эта команда состоит из двух полей разрядов, присутствующих на адресных выходах первого ЗУ 3: первое поле - разряды с п+1 по К-й, второе поле - разряды с 1 по п-й. Код первого поля дешифрируется первым дешифратором 8 и обеспечивает выдачу через коммутатор 13 кода адреса входа контроллера, заданного вторым полем, на адресные входы мультиплексора 16 и ЗУ 17. Формирователь 9 обеспечивает формирование импульсов по переднему фронту выходных импульсов дешифратора В, что необходимо для синхронизации момента обращения к второму ЗУ 17 с интервалом считывания указанного ЗУ. Предлагаемый программируемый контроллер обладает повышенной помехоустойчивостью, что позволяет исключить экономические потери, связанные с выходом из строя управляемых объектов или браком обрабатываемых деталей. Формула изобретения Программируемый контроллер, содержащий элементы согласования, соединенные с входами контроллера, последовательно соединенные генератор импульсов, программный счетчик и первое запоминающее устройство, управляющие выходы которого подключены к вычислительному блоку, а адресные выходы - к адресным входам блока формирования выходных сигналов, подключенного информационным входом к выходу вычислительного блока, а выходом - к выходу контроллера, отличающийся тем, что, с целью повышения помехоустойчивости контроллера, в него введены первый и второй дешифраторы, формирователь импульсов, адресный счетчик, коммутатор, мультиплексор, второе запоминающее устройство, регистр памяти и мажоритарный элемент, информационные входы мультиплексора сое7100динены с выходами элементов согласо вания, а адресные входы - с адресны ми входами второго запоминающего устройства и с выходами коммутатора, первые информационные входы которого соединены с выходами всех разрядов адресного счетчика, а вторые информационные входы - с адресными выходами первого запоминающего устройства и с входа 1 первого дешифратора, выходом под-Ю ключенного через формирователь импульсов к управляющему входу коммутатора, сметный вход адресного сметчика соединен с выходом одного из разрядов программного счетмика и с первым аходом второго дешифратора, второй вход которого соединен с выходом одного из разрядов адресного счетмика, первый выход - с управляюи|им входом второго запоминаюдего устройства, а второй вы-а 128 ход - с управляющим входом регистра памяти , подключенного информа1 ионныии входами к первым выходам второго -запоминающего устройства, второй выход которого соединен с информационным входом мультиплексора и с одним из входов мажоритарного элемента, второй ин(1юрмационный вход - с одним из выходов регистра памяти, а третий информационный вход - с выходом мажоритарного элемента, подключенного вторыми входами к выходам регистра памяти, Источники информации, принятые во внимание при экспертизе 1,Срибнер Л,А. Программируемые контроллеры, их особенности и тенденции развития - Управляющие системы и машины, 1978, № 2. 2.Патент Великобритании tf1507537, кл „ G 3 N опублик, 1978 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Устройство для опроса входов программируемого контроллера | 1989 |

|

SU1718184A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Программируемый контроллер | 1984 |

|

SU1262451A1 |

Авторы

Даты

1983-02-28—Публикация

1981-10-13—Подача