1

Изобретение относится к области электросвязи и может быть использовано в устройствах телесигнализации непрерывного действия, предназначенных для работы по стандартным каналам связи значительной протяженности.

Известен приемник телеинформации, производящий непрерывный прием многократных циклов, устройством фазирования которого служит счетчик-дешифрс гор посылки окончания миогократиого цикла, представляющий собой бинарный счетчик с коэффициентом счета 8.

С целью сокращения избыточности но служебным посылкам в приемник введен дешифрирующий блок, один из входов которого соединен с выходом входного устройства, а другой подключен к генератору стробирующих импульсов. При этом выход дешифрирующего блока соединен с коммутирующей схемой и распределителем.

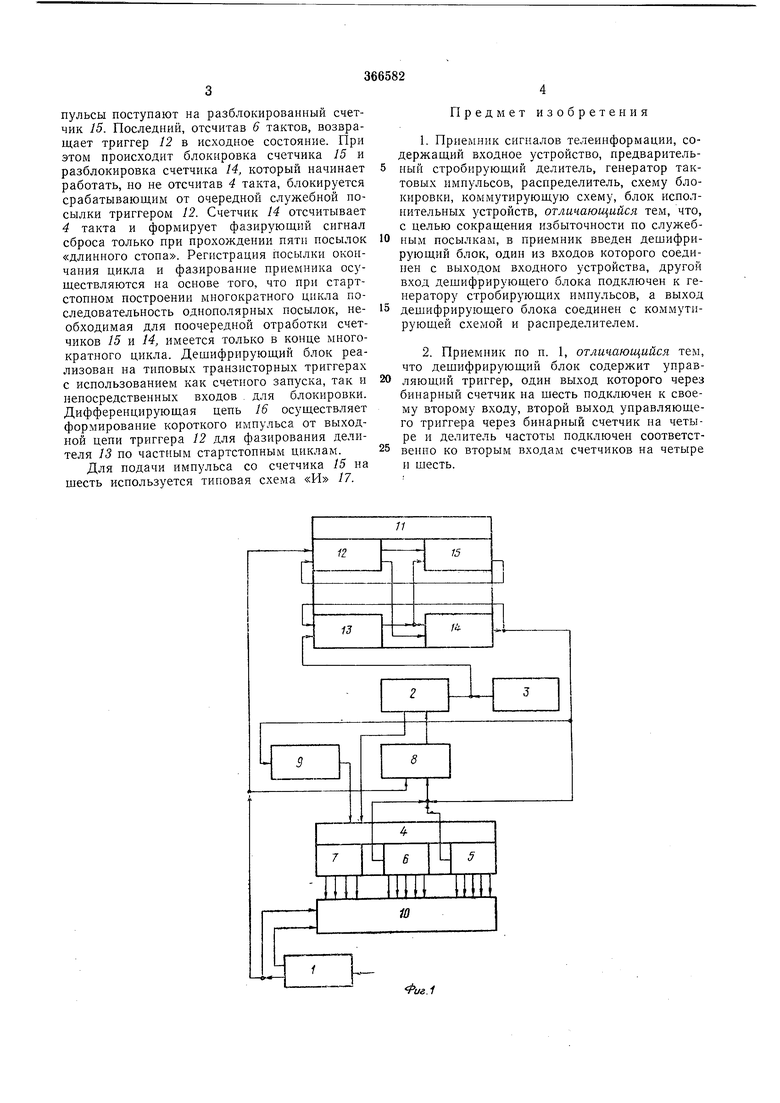

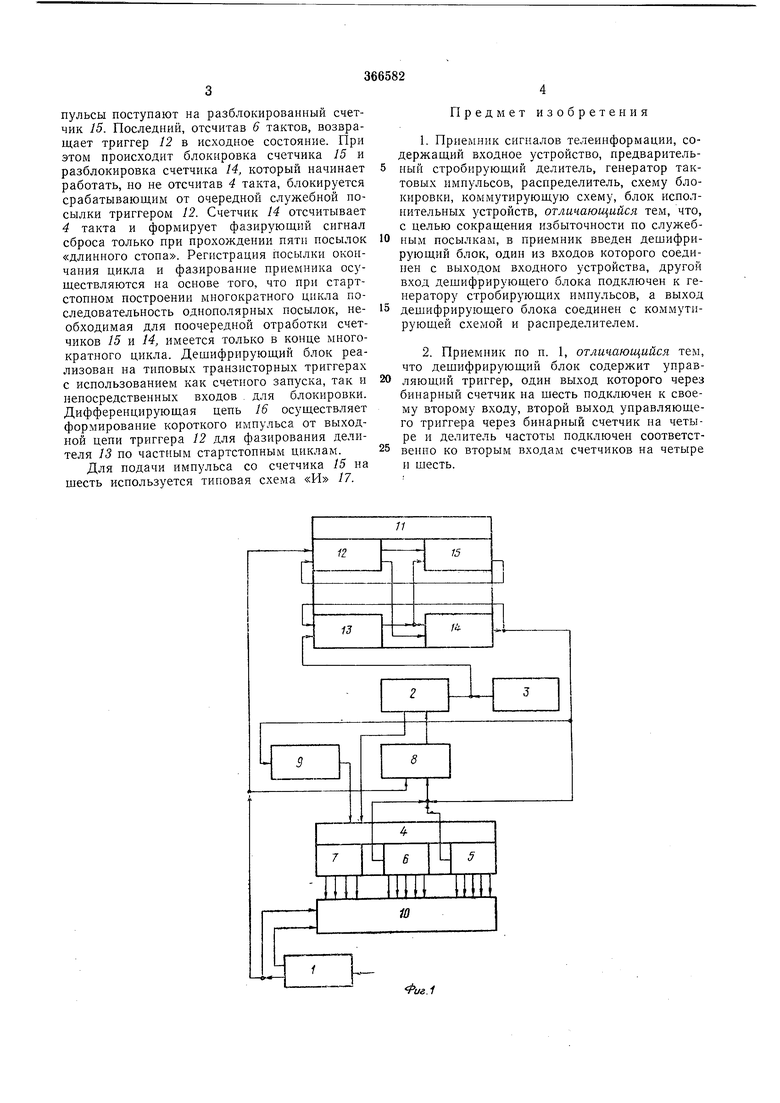

Дешифрирующий блок содержит управляющий триггер, один выход которого через бинарный счетчик на шесть подключен к своему второму входу, а другой выход через бинарный счетчик на четыре и делитель частоты подключен соответственно ко вторым входам счетчиков на четыре и шесть.

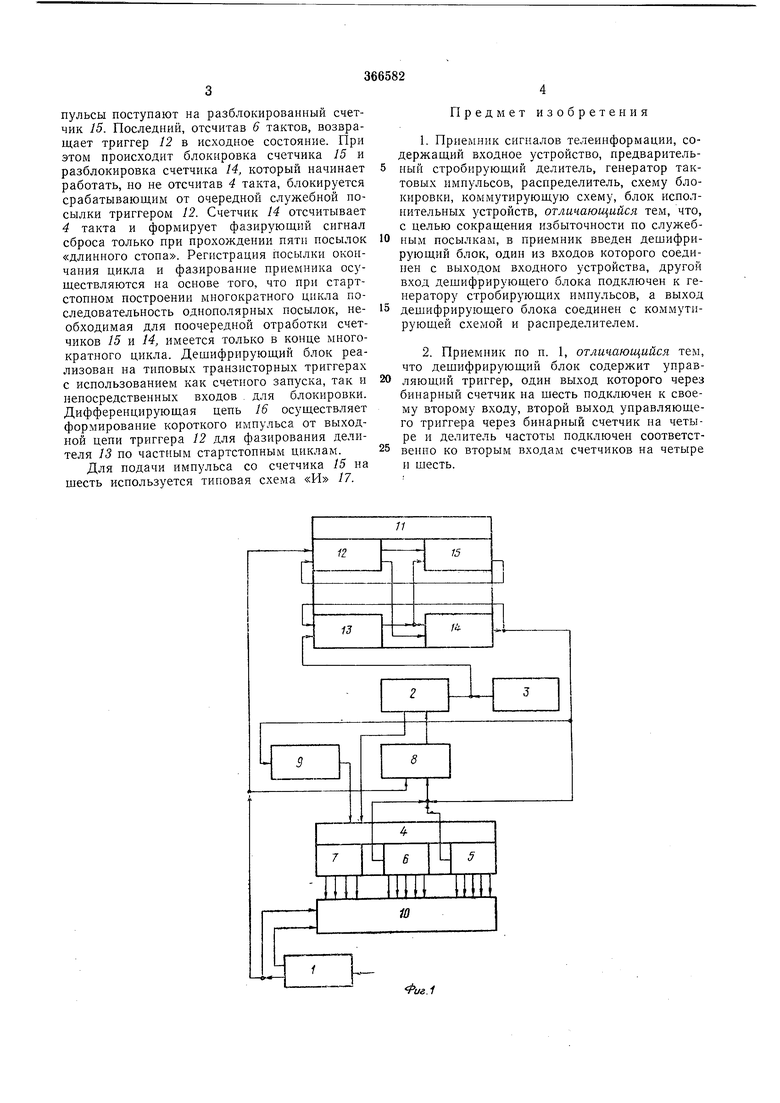

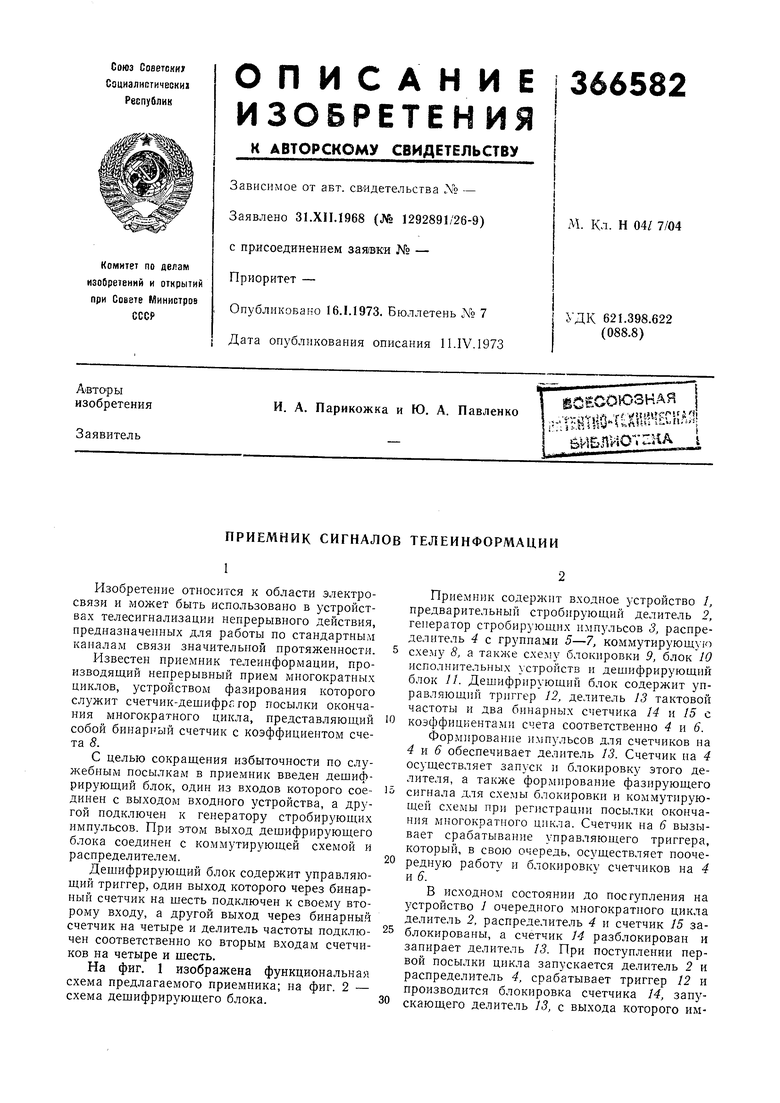

На фиг. 1 изображена функциональная схема предлагаемого приемника; на фиг. 2 - схема дешифрирующего блока.

2

Приемник содержит входное устройство /, предварительный стробнрующнй делитель 2, генератор стробирующих импульсов 3, раснределитель 4 с группами 5-7, коммутирующую схему 8, а также схему блокировки 9, блок 10 исполнительных устройств и дешифрирующий блок //. Дешифрирующий блок содержит управляющий Tpjirrep 12, делитель 13 тактовой частоты и два бинарных счетчика 14 и 15 с

коэффициентами счета соответственно 4 i 6.

Форм1 рование импульсов для счетчиков на 4 и 6 обеспечивает делитель 13. Счетчик на 4 осуществляет запуск и блокировку этого делителя, а также формирование фазирующего

сигпала для схемы блокировки и коммутирующей схемы при регистрации посылки окончання многократного цикла. Счетчик на 6 вызывает срабатывание управляющего триггера, который, в свою очередь, осуществляет поочередную работу н блокировку счетчиков на 4 и 6.

В исходном состоянии до посгупления на устройство / очередного многократного цикла делитель 2, распределитель 4 и счетчик 15 заблокированы, а счетчик J4 разблокирован и запирает делитель 13. При поступлении первой посылки цикла запускается делитель 2 и распределитель 4, срабатывает триггер 12 и производится блокировка счетчика 14, заиуекающего делитель 13, с выхода которого импульсы поступают на разблокированный счетчик 15. Последний, отсчитав 6 тактов, возвращает триггер 12 в исходное состояние. При этом происходит блокировка счетчика 15 и разблокировка счетчика 14, который начинает работать, но не отсчитав 4 такта, блокируется срабатывающим от очередной служебной посылки триггером 12. Счетчик 14 отсчитывает 4 такта и формирует фазирующий сигнал сброса только при прохождении пяти посылок «длинного стопа. Регистрация посылки окончания цикла и фазирование приемника осуществляются на основе того, что при стартстопном построении многократного цикла последовательность однополярных посылок, необходимая для поочередной отработки счетчиков 15 и 14, имеется только в конце многократного цикла. Дещифрирующий блок реализован на типовых транзисторных триггерах с использованием как счетного запуска, так и непосредственных входов . для блокировки. Дифференцирующая цепь 16 осуществляет формирование короткого импульса от выходной цепи триггера 12 для фазирования делителя 13 по частным стартстопным циклам.

Для подачи импульса со счетчика 15 на шесть используется типовая схема «И 17.

Предмет изобретения

1.Приемник сигналов телеинформации, содержащий входное устройство, предварительный стробирующий делитель, генератор тактовых импульсов, распределитель, схему блокировки, коммутирующую схему, блок исполнительных устройств, отличающийся тем, что, с целью сокращения избыточности по служебным посылкам, в приемник введен дешифрирующий блок, один из входов которого соединен с выходом входного устройства, другой вход дешифрирующего блока подключен к генератору стробирующих импульсов, а выход

дешифрирующего блока соединен с коммутирующей схемой и распределителем.

2.Приемник по п. 1, отличающийся тем, что дешифрирующий блок содержит управляющий триггер, один выход которого через бинарный счетчик на шесть подключен к своему второму входу, второй выход управляющего триггера через бинарный счетчик на четыре и делитель частоты подключен соответственно ко вторым входам счетчиков на четыре и шесть.

Pue.l f узлом 8,9

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ СИГНАЛОВ ТЕЛЕИНФОРМАЦИИ | 1967 |

|

SU196085A1 |

| Приемник сигналов телеинформации | 1972 |

|

SU448610A1 |

| Устройство передачи и приема сигналов телеинформации | 1978 |

|

SU698032A1 |

| УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ ИЗМЕРИТЕЛЯ ИСКАЖЕНИЙ СТАРТСТОПНЫХ ТЕЛЕГРАФНЫХ СИГНАЛОВ | 1971 |

|

SU320073A1 |

| Устройство для фазирования электронного телеграфного приемника | 1983 |

|

SU1124437A1 |

| Стартстопное приемное устройство телеграфных сигналов | 1976 |

|

SU652723A1 |

| Приемник сигналов телеинформации | 1973 |

|

SU490269A1 |

| ПЕРЕДАТЧИК ТЕЛЕГРАФНОГО АППАРАТАBCECOiOSHAHisYr^rrt^n Т' '•''•'••''?- 5^ДЯ lAai.iJir<l- ii. = .sa! >&• •'«« | 1973 |

|

SU372726A1 |

| Устройство для фазирования элек-ТРОННОгО ТЕлЕгРАфНОгО пРиЕМНиКА | 1979 |

|

SU813808A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

Авторы

Даты

1973-01-01—Публикация