Изобретение относится к области вычислительной техники и может быть использовано в аналого-цифровых вычислительных системах.

Известны устройства для решения систем обыкновенных дифференциальных уравнений, в которых задание начальных условий производится с помощью специальных устройств.

Однако в известных устройствах в модели, кроме основных решающих устройств, необходимо иметь специальное устройство задания начальных условий, которое не используется в процессе рещения задач, что приводит к неэффективному использованию оборудования и больщим аппаратурным затратам; модели имеют низкую надежность в связи с наличием в ней электромеханических элементов, необходимость применения которых обусловлена сложностью электронного аналогового переключателя с качественными техническими характеристиками; кроме того, модели присуща низкая точность решения задачи за счет несинхронности работы релейных ключей.

Предлагаемое устройство отличается от известного тем, что оно содержит соединенный с программным блоком логический блок, выполненный на элементах «И и «ИЛИ, входы которого подключены соответственно к блоку запоминающих модуляторов начальных условий, блоку запоминающих модуляторов правых частей управлений, блоку запоминающих модуляторов коэффициентов, а выходы логического блока соединены соответственно с блоком управляемых проводимостей и с квазианалоговым блоком, что упрощает устройство и повыщает надежность и точность его работы.

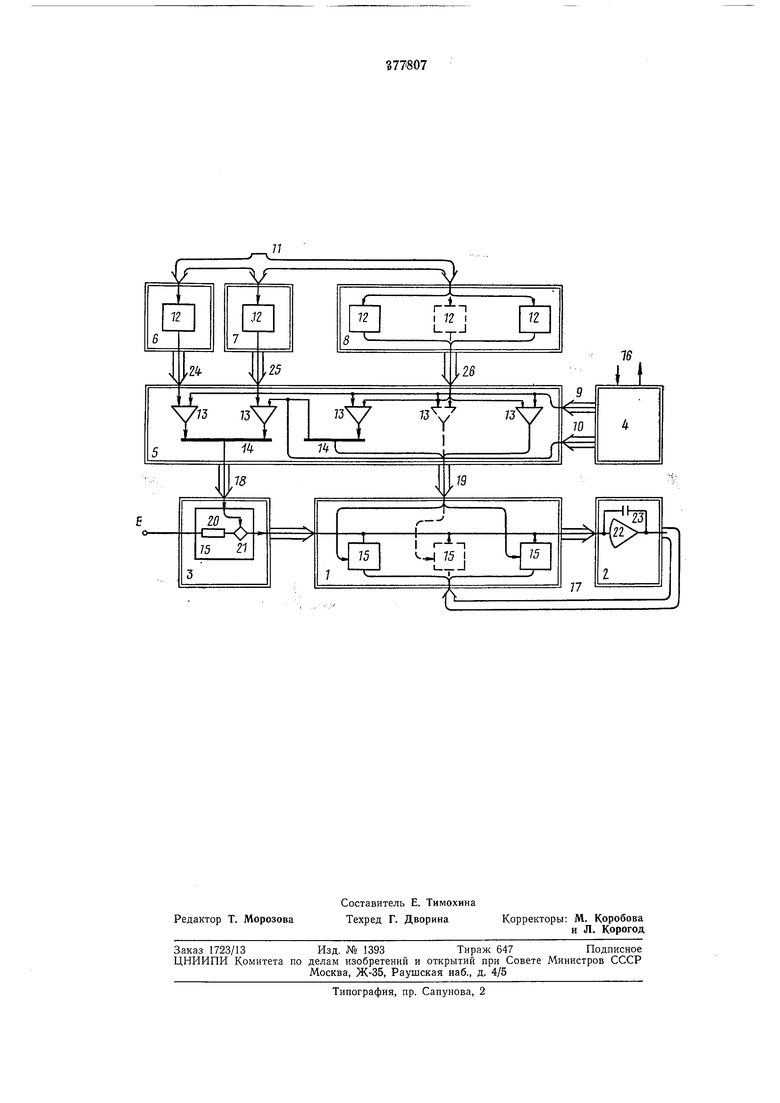

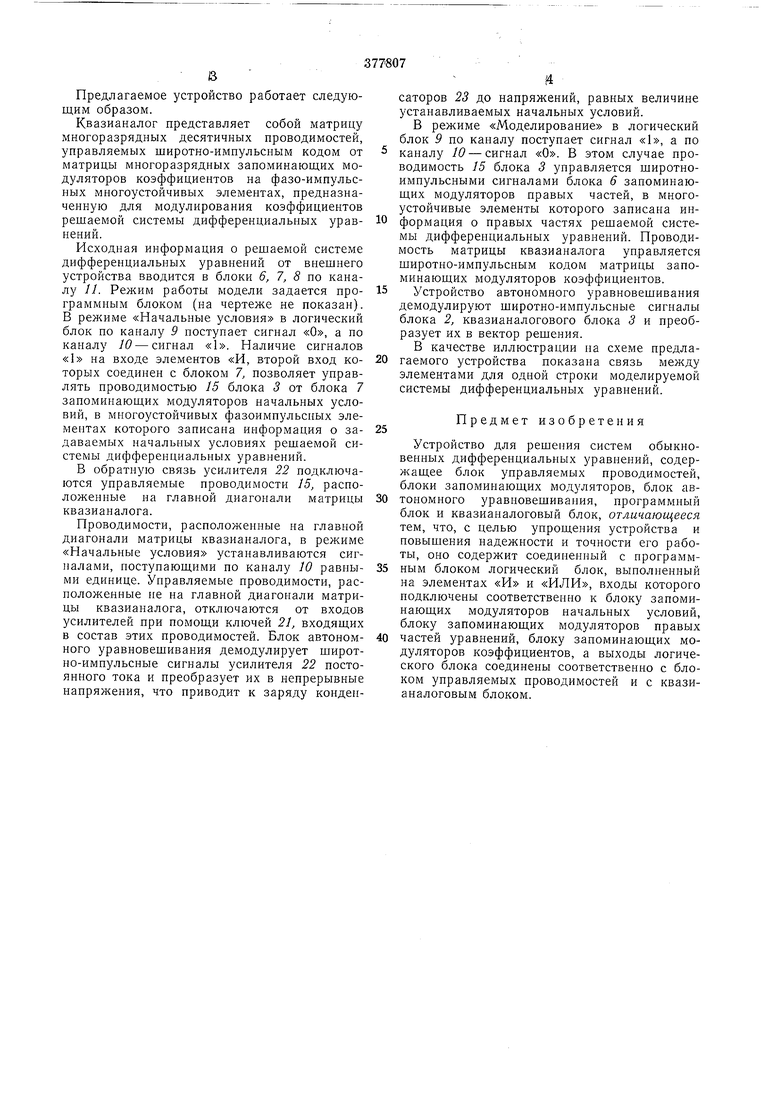

На чертеже дано предлагаемое устройство.

Устройство содержит квазианалоговый блок /, блок 2 автономного уравновещивания, блок 5 управляемых проводимостей, программный блок 4, логический блок 5, блок 6 запоминающих модуляторов правых частей

уравнений, блок 7 запоминающих модуляторов начальных условий, блок 8 запоминающих модуляторов коэффициентов, каналы 9 и 10 задания режимов работы модели, каналы 11 связи запоминающих модуляторов с

внещним устройством, многоустойчивый фазоимпульсный элемент 12, элементы «И 13, элементы «ИЛИ 14, управляемую проводимость 15, канал 16 связи программного блока с внещним устройством, каналы 17 связи

квазианалога с устройством автономного уравновешивания, выходы 18 и 19 логического блока, операционную проводимость 20, электронный ключ 21, усилитель 22 постоянного тока, конденсатор 23 и входы 24-26 логического блока.

13

Предлагаемое устройство работает следующим образом.

Квазианалог представляет собой матрицу многоразрядных десятичных проводимостей, управляемых широтно-импульсным кодом от матрицы многоразрядных запоминающих модуляторов коэффициентов на фазо-импульсных многоустойчивых элементах, предназначенную для модулирования коэффициентов решаемой системы дифференциальных уравнений.

Исходная информация о решаемой системе дифференциальных уравнений от внешнего устройства вводится в блоки 6, 7, 8 по каналу 11. Режим работы модели задается программным блоком (на чертеже не показан). В режиме «Начальные условия в логический блок по каналу 9 поступает сигнал «О, а по каналу 10 - сигнал «1. Наличие сигналов «1 на входе элементов «И, второй вход которых соединен с блоком 7, позволяет управлять проводимостью 15 блока 3 от блока 7 запоминающих модуляторов начальных условий, в многоустойчивых ф|азоимпульсцых элементах которого записана информация о задаваемых начальных условиях решаемой системы дифференциальных уравнений.

В обратную связь усилителя 22 подключаются управляемые проводимости 15, расположенные на главной диагонали матрицы квазианалога.

Проводимости, расположеиные на главной диагонали матрицы квазианалога, в режиме «Начальные условия устанавливаются сигналами, поступаюшими по каналу 10 равными единице. Управляемые проводимости, расположенные не на главной диагонали матрицы квазианалога, отключаются от входов усилителей при помощи ключей 21, входящих в состав этих проводимостей. Блок автономного уравновешивания демодулирует широтно-импульсные сигналы усилителя 22 постоянного тока и преобразует их в непрерывные напряжения, что приводит к заряду конден(4

саторов 23 до напряжений, равных величине устанавливаемых начальных условий.

В режиме «Моделирование в логический блок 9 по каналу поступает сигнал «1, а по

каналу 10 - сигнал «О. В этом случае проводимость 15 блока 5 управляется широтноимпульсными сигналами блока 6 запоминающих модуляторов правых частей, в многоустойчивые элементы которого записана информация о правых частях решаемой системы дифференциальных уравнений. Проводимость матрицы квазианалота управляется широтно-импульсным кодом матрицы запоминающих модуляторов коэффициентов.

Устройство автономного уравновешивания демодулируют широтно-импульсные сигналы блока 2, квазианалогового блока 3 и преобразует их в вектор решения.

В качестве иллюстрации на схеме предлагаемого устройства показана связь между элементами для одной строки моделируемой системы дифференциальных уравнений.

Предмет изобретения

Устройство для решения систем обыкновенных дифференциальных уравнений, содержащее блок управляемых проводимостей, блоки запоминающих модуляторов, блок автономного уравновешивания, программный блок п квазианалоговый блок, отличающееся тем, что, с целью упрощения устройства и повышения надежности и точности его работы, оно содержит соединенный с программным блоком логический блок, выполненный на элементах «И и «ИЛИ, входы которого подключены соответственно к блоку запоминающих модуляторов начальных условий, блоку запоминающих модуляторов правых

частей уравнений, блоку запоминающих модуляторов коэффициентов, а выходы логического блока соединены соответственно с блоком управляемых проводимостей и с квазианалоговым блоком.

Авторы

Даты

1973-01-01—Публикация