1

Изобретение относится к автоматике и вычислительной технике.

Известно устройство для сокращения избыточности дискретных сигналов, содержащее регистр входа, связанный с вычислительным блоком, к которому подключен блок задания точности аппроксимации, и с блоком ввода, подключенным к регистру выхода, и анализатор.

Описываемое устройство отличается тем, что анализатор содержит счетчик, диодную матрицу, логические схемы, схему задержки, триггер и формирователь импульсов, причем выходы вычислительного блока подключены ко входам триггера, выходы которого через формирователи импульсов подключены к первой схеме сборки, и ко второй схеме сборки, выход которой подключен к первым входам схемы антисовпадения и совпадения, ко вторым входам которых подключена входная шина анализатора, выход схемы антисовпадения подключен ко входу первой схемы сборки, выход которой подключен к сбросовому входу счетчика, а выход схемы совпадения подключен через схему задержки к счетному входу счетчика, выход которого соединен с диодной матрицей, связанной с блоком ввода и регистром выхода.

Это позволяет сократить количество оборудования и тем самым повысить надежность

устройства в работе, что особенно важно при обработке цифровых данных в многоканальных системах обработки.

Поступившие на вход устройства отсчеты обрабатываются в вычислительном устройстве на основе решения неравенства

l( - yi)i - (У1 - г/о) 8,(1)

(У1 -ii-yi)i- (У1 - г/о) - S,(2)

где УН - величина первого отсчета на участке аппроксимации;

г/j+i - величина текущего значения отсчета;

/ - номер отсчета; б - заданная точность аппроксимации.

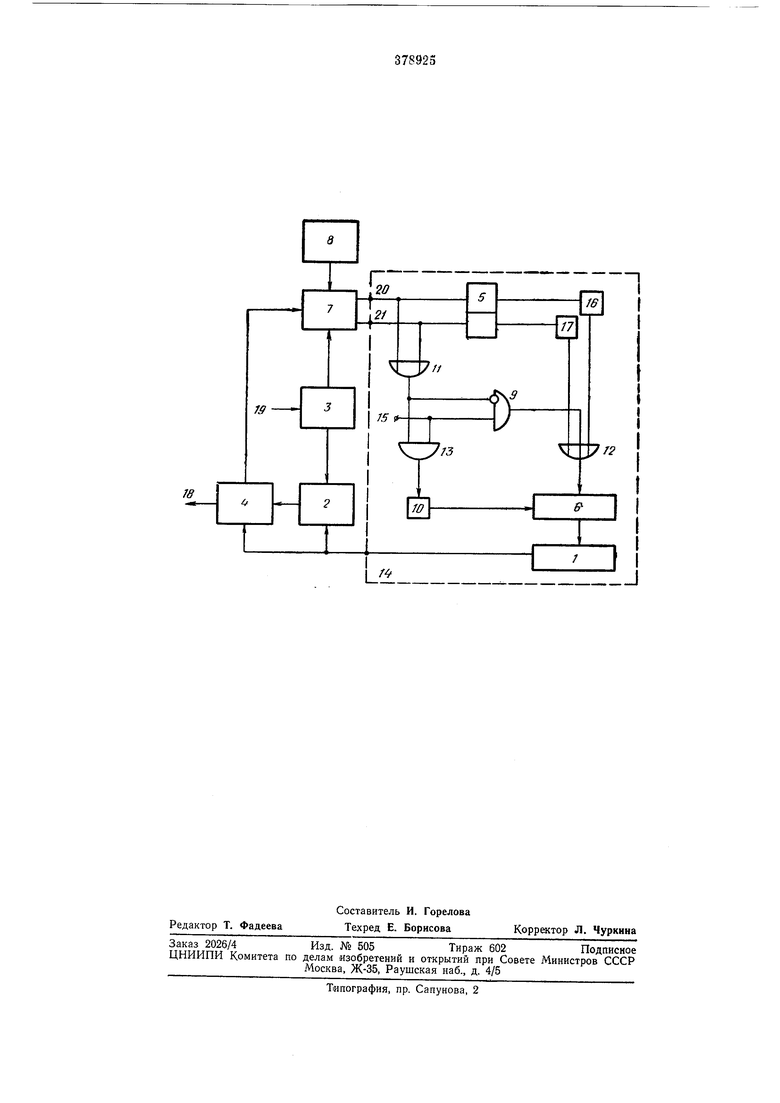

На чертеже изображена структурная схема предлагаемого устройства.

Оно содержит диодную матрицу 1, блок ввода 2, регистр входа 3, регистр выхода 4, триггер 5, счетчик 6, вычислительный блок 7, блок 8 задания точности аппроксимации, схему антисовпадения 9, схему 10 временной задержки, схемы сборки // и 12, схему совпадения 13. Диодная матрица / выполнена в виде одной строчки для выделения определенного кода числа. Ее выход является выходом анализатора 14, который подключен к блоку ввода 2 и регистру выхода 4.

Триггер 5, включенный на входе анализатора 14, выполняет задачу выделения первых импульсов, поступающих с выходов вычислительного блока 7. В блоке задания точности аппроксимации хранятся коды чисел, которые определяют границы зоны допустимых отклонений. Блок антисовпадения 9 входом «Запрет связан через схему сборки 11 с выходами вычислительного блока, а прямым входом - с входом 15 анализатора, на который поступают импульсы синхронизации (тактовые импульсы). Формирователи импульсов 16 и 17 (в простейшем случае дифференцирующие цепочки) включены на выходе триггера 5 для выделения моментов измерения состояния триггера.

Устройство работает следующим образом. В исходном состоянии после вывода существенного отсчета на выход 18 устройства сигналом от диодной матрицы 1 блок ввода 2 открыт, в регистре 3 хранится код числа предыдущего отсчета, регистр 4 очищен, триггер 5 и счетчик 6 находятся в состоянии, соответствующем предыдущему циклу работы устройства. Очередной отсчет (г/о), первый на новом участке аппроксимации, со входа 19 устройства вводится в регистр 3 и затем через блок ввода 2 - в регистр 4, блок ввода 2 закрывается. Последующие отсчеты (например, t/i+i) со входа 19 поступают через регистр входа 3 в вычислительный блок 7, где обрабатываются согласно неравенствам (1) и (2), причем значение предыдущего отсчета (г/г) хранится в вычислительном блоке.

В процессе работы вычислительного блока на его выходах 20 или 21 могут появляться импульсы. На выходе 20 вычислительного блока импульсы возникают в случае невыполнения неравенства (1), т. е. при превышении (t+l)-biM отсчетом верхней границы зоны допустимых отклонений. На выходе 21 импульсы возникают при невыполнении неравенства (2).

Рассмотрим работу анализатора 14 в нескольких типичных ситуациях. Нусть на выходе 20 появилось k импульсов, следующих подряд друг за другом. В этом случае от первого импульса триггер 5 опрокидывается в другое устойчивое состояние. На его выходе формирователем импульсов образуется импульс, который устанавливает счетчик 6 в нуль, этот же импульс с выхода 20 через схему сборки 11 действует на схему антисовпадения как сигнал запрета, а на схему совпадения 13 как разрещающий сигнал. Тактовый импульс, совпадающий во времени с импульсами на выходах 20 или 21, поступает со входа 15 через схему совпадения 13 и схему задержки 10 на счетный вход счетчика 6. Второй: и .Последующие импульсы будут действовать- на элементы схемы анализатора аналогично; .однако триггер 5 останется в прежнем состоянии. Триггер может менять свое состояние только от первого из импульсов, подаваемого йа одно его плечо. В результате в,счетчик вводится число k. Если в матрице / предварительно защифрован код, равньш k, то происходит совпадение кодов, и на выходе

матрицы возникает сигнал вывода существенного отсчета. Сигнал выводит число из регистра 4 на выход 18 устройства и открывает блок 2 для ввода следующего отсчета. В любом другом случае: если импульсы на выходе

20 или 21 чередуются соответственно с импульсами на выходах 20 или 21 вычислительного устройства или если импульсы на выходах 20 или 21 чередуются с отсутствием импульсов по обоим выходам, в счетчике 6 не

происходит накапливания импульсов. В первом случае счетчик сбрасывается на О импульсом с противоположного выхода вычислительного устройства, который изменяет при этом состояние триггера 5 и сбрасывает счетчик через схему сборки 12, а во втором случае- тактовым импульсом со входа 19, который проходит через схему 9, так как отсутствует запрещающий импульс на ее втором входе.

Таким образом, на выходе матрицы появляются импульсы для вывода существенного отсчета только в том случае, когда в счетчике 6 окажется код числа k. Во всех остальных случаях счетчик устанавливается в нуль. Все

отсчеты, с приходом которых счетчик не устанавливается в положение для вывода существенного отсчета, считаются либо помехой, либо избыточными.

Предмет изобретения

Устройство для сокращения избыточности дискретных сигналов, содержащее регистр входа, связанный с вычислительным блоком, к которому подключен блок задания точности аппроксимации, и с блоком ввода, подключенным к регистру выхода, и анализатор, отличающееся тем, что, с целью упрощения и повышения надежности устройства в работе, анализатор содержит счетчик, диодную матрицу, логические схемы, схему задержки,

триггер и формирователи импульсов, причем выходы вычислительного блока подключены ко входам триггера, выходы которого через формирователи импульсов подключены к первой схеме сборки, и ко второй схеме сборки,

выход которой подключен к первым входам схемы антисовпадения и совпадения, ко вторым входам которых подключена входная шина анализатора, выход схемы антисовпадения подключен ко входу первой схемы сборки, выход которой подключен к сбросовому входу счетчика, а выход схемы совпадения подключен через схему задержки к счетному входу счетчика, выход которого соединен с диодной матрицей, связанной с блоком ввоаа

и регистром выхода.

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ КОММУТАТОР СИСТЕМЫ ТЕЛ ЕИЗМЕРЕН ИИ | 1973 |

|

SU407376A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ГАММА-ПРОФИЛО ГРАФА | 1970 |

|

SU270858A1 |

| БИБЛГ: | 1973 |

|

SU378842A1 |

| Устройство для передачи телеметрической информации | 1982 |

|

SU1030830A1 |

| Третьоктавный спектральный анализатор | 1985 |

|

SU1308927A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ С ПОСТОЯННЫМ ЧИСЛОМ «ЕДИНИЦ» | 1969 |

|

SU241110A1 |

| Функциональный генератор | 1987 |

|

SU1501100A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ТОРМОЖЕНИЕМ ПОЕЗДА | 1967 |

|

SU190406A1 |

| Цифровой вольтметр | 1977 |

|

SU815652A1 |

| Адаптивный коммутатор телеизмерительной системы | 1980 |

|

SU877597A1 |

Авторы

Даты

1973-01-01—Публикация