11308927

зобретение относится к измерипопо ля вы бл ро сл ра ды пе то кл вх пе вы ра вт пр бл

10

ельной технике, в частности к облас- и измерения характеристик случайных игналов.

Целью изобретения является расшиение функциональных возможностей ретьоктавного анализатора за счет беспечения возможности измерения аксимальных значений сигнала в соотетствующих полосах частот.

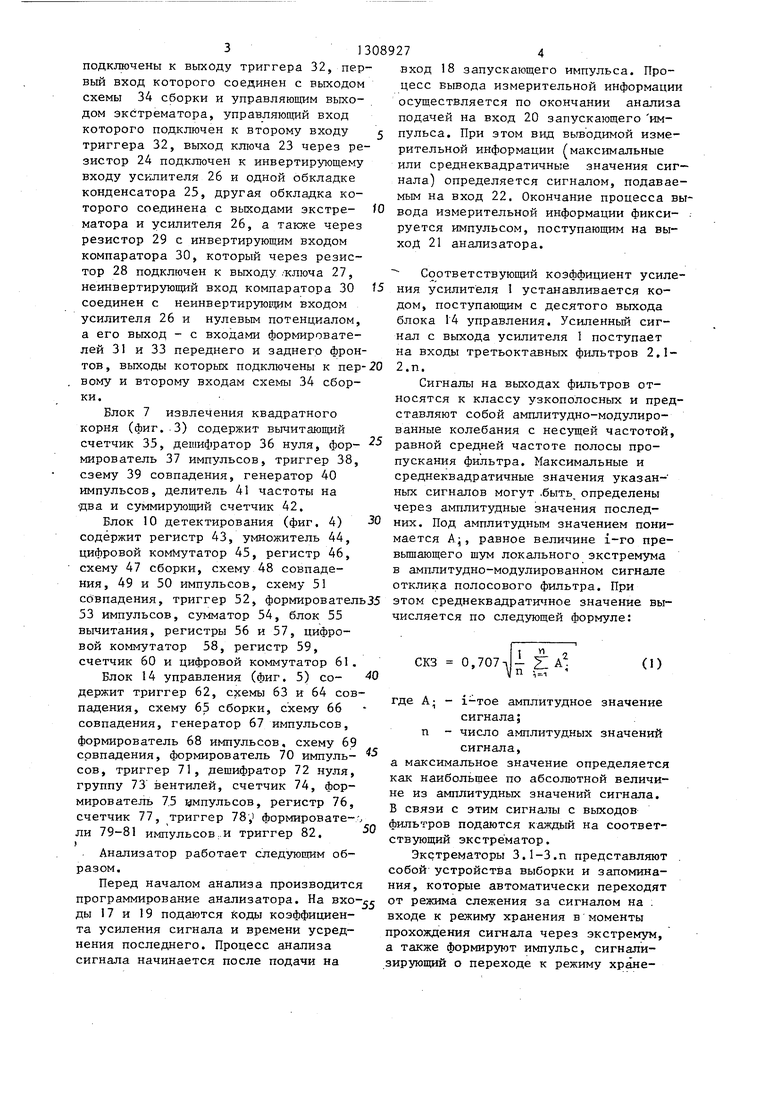

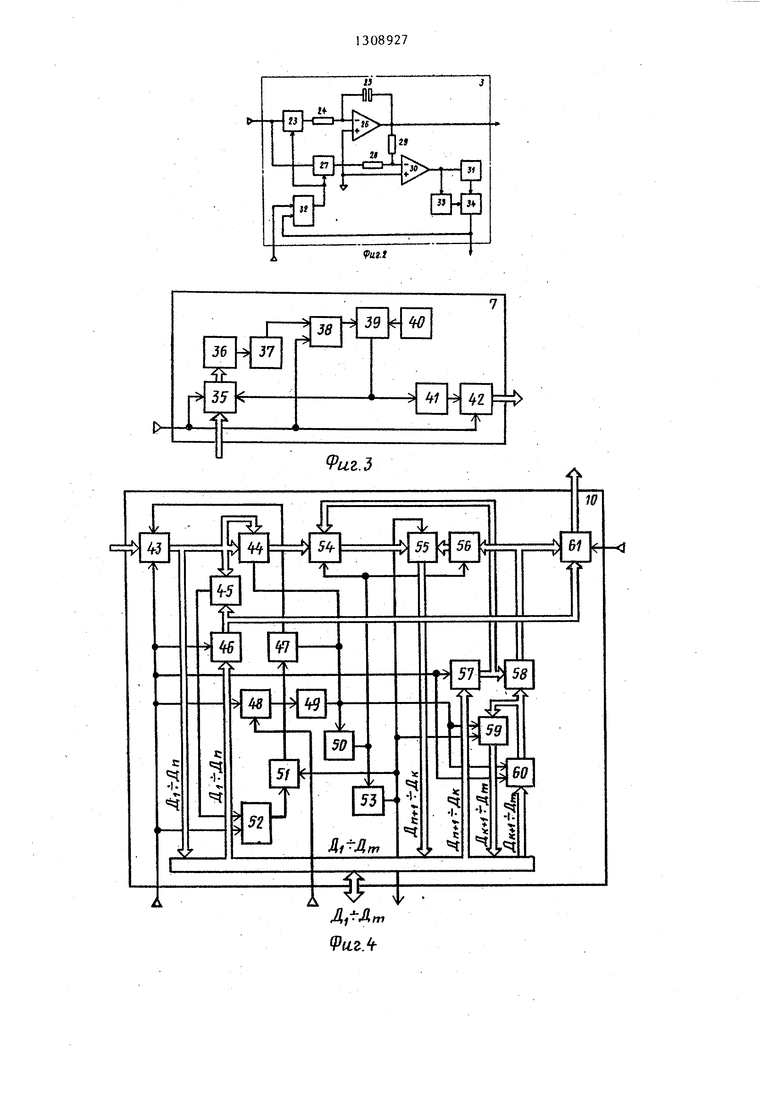

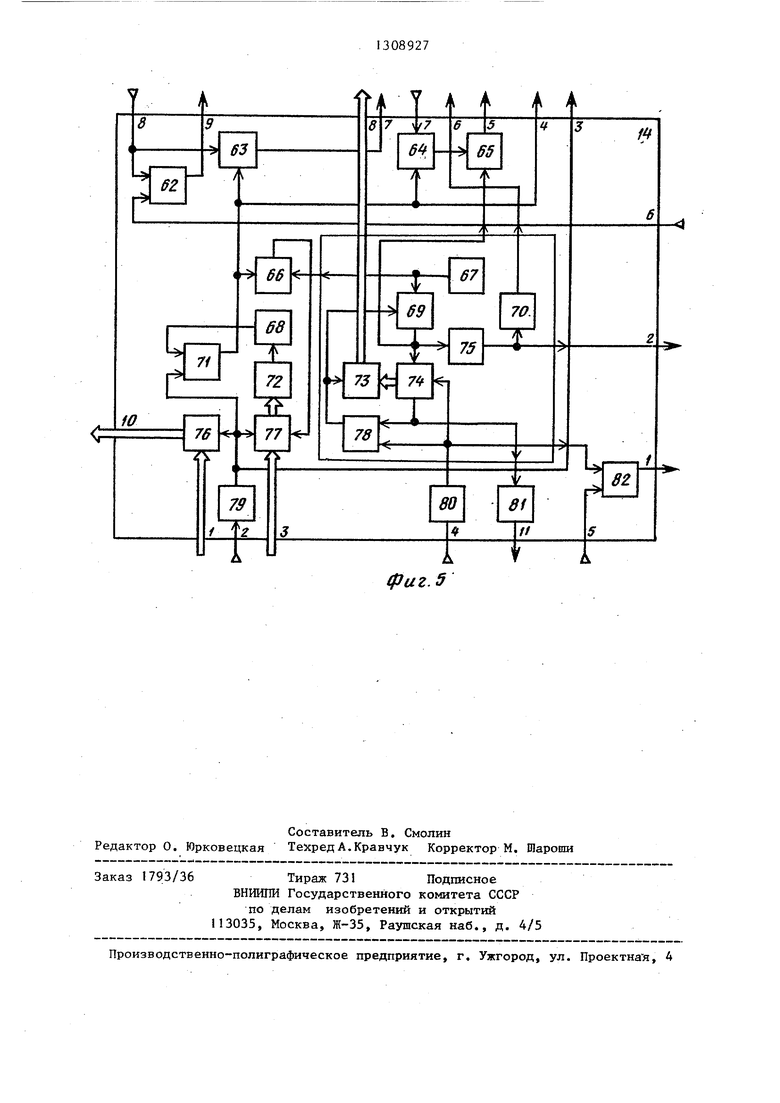

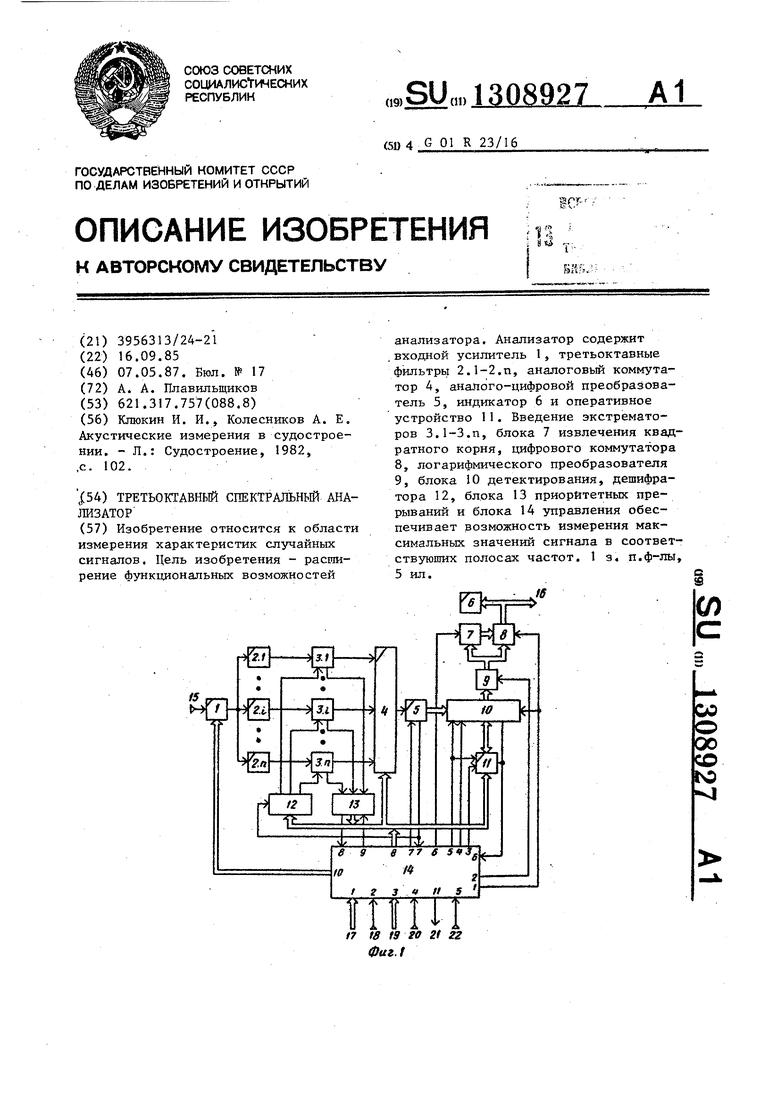

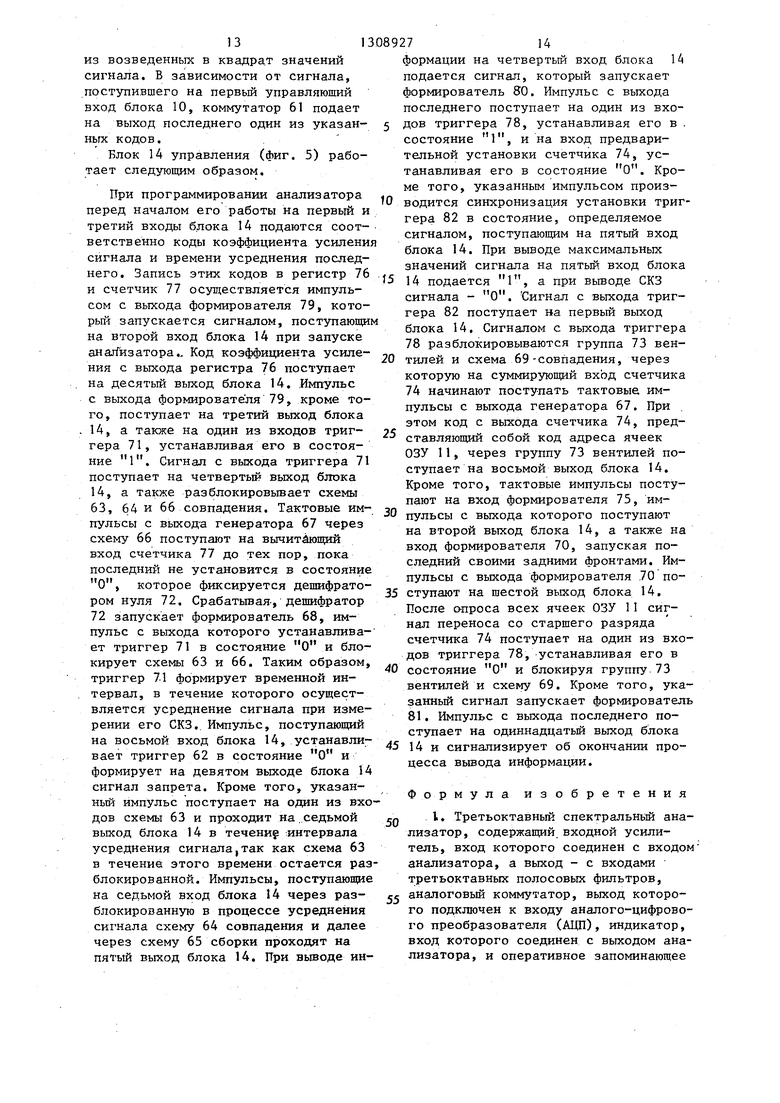

На фиг. 1 представлена блок-схема нализатора; на фиг. 2 - блок-схема кстрематора; на фиг. 3 - блок-схема лока извлечения квадратного корня а фиг.. 4 - схема блока детектироваия; на фиг. 5 - схема блока управлеия.

Анализатор (фиг. 1) содержит входой усилитель 1, третьоктавные фильт15

30

35

ы 2.1-2.П, экстрематоры 3.1-ЗсП,. аналоговый коммутатор 4, АЦП 5, индиатор 6, блок 7 извлечения квадратного корня, цифровой коммутатор 8, логарифмический преобразователь 9,. блок 25 10 детектирования (детектор), ОЗУ 11, ешифратор 12, блок 13 приоритетных прерываний и блок 14 управления. На вход 15 подается анализируемый сигнал, на выход 16 поступают коды максимальных или среднеквадратичных зна-. чений (СКЗ) сигнала в соответствующих полосах частот, на входы 17-20 анализатора подаются (с клавиатуры на ли- лицевой панели анализатора или с выхода внешнего управляющего устройства, например ЭВМ) соответственно код коэффициента усиления сигнала, импульс запуска анализатора,- код времени усреднения сигнала, импульс начала вывода измерительной информации На выход 21 анализатора подается импульс, сигнализирующий об окончании процесса вьюода информации.

На вход 22 анализатора подается потенциальный сигнал, определяющий вид поступающей на выход анализатора измерительной информации (максимальные или среднеквадратичные значения анализируемого сигнала).

Вход 15 соединен с входом усилителя 1, выход которого подключен к входам фильтров 2.1-2.П, выход, каждого фильтра 2.1 соединен с входом соответствующего экстрематора 3.1, выходы экстрематоров 3.1-3,п подключены каждый к соответствующему входу коммутатора 4, .выход которого соединен с входом АЦП 5, выход последнего

подключен подключен ля 9, вых вым входо блока 7, рому вход следнего ра 6 и вы ды 17-20 первому, тому вход ключен к вход 22 первый вы вым управ равляюшрям второй вы преобразо блока 10 блока 14

40

45

50

ОЗУ 11, в торого по блока 14

блока 10 которого ляющему в блока 14 торого со равляющим управляющ к седьмом ющему вх из выходо равляющи экстрема 14 подклю коммутат дам деши выход ко ходом бл 14 подкл блока 13 соединен ответств его упра входом б рого под усилител

Экстр ключ 23, операцион резисторы ,5 формиров триггер фронта и рематора 32 и 27,

подключен к входу блока 10, выходом подключенного к входупреобразователя 9, выход которого соединен с первым входом коммутатора 8 и входом блока 7, выходом подключенного к второму входу коммутатора 8, выход последнего соединен с входом индикатора 6 и выходом 16, и выходом 16, входы 17-20 подключены соответственно к первому, второму, третьему и четвертому входам блока 14, выход 21 подключен к одиннадцатому выходу, а вход 22 к пятому входу блока 14, первый выход которого соединен с первым управляющим входом блока 10 и уп- равляюшрям входом коммутатора 8, а второй выход - с управляющим входом преобразователя 9, управляющий выход блока 10 соединен с шестым входом блока 14 и первым управляющим входом

0

5

5

0

5

0

ОЗУ 11, второй управляюршй вход которого подключен к тр етьему выходу блока 14, четвертый выход которого

с вторым управляющим входом блока 10 третий управляющий вход которого подключен к третьему управляющему входу ОЗУ 11 и пятому выходу блока 14, шестой и седьмой выходы которого соединены соответственно с управляющими входами блока 7 и АЦП 5, управляющий выход которого подключен к седьмому входу блока 14 и управляющему входу дешифратора 12, каждый из выходов которого соединен с управляющим входом соответствующего экстрематора 3.1, восьмой выход блока 14 подключен к управляющему входу коммутатора 4, выходу блока 13 и входам дешифратора 12 и ОЗУ 11, вход- выход которого соединен с входом-выходом блока 10, девятый выход блока 14 подключен к управляющему входу, блока 13, каждый из входов которого соединен с управляющим выходом соответствующего экстрематора 3.1, а его управляющий выход - с восьмым входом блока 14, десятый выход которого подключен к управляющему входу усилителя 1. .

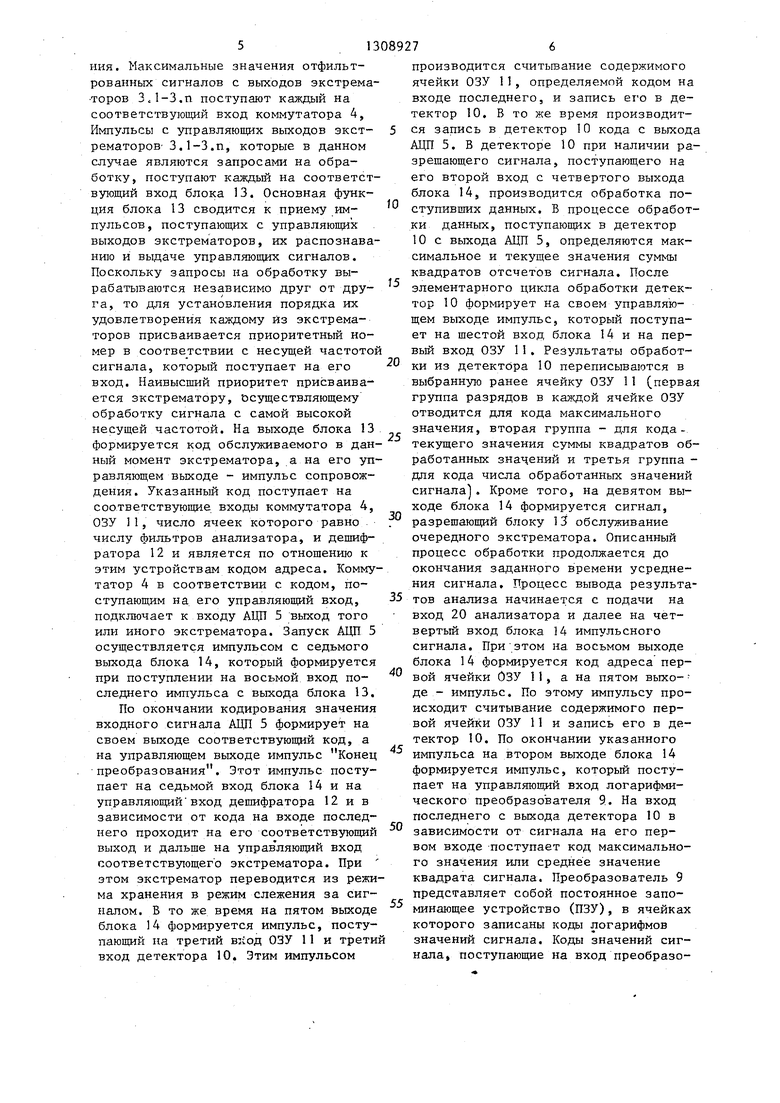

Экстрематор 3 (фиг. 2) содержит ключ 23, резистор 24, конденсатор 25, операционный усилитель 26, ключ 27, резисторы 28 и 29, компаратор 30, 5 формирователь 31 переднего фронта, триггер 32, формирователь 33 заднего фронта и .схему 34 сборки. Вход экстрематора соединен с входами ключей 32 и 27, заправляющие входы которых

31308927

подключены к выходу триггера 32, пер- вход вьй вход которого соединен с выходом схемы 34 сборки и управляющим выходом эксгтрематора, управляющий вход которого подключен к второму входу триггера 32, выход ключа 23 через резистор 24 подключен к инвертирующему входу усршителя 26 и одной обкладке конденсатора 25, другая обкладка которого соединена с выходами экстре- fO матора и усилителя 26, а также через резистор 29 с инвертирующим входом компаратора 30, который через резистор 28 подключен к выходу/ключа 27, неинвертирующий вход компаратора 30 t5 соединен с неинвертирующим входом усилителя 26 и нулевым потенциалом, а его выход - с входами формирователей 31 и 33 переднего и заднего фронтов, выходы которых подключены к пер-20 вому и второму входам схемы 34 сборки.

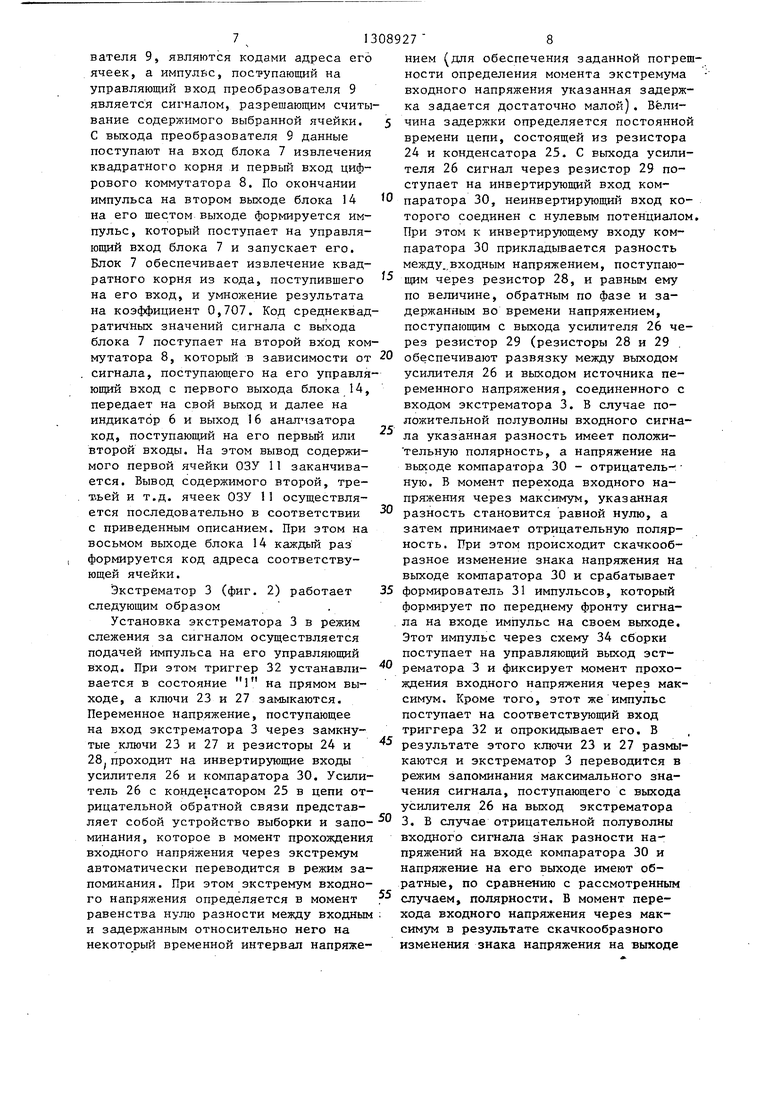

Блок 7 извлечения квадратного корня (фиг.-З) содержит вычитающий счетчик 35, дешифратор 36 нуля, фор- мирователь 37 импульсов, триггер 38, сзему 39 совпадения, генератор 40 импульсов, делитель 41 частоты на два и суммирующий счетчик 42.

Блок 10 детектирования (фиг. 4) 0 содержит регистр 43, умножитель 44, цифровой коммутатор 45, регистр 46, схему 47 сборки, схему 48 совпаде18 запускающего импульса. Процесс вывода измерительной информации осуществляется по окончании анализа подачей на вход 20 запускающего импульса. При этом вид выводимой измерительной информации (максимальные или среднеквадратичные значения сиг нала) определяется сигналом, подавае мым на вход 22, Окончание процесса вы вода измерительной информации фикси- руется импульсом, поступающим на выход 21 анализатора.

Соответствующий коэффициент усиле ния усилителя 1 устанавливается кодом, поступающим с десятого выхода блока 14 управления. Усиленный сигнал с выхода усилителя 1 поступает на входы третьоктавных фильтров 2,1- 2.п.

Сигналы на выходах фильтров относятся к классу узкополосных и представляют собой амплитудно-модулиро- ванные колебания с несущей частотой, равной средней частоте полосы пропускания фильтра. Максимальные и среднеквадратичные значения указан- ных сигналов могут .быть определены через амплитудные значения последних. Под амплитудным значением понимается А;, равное величине i-ro превьппающего шум локального экстремума в амплитудно-модулированном сигнале отклика полосового фильтра. При совпадения, триггер 52, формирователь35 этом среднеквадрати шое значение выния, 49 и 50 импульсов, схему 51

40

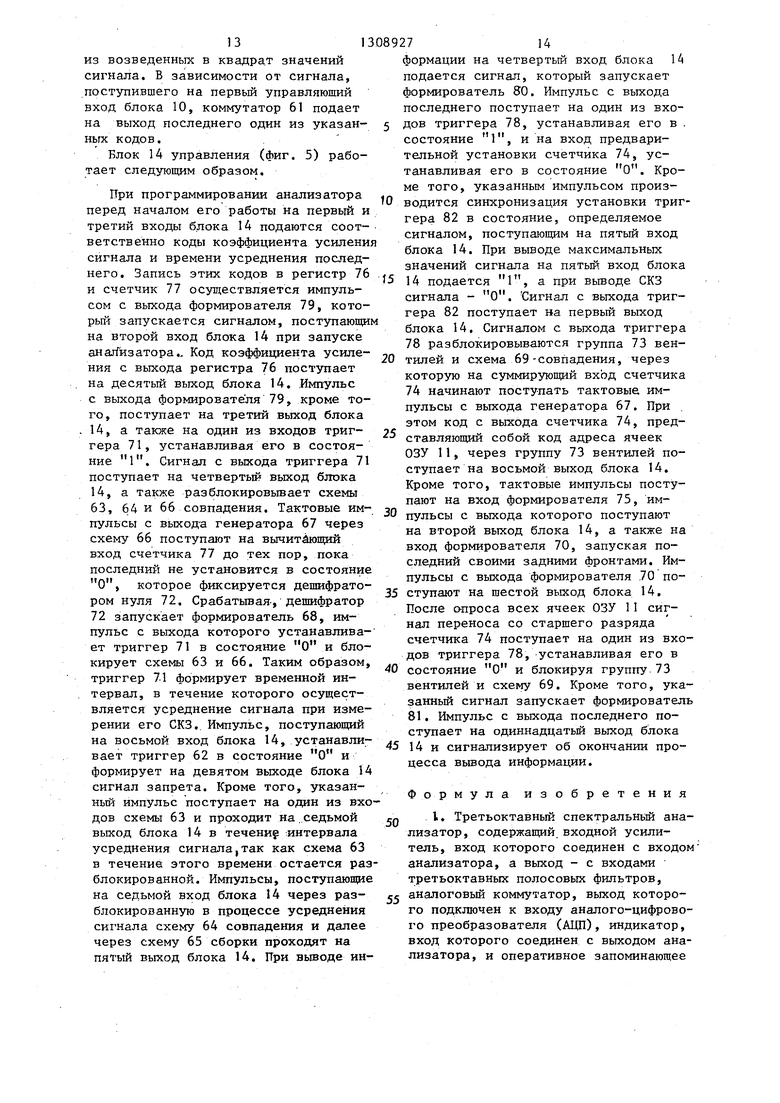

53 импульсов, сумматор 54, блок 55 вычитания, регистры 56 и 57, цифровой коммутатор 58, регистр 59, счетчик 60 и цифровой коммутатор 61 Блок 14 управления (фиг. 5) содержит триггер 62, схемы 63 и 64 совпадения, схему 65 сборки, схему 66 совпадения, генератор 67 импульсов,

формирователь 68 импульсов, схему 69 совпадения, формирователь 70 импуль- сов, триггер 71, дешифратор 72 нуля, группу 73 вентилей, счетчик 74, формирователь 7.5 импульсов, регистр 76, счетчик 77, триггер 78, формирователи 79-81 импульсов,и триггер 82.

Анализатор работает следующим образом.

Перед началом анализа производится

числяется по следующей фор гуле:

СКЗ 0,707

А

(О

50

где А- - 1-тое амплитудное значение

сигнала; п - число амплитудных значений

сигнала,

а максимальное значение определяется как наибольшее по абсолютной величине из амплитудных значений сигнала. В связи с этим сигналы с выходов фильтров подаются каждый на соответствующий экстрёматор.

Экстрематоры 3.1-З.п представляют собой устройства выборки и запоминания, которые автоматически переходят

программирование анализатора. На вхо- от режима слежения за сигналом на

ды 17 и 19 подаются коды коэффициента усиления сигнала и времени усреднения последнего. Процесс анализа сигнала начинается после подачи на

входе к режиму хранения в моменты прохождения сигнала через экстрему а также формируют импульс, сигнали зирующий о переходе к режиму хране

вход

18 запускающего импульса. Процесс вывода измерительной информации осуществляется по окончании анализа подачей на вход 20 запускающего импульса. При этом вид выводимой измерительной информации (максимальные или среднеквадратичные значения сигнала) определяется сигналом, подаваемым на вход 22, Окончание процесса вывода измерительной информации фикси- руется импульсом, поступающим на выход 21 анализатора.

Соответствующий коэффициент усиления усилителя 1 устанавливается кодом, поступающим с десятого выхода блока 14 управления. Усиленный сигнал с выхода усилителя 1 поступает на входы третьоктавных фильтров 2,1- 2.п.

Сигналы на выходах фильтров относятся к классу узкополосных и представляют собой амплитудно-модулиро- ванные колебания с несущей частотой, равной средней частоте полосы пропускания фильтра. Максимальные и среднеквадратичные значения указан- ных сигналов могут .быть определены через амплитудные значения последних. Под амплитудным значением понимается А;, равное величине i-ro пречисляется по следующей фор гуле:

40

СКЗ 0,707

А

(О

0

где А- - 1-тое амплитудное значение

сигнала; п - число амплитудных значений

сигнала,

а максимальное значение определяется как наибольшее по абсолютной величине из амплитудных значений сигнала. В связи с этим сигналы с выходов фильтров подаются каждый на соответствующий экстрёматор.

Экстрематоры 3.1-З.п представляют собой устройства выборки и запоминания, которые автоматически переходят

входе к режиму хранения в моменты прохождения сигнала через экстремум, а также формируют импульс, сигнализирующий о переходе к режиму хране

51

ния. Максимальные значения отфильтрованных сигналов с выходов экстрема торов 3.1-З.п поступают каждый на соответствующий вход коммутатора 4, Импульсы с управляющих выходов экст- рематоров 3.1-З.п, которые в данном случае являются запросами на обработку, поступают каждый на соответствующий вход блока 13. Основная функция блока 13 сводится к приему импульсов , поступающих с управляющих выходов экстрематоров, их распознаванию и выдаче управляющих сигналов. Поскольку запросы на обработку вырабатываются независимо друг от друга, то для установления порядка их удовлетворения каждому из экстрема- торов присваивается приоритетный номер в соответствии с несущей частото сигнала, который поступает на его вход. Наивысший приоритет присваивается экстрематору, осуществляющему обработку сигнала с самой высокой несущей частотой. На выходе блока 13 формируется код обслуживаемого в данный момент экстрематора, а на его управляющем выходе - импульс сопровождения. Указанный код поступает на соответствующие входы коммутатора 4, ОЗУ 11, число ячеек которого равно числу фильтров анализатора, и дешифратора 12 и является по отношению к этим устройствам кодом адреса. Коммутатор 4 в соответствии с кодом, поступающим на его управляющий вход, подключает к входу АЦП 5 выход того или иного экстрематора. Запуск АЦП 5 осуществляется импульсом с седьмого выхода блока 14, который формируется при поступлении на восьмой вход последнего импульса с выхода блока 13. По окончании кодирования значения входного сигнала АЦП 5 формирует на своем выходе соответствующий код, а на управляющем выходе импульс Конец преобразования. Этот импульс поступает на седьмой вход блока 14 и на управляющий вход дешифратора 12 и в зависимости от кода на входе последнего проходит на его соответствующий выход и дальше на управ ляющий вход соответствующего экстрематора. При этом экстрематор переводится из режима хранения в режим слежения за сигналом. Б то же время на пятом выходе блока 14 формируется импульс, поступающий на третий взсод ОЗУ 11 и трети вход детектора 10. Этим импульсом

5

5

производится считьгоание содержимого ячейки ОЗУ 11, определяемой кодом на входе последнего, и запись его в детектор 10. В то же время производится запись в детектор 10 кода с выхода АЦП 5. В детекторе 10 при наличии разрешающего сигнала, поступающего на его второй вход с четвертого выхода блока 14, производится обработка поступивших данных. Б процессе обработки данных, поступаюш 1х в детектор 10 с выхода АЦП 5, определяются максимальное и текущее значения суммы квадратов отсчетов сигнала. После элементарного цикла обработки детектор 10 формирует на своем управляющем выходе импульс, который поступает на шестой вход, блока 14 и на первый вход ОЗУ 11. Результаты обработки из детектора 10 переписьгоаются в выбранную ранее ячейку ОЗУ 11 (первая группа разрядов в каждой ячейке ОЗУ отводится для кода максимального значения, вторая группа - для кода- текущего значения суммы квадратов обработанных значений и третья группа - для кода числа обработанных значений сигнала. Кроме того, на девятом выходе блока 14 формируется сигнал, разрешающий блоку 13 обслуживание очередного экстрематора. Описанный процесс обработки продолжается до окончания заданного времени усреднения сигнала. Процесс вывода результатов анализа начинается с подачи на вход 20 анализатора и далее на четвертый вход блока 14 импульсного сигнала. При этом на восьмом выходе блока 14 формируется код адреса первой ячейки ОЗУ 11, а на пятом вьгхо- де - импульс. По этому импульсу происходит считывание содержимого первой ячейки ОЗУ 11 и запись его в детектор 10. По окончании указанного импульса на втором выходе блока 14 формируется импульс, который поступает на управляющий вход логарифмического преобразователя 9. На вход последнего с выхода детектора 10 в зависимости от сигнала на его первом входе поступает код максимального значения или среднее значение квадрата сигнала. Преобразователь 9 представляет собой постоянное запо- минающее устройство (ПЗУ), в ячейках которого записаны коды логарифмов значений сигнала. Коды значений сигнала, поступающие на вход преобразо0

5

0

0

вателя 9, являются кодами адреса его ячеек, а импульс, поступающий на управляющий вход преобразователя 9 является сигналом, разрешающим считывание содержимого выбранной ячейки, С выхода преобразователя 9 данные поступают на вход блока 7 извлечения квадратного корня и первый вход цифрового коммутатора 8. По окончании импульса на втором выходе блока 14 на его шестом выходе формируется импульс, который поступает на управляющий вход блока 7 и запускает его. Блок 7 обеспечивает извлечение квадратного корня из кода, поступившего на его вход, и yмIioжeниe результата на коэффициент 0,707. Код среднеквадратичных значений сигнала с выхода блока 7 поступает на второй вход коммутатора 8, который в зависимости от сигнала, поступаюпдего на его управляющий вход с первого выхода блока 14, передает на свой выход и далее на индикатор 6 и выход I6 анализатора код, поступающий на его первый или второй входы. На этом вывод содержимого первой ячейки ОЗУ 11 заканчивается. Вывод содержимого второй, тре- т,ьей и т.д. ячеек ОЗУ 11 осуществляется последовательно в соответствии с приведенным описанием. При этом на восьмом выходе блока 14 каждый раз формируется код адреса соответствующей ячейки.

Экстрематор 3 (фиг. 2) работает следующим образом

Установка экстрематора 3 в режим слежения за сигналом осуществляется подачей импульса на его управляющий вход. При этом триггер 32 устанавливается в состояние 1 на прямом выходе, а ключи 23 и 27 замыкаются. Переменное напряжение, поступающее на вход экстрематора 3 через замкнутые ключи 23 и 27 и резисторы 24 и 28 проходит на инвертирующие входы усилителя 26 и компаратора 30. Усилитель 26 с конденсатором 25 в цепи отрицательной обратной связи представляет собой устройство выборки и запоминания, которое в момент прохождения входного напряжения через экстремум автоматически переводится в режим запоминания . При этом экстремум входного напряжения определяется в момент равенства нулю разности между входньш и задержанным относительно него на некоторый временной интервал напряжеo

5

0

5

0

5

0

5

0

5

нием (для обеспечения заданной погрещ- ности определения момента экстремума входного напряжения указанная задержка задается достаточно малой). Величина задержки определяется постоянной времени цепи, состоящей из резистора 24 и конденсатора 25. С выхода усилителя 26 сигнал через резистор 29 поступает на инвертирующий вход компаратора 30, неинвертирующий вход которого соединен с нулевым потенциалом. При этом к инвертирующему входу компаратора 30 прикладывается разность между.,входным напряжением, поступающим через резистор 28, и равным ему по величине, обратным по фазе и за- держанньш во времени напряжением, поступающим с выхода усилителя 26 через резистор 29 (резисторы 28 и 29 . обеспечивают развязку между выходом усилителя 26 и выходом источника переменного напряжения, соединенного с входом экстрематора 3. В случае положительной полуволны входного сигнала указанная разность имеет положи- тельную полярность, а напряжение на выходе компаратора 30 - отрицатель- ную. В момент перехода входного напряжения через максимум, указанная разность становится равной нулю, а затем принимает отрицательную полярность. При этом происходит скачкообразное изменение знака напряжения на выходе компаратора 30 и срабатывает формирователь 31 импульсов, который формирует по переднему фронту сигнала на входе импульс на своем выходе. Этот импульс через схему 34 сборки поступает на управляющий выход эст- рематора 3 и фиксирует момент прохождения входного напряжения через максимум. Кроме того, этот же импульс поступает на соответствуюш 1й вход триггера 32 и опрокидывает его. В результате этого ключи 23 и 27 размыкаются и Экстрематор 3 переводится в режим запоминания максимального значения сигнала, поступающего с выхода усилителя 26 на выход экстрематора 3. В случае отрицательной полуволны входного сигнала знак разности напряжений на входе компаратора 30 и напряжение на его выходе имеют обратные, по сравнению с рассмотренным случаем, полярности. В момент перехода входного напряжения через максимум в результате скачкообразного изменения знака напряжения на выходе

компаратора 30 срабатывает формирователь 33 импульсов, который формирует по заднему фронту сигнала на вхог; де импульс на своем выходе. Этот импульс через схему 34 сборки посту- пает на управляющий выход экстремАто- ра 3 и фиксирует момент прохождения входного напряжегшя через максимум.

Блок 7 извлечения квадратного корня (фиг. 3) работает следующим обра- зом.

При подаче импульса на управляющий вход блока 7 код, поступающий на его вход, записывается в вычитающий счетчик 35, триггер 38 устанав- ливается в состояние 1 на прямом выходе, а счетчик 42 - в исходное состояние.

Данные, поступающие на вход блока 7, представляются в логарифмическом масштабе. С учетом известных свойств логарифмов алгоритм обработки данных по формуле (1) в блоке 7 -может быть представлен в виде

Ig 0,707-IF Ig 0,707 + 1/2 Ig А (2)

где А - код, поступающий на вход блока 7.

Указанный алгоритм обработки реализуется в блоке 7 .с помощью число- импульсного метода.-При этом код логарифма Поступающих данных преобразуется в интервал времени соответствующей длительности, формируемый триггером 38. Передний фронт этого интервала фиксируется импульсом, поступающим на управляющий вход блока 7. На вход вычитающего счетчика 35 с выхода генератора 40 импульсов образцовой частоты через схему 39 совпадения, разблокированную триггером 38, начинают поступать импульсы. Они подаются на вход счетчика 35 до тех пор, пока последний не установится в состояние О, которое фиксируется дешифратором 36 Нуля,. При срабатывании последнего запускается формирователь 37 импульсов, который опроки- дывает триггер 38 в исходное состояние, блокируя схему 39 совпадения и фиксируя тем самым задний фронт временного интервала. В течение указанного интервала времени импульсы с выхода схемы 39 поступают через делитель 41 на два частоты следования и тульсов также на вход счетчика 42. При этом деление частоты следования

5

0

0

5

5

0

5 0 5

импульсов на два обеспечивает операцию извлечения квадратного корня, а умножение результатов этой операции на коэффициент 0,707 обеспечивается предварительной установкой счетчика 42 на величину Ig 0,707 в момент поступления импульса на управляющий вход блока 7. С выхода счетчика 42 код результата поступает на выход

блока 7. I

Блок 10 детектирования (фиг. 4) работает в двух режимах: анализа сигнала и вью ода информации.

В режиме анализа сигнала цикл обработки осуществляется за четыре такта. Запуск блока 10 производится подачей на его третий управляющий вход импульса, который проходит на управляющие входы регистров 43, 46 и 57 и счетчика 60. При этом в регистр 43 записывается код, поступивший на вход блока 10, в регистр 46 - разряды кода D;|-Df|, поступившего на вход-выход блока 10, представляющие собой код максимального значения сигнала, в регистр 57 /- разряды кода В„.,-D;., представляющие собой текущее значение суммы квадратов отсчетов сигнала, в счетчик 60 - разряды кода D,,-D, представляющие собой число усредненных отсчетов сигнала. Указанный импульс устанавливает также триггер 52 в состояние I и разблокировывает .схему 51 совпадения. При наличии.разрешающего сигнала на втором управляющем входе блока 10 импульс с его третьего управляющего входа через схему 48 совпадения своим задним фронтом запускает формирователь 49 импульсов. Импульс с выхода формирователя 49 своим передним фронтом увеличивает содержимое счетчика 60 на единицу, а задним фронтом переписывает содержимое счетчика 60 в регистр 59. Указанный импульс, кроме того, через схему 47 сборки поступает на управляющий вход регистра 43 и вызывает считывание его содержимого, которое поступает на один из входов коммутатора 45 и на оба входа умножителя 44, Последний представляет собой быстродействующее комбинационное устройство для перемножения опе- рантов (в рассматриваемом случае умножитель 44 выполняет операцию возведения в квадрат кода с выхода регистра 43).

Код, поступающий на один из входов коммутатора 45 с выхода регистра 43, сравнивается с кодом, поступающим на его другой вход с выхода регистра 46. При этом, если код в регистре 46 TIO абсолютной величине больше кода, в регистре 43, то коммутатор срабатывает, опрокидывает триггер 52 и тем самым блокирует схему 51 совпадения. Формирователь 49 задним фронтом импульса запускает формирователь 50 импульсов, сигнал с выхода кото- рого поступает на управляющие входы сумматора 54 и регистра 56. При этом осз цествляется запуск сумматора 54 и запись информации в регистр 56. матор 54 суммирует квадрат текущего значения сигнала, код которого поступает с выхода умножителя 44, с суммой квадратов предыдущих значений сигнала,, код которой поступает с выхода регистра 57. При вычислении среднеквадратичных значений сигнала в детекторе 10 используется рекурсивный алгоритм вида

N.

NH

Ni- Ni-,

где N - возведенный в квадрат i-й отсчет сигнала; N., - среднее значение из возведенных в квадрат (i-1) отсчетов сигнала; N - среднее значение из возведенных в квадрат i отсчетов сигнала;

i - число усредненных отсчето Схемотехнически более просто реа- р1изуется следующая модификация выражения (3) :

iN. iN., + N - N

1-1

(4)

45

В соответствии с выражением (4). из полученной суммы с помощью блока 55 вычитается среднее значение из возведенных в квадрат (i-1) отсчетов сигнала. Указанное значение получается в результате деления суммы возве- м денных в квадрат (i-1) отсчетов сигнала, код которой хранится в регистре 57, на код числа усредненных отВ режиме вывода информации на второй управляющий вход блока 10 подается сигнап запрета, который блокирует схему 48. В результате этого цикл обработки осзтцествляется за один такт При подаче импульса на третий управляющий вход блока 10 содержимое соответствующей ячейки ОЗУ 11 переписывается в регистры 46 и 57 и счетчик 60. При этом содержимое регистра 46,

счетов, хранящийся в счетчике 60. Операция деления осуществляется путем « представляющее собой код максимально- соответствующего сдвига кода содер- го значения сигнала, поступает на жимого регистра 57. Указанный сдвиг один вход коммутатора 61. На второй реализуется с помощью коммутатора 58, рход последнего, с выхода коммутатора который управляется кодом с выхода 58 поступает код среднего значения

15

0

5

0

5

0

5

счетчика 60 и подключает каждый раз к своему выходу определенную часть своих входов, выполняя тем самым функцию селектора выходов регистра 57,

С выхода коммутатора 58 код среднего значения из возведенных в квадрат (1-1) отсчетов сигнала - N.;, поступа.ет на один из входов коммутатора 61 и в зависимости от сигнала на управляющем входе последнего про- - ходит или не проходит на выход блока 10. Кроме того, указанньй код поступает на вход регистра 56 и записывается -в него, Формирователь 50 задним фронтом импульса запускает формирователь 53 импульсов, сигнал с выхода которого поступает на управляющие входы блока 55 и регистра 59, на вход схемы 51 совпадения и на управляющий выход блока 10. При этом, блок 55 осуществляет вычитание из содержимого сумматора 54 содержимое регистра 56 и выдает результат на разряды кода D -D входа-выхода блока 10. Кроме того, считывается содержимое регистра 59, которое поступает на разряды кода Dj -D входа-выхода блока 10. Импульс с выхода формирователя 53 поступает также на один из входов схемы 51 совпадения. Если указанная схема оказывается разблокированной, то импульс проходит на ее выход и далее через схему 47 сборки поступает на управляющий вход регистра 43 и вызывает считывание содержимого последнего, которое поступает на разряды кода D,-Df, входа-выхода блока 10. Информация, поступающая на вход-выход блока 10, записьшается в соответствующую ячейку ОЗУ 11 импульсом с управляющего выхода блока 10. На этом цикл обработки информации в блоке 10 за- : канчивается.

В режиме вывода информации на второй управляющий вход блока 10 подается сигнап запрета, который блокирует схему 48. В результате этого цикл обработки осзтцествляется за один такт. При подаче импульса на третий управляющий вход блока 10 содержимое соответствующей ячейки ОЗУ 11 переписывается в регистры 46 и 57 и счетчик 60. При этом содержимое регистра 46,

представляющее собой код максимально- го значения сигнала, поступает на один вход коммутатора 61. На второй рход последнего, с выхода коммутатора 58 поступает код среднего значения

13

из возведенных в квадрат значений сигнала, В зависимости от сигнала, поступившего на первьш управляющий вход блока 10, коммутатор 61 подает на выход последнего один из указанных кодов.

Блок 14 управления (фиг. 5) работает следующим образом.

При программировании анализатора перед началом его работы на первый и третий входы блока 14 подаются соот- ветственно коды коэффициента усиления сигнала и времени усреднения последнего. Запись этих кодов в регистр 76 и счетчик 77 осуществляется импульсом с выхода формирователя 79, кото- рьй запускается сигналом, поступающим на второй вход блока 14 при запуске aHajfti3aTopa., Код коэффициента усиления с выхода регистра 76 поступает на десятый выход блока 14, .Импульс с выхода формирователя 79, кроме того, поступает на третий выход блока 14, а также на один из входов триггера 71, устанавливая его в состояние 1. Сигнал с выхода триггера 71 поступает на четвертый выход блока 14, а также разблокировьгоает схемы 63, 64 и 66 совпадения. Тактовые импульсы с выход-а генератора 67 через схему 66 поступают на вычитающий вход счетчика 77 до тех пор, пока последний не установится в состояние О, которое фиксируется дешифратором нуля 72. Срабатывая-, депшфратор 72 запускает формирователь 68, импульс с выхода которого устанавливает триггер 71 в состояние О и блокирует схемы 63 и 66. Таким образом, триггер 71 формирует временной интервал, в течение которого осуществляется усреднение сигнала при измерении его СКЗ.. Импульс, поступающий на восьмой вход блока 14, устанавливает триггер 62 в состояние О и формирует на девятом выходе блока 14 сигнал запрета. Кроме того, указанный импульс поступает на один из входов схемы 63 и проходит на.седьмой выход блока 14 в течени :интервала усреднения сигнала,так как схема 63 в течение этого времени остается разблокированной. Импульсы, поступающие на седьмой вход блока 14 через разблокированную в процессе усреднения сигнала схему 64 совпадения и далее через схему 65 сборки проходят на пятый выход блока 14. При вьшоде ин0892714

формации на четвертый вход блока 14 подается сигнал, который запускает формирователь 80. Импульс с выхода последнего поступает на один из вхо- 5 Дов триггера 78, устанавливая его в .

триггера 78, состояние 1, и на вход предварительной установки счетчика 74, устанавливая его в состояние О. Кроме того, указанным импульсом произ 0 водится синхронизация установки триггера 82 в состояние, определяемое сигналом, поступающим на пятый вход блока 14. При выводе максимальных значений сигнала на пятый вход блока

J5 14 подается 1, а при выводе СКЗ сигнала - О. Сигнал с выхода триггера 82 поступает на первый выход блока 14. Сигналом с выхода триггера 78 разблокировываются группа 73 вентилей и схема 69-совпадения, через которую на суммирующий вход счетчика 74 начинают поступать тактовые импульсы с выхода генератора 67. При этом код с выхода счетчика 74, представляющий собой код адреса ячеек ОЗУ 1I, через группу 73 вентилей поступает на восьмой выход блока 14. Кроме того, тактовые импульсы поступают на вход формирователя 75, импульсы с выхода которого поступают на второй выход блока 14, а также на вход формирователя 70, запуская последний своими задними фронтами. Импульсы с выхода формирователя 70 по35 ступают на шестой выход блока 14, После о-проса всех ячеек ОЗУ 11 сигнал переноса со старшего разряда счетчика 74 поступает на один из входов триггера 78, устанавливая его в

40 состояние О и блокируя группу 73 вентилей и схему 69, Кроме того, указанный сигнал запускает формирователь 81. Импульс с выхода последнего поступает на одиннадцатый выход блока

45 14 и сигнализирует об окончании про20

25

30

цесса вьшода информации.

Формула изобретения

I, Третьоктавный спектральньй анализатор, содержащий, входной усилитель, вход которого соединен с входом анализатора, а выход - с входами третьоктавных полосовых фильтров, аналоговый коммутатор, выход которого подключен к входу аналого-цифрового преобразователя (АЦП), индикатор, вход которого соединен с выходом анализатора, и оперативное запоминающее

ш

15

151308927

устройство (ОЗУ), отличающийся тем, что, с целью расширения функциональных возможностей анализатора за счет возможности измерения максимальных значений сигнала в соответствующих полосах частот, в него введены экстрематоры, блок детектирования , логарифмический преобразователь, блок извлечений квадратного корня, цифровой коммутатор, блок приоритетных прерываний, дешифратор и блок управления, при этом выход каждого фильтра соединен с входом соответствующего экстрематора, выходы которых подключены каждый к соответствующему входу аналогового коммутатора, выход АЦП соединен с- входом блока детектирования, выход которого подключен к входу логарифмического преобразователя, выход кото- рого соединен с первым входом цифрЬ- вого коммутатора и входом блока извлечения квадратного корня, выход которого подключен к второму входу цифрового, коммутатора, выход которого соединен с входом индикатора и выходом анализатора, первый, второй, третий, четвертый и пятый управляющие входы которого подключены соответственно к первому, второму, третьему, четвертому и пятому входам блока управления, первый выход которого соединен с первым управляющим входом блока детектирования и управляющим входом цифрового коммутатора, второй выход блока управления подключен к управляющему входу логарифмического преобразователя, управляюшлй выход блока детектирования соединен с шесупды уп эк ра вх бл вх ко бл бл ля пр со от уп бл ца уп

0 ля со

ч то ра те ре фр эт

вх хо ст ду об

35 ка ра че щи ющ

25

тым входом блока управления и первым инвертирующему входу операционного управляющим входом ОЗУ, второй управ- усилителя и к нулевому потенциалу.

ляющии вход которого подключен к тре- тьег-гу выходу блока управления, четвертый выход которого соединен с вторым управляющим входом блока детектирования, третий управляющий вход которого пЪдключен к третьему управляющему -входу ОЗУ и пятому выходу блока управления, шестой и седьмой

выходы которого соединены соответст- 50 экстрематора, выход триггера соедивенно с управляюшр ми входами блока извлечения квадратного корня и АЦП, управляющий выход которого подключен к седьмому входу-блока управления и

5

927

16

управляющему входу депшфратора, каждый из .выходов которого соединен с управляюшим входом соответствующего экстрематора, восьмой выход блока управления подключен к управляющему входу аналогового коммутатора, выходу блока приоритетных прерываний и к входам дешифратора и ОЗУ, вход-выход которого соединен с входом-выходом блока детектирования, девятый выход блока управления подключен к управляющему входу блока приоритетных прерываний каждый из входов которого соединен с управляюш 1М выходом соответствующего экстрематора, а его управляющий выход - с восьмым входом блока управления, десятый и одиннадцатый выходы которого подключены к управляющему входу входного усилите0 ля и управляющему выходу анализатора соответственно.

2. Анализатор по п. 1, отличающийся тем, что экстрема- тор содержит два ключа, три резистора, конденсатор, операционньа усилитель, компаратор, формирователь переднего фронта, формирователь заднего фронта, схему сборки и триггер, при этом вход экстрематора подключен к

входам первого и второго ключей, выход первого ключа через первый рези- стор подключен к инвертирующему входу операционного усилителя и к одной обкладке конденсатора, другая обклад5 ка которого соединена с выходом операционного усилителя и экстрематора и через второй резистор с инвертирующим входом компаратора, неинвертирующий вход которого подключен к не5

выход компаратора соединен с входами формирователей переднего и заднего фронтов, выходы которых подключены к 45 первому и второму входам схемы сборки, выход которой соединен с управляющим выходом экстрематора и первым входом триггера, второй вход которого подключен к управляющему входу

нен с управляющими входами ключей, вьрсод второго ключа через третий резистор подключен к инвертир-ующему входу компаратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Спектральный анализатор | 1987 |

|

SU1613969A1 |

| Устройство для определения угловых положений указателей стрелочных приборов | 1988 |

|

SU1504515A1 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Устройство для преобразования сейсморазведочной информации | 1987 |

|

SU1497599A1 |

| Устройство для определения местоположения источника акустической эмиссии | 1987 |

|

SU1499224A1 |

| СПУТНИКОВАЯ СИСТЕМА СВЯЗИ "КИБОЛ" | 1992 |

|

RU2033693C1 |

| Способ спектрального анализа сигналов | 1985 |

|

SU1308928A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1043692A1 |

| Устройство для измерения фазового сдвига | 1988 |

|

SU1661668A1 |

Изобретение относится к области измерения характеристик случайных сигналов. Цель изобретения - расширение функциональных возможностей TTTTil 17 tS tS го 2t 22 фаг. t анализатора. Анализатор содержит . входной усилитель 1, третьоктавные фильтры 2.1-2.П, аналоговый коммутатор 4, аналого-цифровой преобразователь 5, индикатор 6 и оперативное устройство 11. Введение экстремато- ров 3.1-З.п, блока 7 извлечения квадратного корня, цифрового коммутатора 8,логарифмического преобразователя 9,блока 10 детектирования, дешифратора 12, блока 13 приоритетных прерываний и блока 14 управления обеспечивает возможность измерения максимальных значений сигнала в соответствующих полосах частот. 1 з. п.ф-лы, 5 ил. je (П 00 о 00 со го

Риг.З

VlLZ.

Составитель В, Смолин Редактор О. Юрковецкая Техред А.Кравчук Корректор М. Шароши

1793/36

Тираж 731 Подписное ВНИИШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектна я, 4

fpuz. 5

| Клюкин И | |||

| И., Колесников А | |||

| Е | |||

| Акустические измерения в судостроении | |||

| - Л.: Судостроение, 1982, ,с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-05-07—Публикация

1985-09-16—Подача