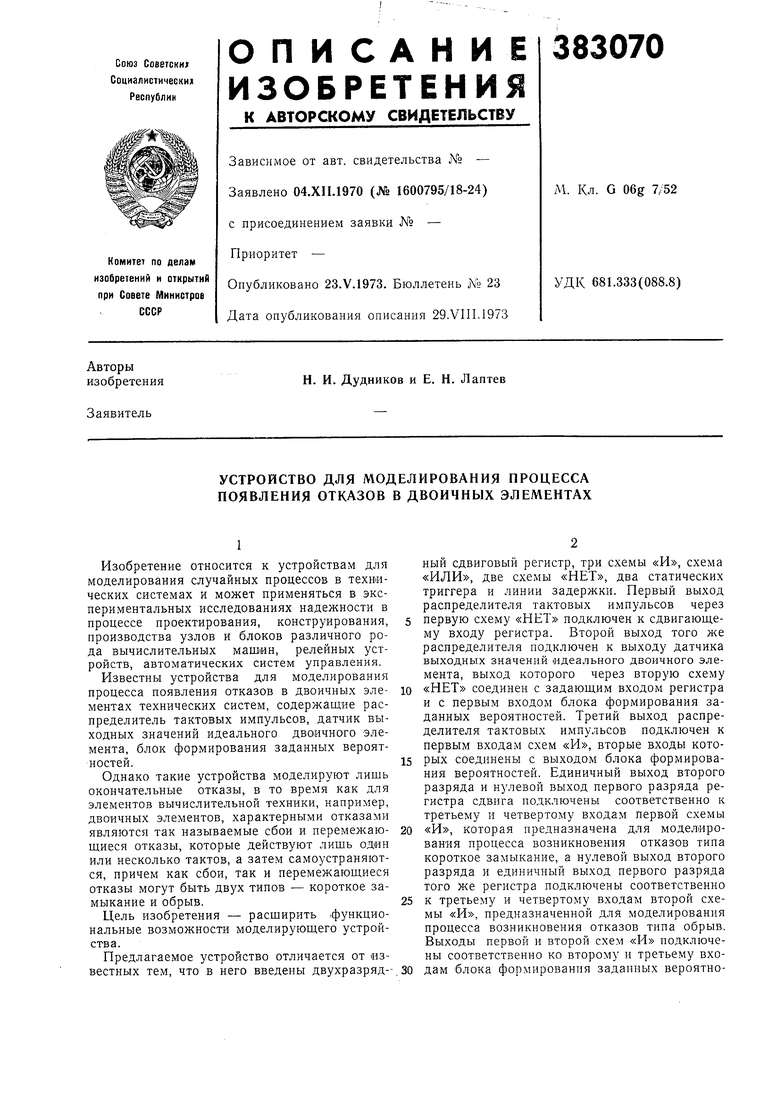

Изобретение относится к устройствам для моделирования случайных процессов в технических системах и может применяться в экспериментальных исследованиях надежности в процессе проектирования, конструирования, производства узлов и блоков различного рода вычислительных машин, релейных устройств, автоматических систем управления. Известны устройства для моделирования процесса появления отказов в двоичных элементах технических систем, содержащие распределитель тактовых импульсов, датчик выходных значений идеального двоичного элемента, блок формирования заданных вероятностей. Однако такие устройства моделируют лишь окончательные отказы, в то время как для элементов вычислительной техники, например, двоичных элементов, характерными отказами являются так называемые сбои и перемежающиеся отказы, которые действуют лишь один или несколько тактов, а затем самоустраняются, причем как сбои, так и перемежающиеся отказы могут быть двух типов - короткое замыкание и обрыв. Цель изобретения - расширить функциональные возможности моделирующего устройства. Предлагаемое устройство отличается от известных тем, что в него введены двухразрядный сдвиговый регистр, три схемы «И, схема «ИЛИ, две схемы «НЕТ, два статических триггера и линии задержки. Первый выход распределителя тактовых импульсов через первую схему «НЕТ подключен к сдвигающему входу регистра. Второй выход того же распределителя подключен к выходу датчика выходных значений идеального двоичного элемента, выход которого через вторую схему «НЕТ соединен с задающим входом регистра и с первым входом блока формирования заданных вероятностей. Третий выход распределителя тактовых импульсов подключен к первым входам схем «И, вторые входы которых соединены с выходом блока формирования вероятностей. Единичный выход второго разряда и нулевой выход первого разряда регистра сдвига подключены соответственно к третьему и четвертому входам первой схемы «И, которая предназначена для моделирования процесса возникновения отказов типа короткое замыкание, а нулевой выход второго разряда и единичный выход первого разряда того же регистра подключены соответственно к третьему и четвертому входам второй схемы «И, предназначенной для моделирования процесса возникновения отказов типа обрыв. Выходы первой и второй схем «И подключены соответственно ко второму и третьему входам блока формирования заданных вероятностеи и через линии задержки к единичным входам первого и второго триггеров. Выход третьей схемы «И, предназначенной для моделирования процесса самоустранения отказов, подключен через линию задержки к нулевым входам первого и второго триггеров. Единичные выходы триггеров подключены к входам схемы «ИЛИ, выход которой соединен с запрещающими входами первой и второй схем «НЕТ и с третьим входом третьей схемы «И. Нулевые выходы первого и второго триггеров подключены к пятым входам соответственно первой и второй схем «И. Первый вход блока формирования вероятностей предназначен для настройки блока на формирование вероятности отказа типа короткое замыкание или типа обрыв, второй вход - на формирование вероятности самоустранения отказов типа короткое замыкание, третий вход-на формирование вероятности самоустранения отказов типа обрыв. На чертеже приведена функциональная схема устройства. Предлагаемое устройство содержит блок 1 формирования заданных вероятностей, состоящий из генератора 2 случайных импульсов, который вырабатывает импульсы со случайной длительностью пауз между соседними импульсами, двоичного счетчика 3, имеющего п-разрядов, схемы совпадения 4, регистра 5 ДЛЯ запоминания п-разрядного двоичного числа, выходного триггера 6, блока 7 регистров для запоминания и хранения 4 п-разрядных двоичных чисел, несимметричного триггера 8 для фиксации значения выхода двоичного элемента и схемы 9 «ИЛИ. Блок 1 предназначен для формирования четырех вероятностей: первой, численно равной интенсивности отказов типа короткое замыкание, второй, численно .равной интенсивности отказов типа обрыв, третьей, численно равной вероятности самоустранения отказов типа короткое замыкание, и четвертой, численно равной вероятности самоустранения отказов типа обрыв. Кроме того, в устройство входит распределитель 10 тактовых импульсов на три выхода и датчик 11 выходных значений идеального двоичного элемента. Датчик // предназначен для формирования последовательности нулей и единиц, отображающих выходные значения идеального (не подверженного отказам) двоичного элемента. Расширение функциональных возможностей устройства достигнуто за счет введения в него двухразрядного сдвигового регистра 12, трех схем 13, 14 и 15 «И, двух статист ических триггеров 16, 17, схемы 75 «ИЛИ, двух схем 19 и 20 «НЕТ и линий задержки 21, 22 и 23, которые совместно с блоком 1 формирования заданных вероятностей, датчиком 11 выходных значений идеального двоичного элемента и распределителем 10 тактовых импульсов позволяют моделировать процессы возникновения и самоустранения сбоев и перемещающихся отказов типа короткое замыкание и типа обрыв. Реглстр 12 состоит из двух триггеров 24 и 25 и линии задержки 26. Он предназначен для формирования двухразрядных двоичных последовательностей, отображающих настоящее и ближайшее прошлое значение выхода двоичного элемента. На сдвиговый вход с регистра 12 через схему 19 «НЕТ подаются тактовые сигналы с выхода распределителя 10 тактовых импульсов, поэтому состояние триггера 24 регистра отображает ближайшее прошлое значение выхода двоичного элемента. На задающий выход регистра 12, а следовательно, и на единичный выход триггера 25 через схему 20 «НЕТ по сигналу с выхода 27 распределителя 10 тактовых импульсов подается настоящее значение (нулевое или единичное) выхода двоичного элемента. Схемы 13 и 14 «И предназначены для моделирования процесса возникновения отказов соответственно типа короткое замыкание и типа обрыв. Для этого третий и четвертый входы этих схем соединены с триггерами регистра таким образом, чтобы при поступлении сигналов на первые -входы с выхода 27 распределителя 10, а на вторые входы с выхода триггера 6, на выходе схемы 13 «И сигнал появился только тогда, когда настоящее значение выхода датчика 11 равно нулю, а ближайшее прошлое - единице, а на выходе схемы «И 14, когда настоящее значение выхода того же датчика равно единице, а ближайшее прощлое - нулю. Креме того, схема 13 «И предназначена для настройки блока 1 формирования заданных вероятностей на вероятность самоустранения отказа типа короткое замыкание, а схема 14 «И - на вероятность самоустранения отказа типа обрыв. Схема 15 «И предназначена для моделирования процесса самоустранения отказов. Статические триггеры 16 и 17 предназначены для запоминания отказов соответственно типа короткое замыкание и типа обрыв. Для этого единичные входы триггеров соединены с выходами соответствующих схем «И 13 и 14, а нулевые входы - с выходом схемы 15 «И. Таким образом, триггер 16 будет в единичном состоянии в течение всего времени действия отказа типа короткое замыкание с момента его появления до самоустранения. Это справедливо и для триггера 17 в случае отказа типа обрыв. Схема «ИЛИ предназначена для управления схемами «НЕТ. Ее выход является запрещающим входом для схем «НЕТ. Схема «НЕТ предназначена для прекращения процесса моделирования отказов, когда устройство зафиксировало появление отказа, и для возобновления процесса моделирования, если устройство зафиксировало самоустранение отказа. Линии задержки 21, 22 и 23 предназначены ля задержки подаваемых .на вход триггеров 16 и 17 импульсов на время действия импульса, поступающего из распределителя на первые входы схем 13, 14 и 15 «И.

Предлагаемое устройство работает следующим образом.

Исходными данными для моделирования являются программа значений выхода идеального двоичного элемента, интенсивность отказов типа короткое замыкание A,i моделируемого двоичного элемента, интенсивность, отказов типа обрыв 1о, интенсивность самоустранения отказов типа короткое замыкание %, и интенсивность самоустранения отказов типа обрыв Ко того же элемента.

Перед началом работы в датчик // выходных значений идеального двоичного элемента вводится программа изменения этих значений. В блок регистров 7 записываются четыре разрядных числа, первое k 1.2, второе Xt.Xo-2, третье А,г2« и четвертое ,:„ Хо-2.

Включается генератор 2 случайных импульсов, в качестве которого может использоваться генератор белого щума с последующим ограничением и формированием случайных импульсов. Длительность паузы между соседними импульсами в этом случае будет распределена по показательному закону с плотностью а. Средняя частота импульсов на выходе генератора 2 будет равна fcpi a. Частота fcp, (может достигать значений 10- 10 гц.

Импульсы с генератора 2 поступают на двоичный счетчик 3. Переполнение счетчика 3 будет наступать всякий раз при подаче импульса (,2...). Выходной триггер 6 управляется счетчиком 3 и схемой совпадения 4. Пусть триггер 6 в начальный момент времени находился в состоянии, когда на его выходе был высокий потенциал. Пусть далее в регистр 5 записано число.Д. Тогда при поступлении из генератора 2 в счетчик 5 k того импульса из схемы совпадения 4 на триггер б поступает сигнал, переводящий его в состояние, когда на его выходе будет более низкий потенциал. При поступлении импульса счетчик 3 и триггер 6 возвращаются в исходное состояние и т. д.

Таким образом, триггер 6 формирует на вь1ходе случайные импульсы высокого потенциала, математическое ожидание длительности которого М - . Если взять достаточно а

отдаленный от начала момент времени, то вероятность наличия на выходе триггера 6 высокого потенциала равна fe/2 Л средняя частота- импульсов на этом же выходе будет равна fcp2 -„

Указанная вероятность будет являться при моделировании одной из величин

2

К-. X,,/„,,,,),„ т. е. X, /.„

К

АГ, . ) -о

2 ° 2

Выбор чисел k, ,., ).;, k., из блока регистра 7 и запись их в регистр 5 производится следующим образом. Так как отказ типа

короткое замыкание может произойти лишь при изменении значения выхода идеального двоичного элемента с единичного на нулевое, а отказ типа обрыв - при изменении значения выхода того же элемента с нулевого на

единичное, то при выдаче датчиков // нуля 1 есимметричный триггер 8 формирует нмпульс на своем нулевом вы.ходе, а при выдаче тем же датчиком единицы на единичном выходе. Эти сигналы с триггера 8 подаются ка

блок регистров 7 н на схему 9 «ИЛИ. Сигнал с выхода схемы 9 «ИЛИ используется для сброса в нуль триггеров регистра 5, т. е. для его очистки. Сигналы, подаваемые с нулевого или единичного выходов триггера 8 на блок 7

регистров, используются для выбора соответственно числа ft),, или fe ).„ из блока регистров 7 и для записи их в регистр 5. Выбор чисел АХ, и k),,, производится по сигналам со схем 13 и 14 «И, т. е. после того как в моделируеMOM двоичном элементе произошел отказ. При этом, если произошел отказ типа короткое замыкание, сигнал очистки регистпа 5 и для выбора числа fr.., в блоке регистров 7 подается со схемы 13 «И, если же произонгел отказ

типа обрыв, то подобный сигнал подается го схемы 14 «И и производится выбор числа.

Таким образом производится пепестронка блока / в процессе работы устройства. После настройю блока / и ввода программы В-датчик // выходных значений идеального двоичного элемента включается генератор (распределитель) 10 тактовых импульсов. Работа устройства происходит циклически. Устройство работает в двух режимах - режиме

моделирования процесса возникновения отказов и режиме моделирования процесса самоустранения отказов, причем эти режимы чередуются. При работе в режиме моделирования процесса возникновения отказов схемы 19 « 20 «НЕТ открыты, так как триггеры 16 и 17 находятся в нулевом состоянии, т. е. на единичных их выходах низкий потенциал, в результате чего на выходе схемы «ИЛИ будет также низкий потенниал. При подаче импульса с выхода 27 распределителя 10 импульсов сигнал подается через схему 19 «НЕТ на сдвиговый вход регистра 12. в результате чего осуществляется перенос числа из триггера 25 в

триггер 24, т. е. в триггер 24 записывается ближайшее прошлое значение выхода идеального двоичного элемента. Затем с выхода 28 распределителя 10 импульсов подается сигнал на датчик // выходных значений идеального

двоичного элемента. По этому сигналу датчик

выдает в устройство очередное, т. е. для данного цикла настоящее значение выхода идеального двоичного элемента, которое, во-первых, записывается в триггер 24 регистра 12, а во-вторых, производит перестройку триггера 8, а вместе с ним и всего блока 1. При этом могут быть четыре варианта сочетания состояний ближайшее прошлое и настояш,ее, которым соответствуют четыре двухразрядных двоичных числа регистра 12: 00, И, 10, 01. В первом и третьем варианте блок / настраивается на вероятность К во втором и третьем - на вероятность ЯоПосле этого нодачей импульса с выхода 28 распределителя 10 возбуждаются первые входы схем 13, 14 и 15 «И, пятые входы схем 13 и 14 «И возбуждены, так как триггеры 16 и 17 находятся в нулевом состоянии 1И высокий потенциал на нулевых выходах этих триггеров возбуждает пятые входы схем 13 и 14 «И. Если в регистре 12 записано число 00 или 11, то возбуждения выхода схем 13 и 14 «И не происходит, так как один из входов этих схем к моменту поступления импульса с выхода 28 распределителя 10 не будет возбужден. Этим самым отображается тот факт моделей отказов.элементов дискретных систем, согласно которому возникновение отказов не является невозможным событием только в моменты изменения состояния выхода элемента с единицы на нуль (короткое замыкание) Либо с нуля на единицу (обрыв).

Если в регистре 12 записано число 10, то третий и четвертый входы схемы 13 «И будут возбуждены. В момент подачи импульса с выхода 28 распределителя 10 второй вход, а следовательно, и выход этой схемы будет возбужден с вероятностью. В том случае, когда второй вход схемы 13 не возбужден, отказа типа короткое замыкание не происходит, в результате чего устройство приступает к реализации следующего цикла моделирования процесса возникновения отказов для очередного значения выхода идеального двоичного элемента. В том же случае, когда вход схемы 13 возбужден, возбуждение выхода этой схемы моделирует возникновение отказа типа короткое замыкание. При этом блок / перестраивается на вероятность ATi самоустранение отказа типа короткое замыкание, триггер 16 переходит в единичное состояние, в результате чего через схему 18 «ИЛИ подается сигнал запрета на схемы 19 и 20 «НЕТ, возбуждается третий вход схемы 15 «И и снимается возбуждение с пятого входа схемы 13 ;%И. Тем самым прекращается моделирование процесса возникновения отказов, и устройство переходит на режим моделирования процесса сам оустранения отказов.

Если в регистре 12 к моменту поступления сигнала с выхода 28 распределителя 10 было записано число 01, то будут возбуждены третий и четвертый выходы схемы 14 «И, что

обеспечивает возбуждение выхода этой схемы с вероятностью о- В случае, когда второй вход схемы 14 не возбужден, происходит моделирование безотказной работы двоичного элемента. При возбзждении второго входа схемы 14 моделируется возникновение отказа типа обрыв. При этом блок / перестраивается на вероятность А,о самоустранения отказа типа обрыв, триггер 17 переходит в единичное состояние, в результате чего через схему 18 «ИЛИ подается сигнал запрета на схемы 19 и 20 «НЕТ, возбуждается третий вход схемы 15 «И и снимается возбуждение с пятого входа схемы 14 «И, прекращается моделирование процесса возникновения отказов, и устройство переходит на режим моделирования процесса самоустранения отказов.

При работе в режиме моделирования самоустранения отказов схемы 19 и 20 «НЕТ закрыты, поэтому никаких изменений в регистре 12 не происходит. Кроме того, перестройка блока по сигналам с датчика 11 не происходит. При подаче импульса с выхода 28 распределйтеля 10 импульсов возбуждается первый вход схемы 15 так как третий вход этой схемы возбужден, то вероятность возбуждения ее выхода будет равна вероятности возбуждения второго входа, а последняя, в

свою очередь, равна вероятности самоустранения отказов К или А,о в зависимости от того, какой отказ произошел. Если в момент опроса схемы 15 «И второй вход не был возбужден, то распределитель 10 переходит к следующему циклу моделирования самоустранение отказов. Если не к моменту опроса схемы 15 второй ее вход был возбужден, то возбудится и ее выход, что приведет к подаче сигнала на нулевые входы триггеров 16 и 17, и тот триггер, который к этому времени был в единичном состоянии, переходит в нулевое. Возвращение триггера в нулевое состояние приводит к снятию запрета со схем 19 и 20 «НЕТ, к снятию возбуждения с третьего входа схемы

15 «И и к возбуждению пятого входа соответствующей схемы 13 или 14 «И. Устройство вновь переходит на режим моделирования процесса появления отказов.

В зависимости от того, какие числа и записаны в блок регистров 7, можно моделировать окончательные отказы, сбои или перемежающие отказы. Если k -Q или k „ 0, то моделирования самоустранения отказов типа короткое замыкание или типа обрыв происходить практически не будет. Если k, 0 или k, 0, то соответствующий отказ самоустранится при моделировании практически на следующем цикле работы распределителя 10 импульсов. В первом случае будут моделироваться окончательные отказы, во втором - сбои. При или ) будут моделироваться перемещающиеся отказы либо типа короткое замыкание, либо типа обрыв.

Авторы

Даты

1973-01-01—Публикация