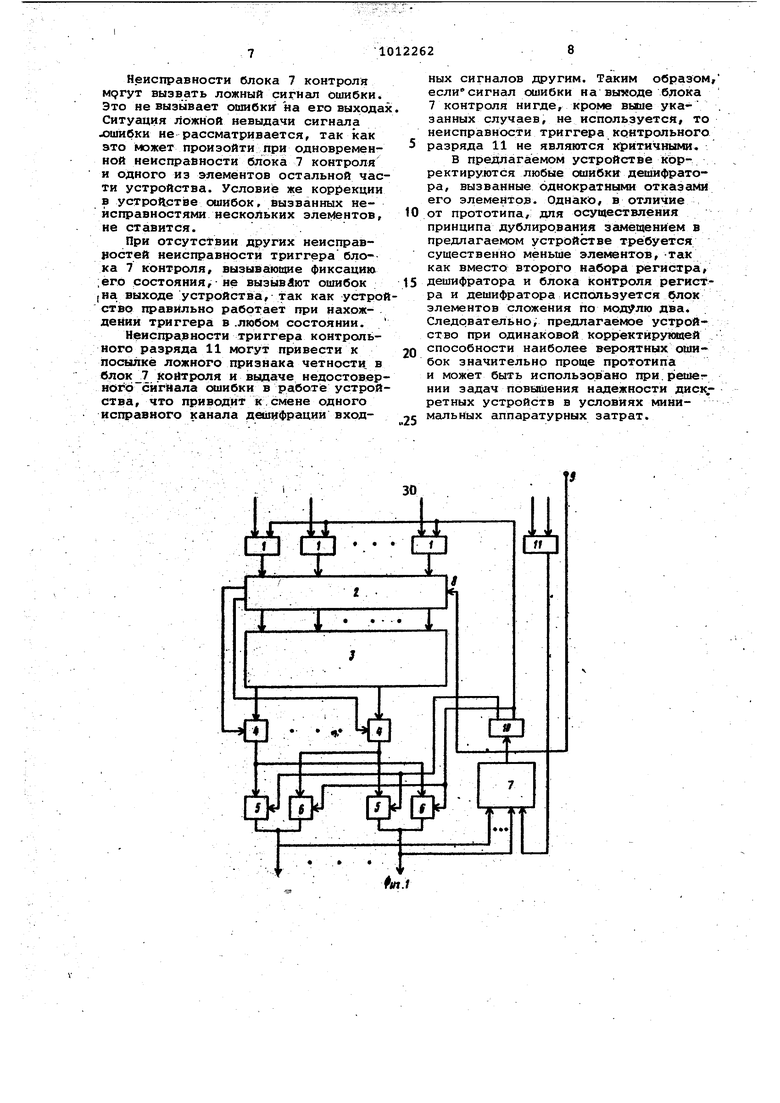

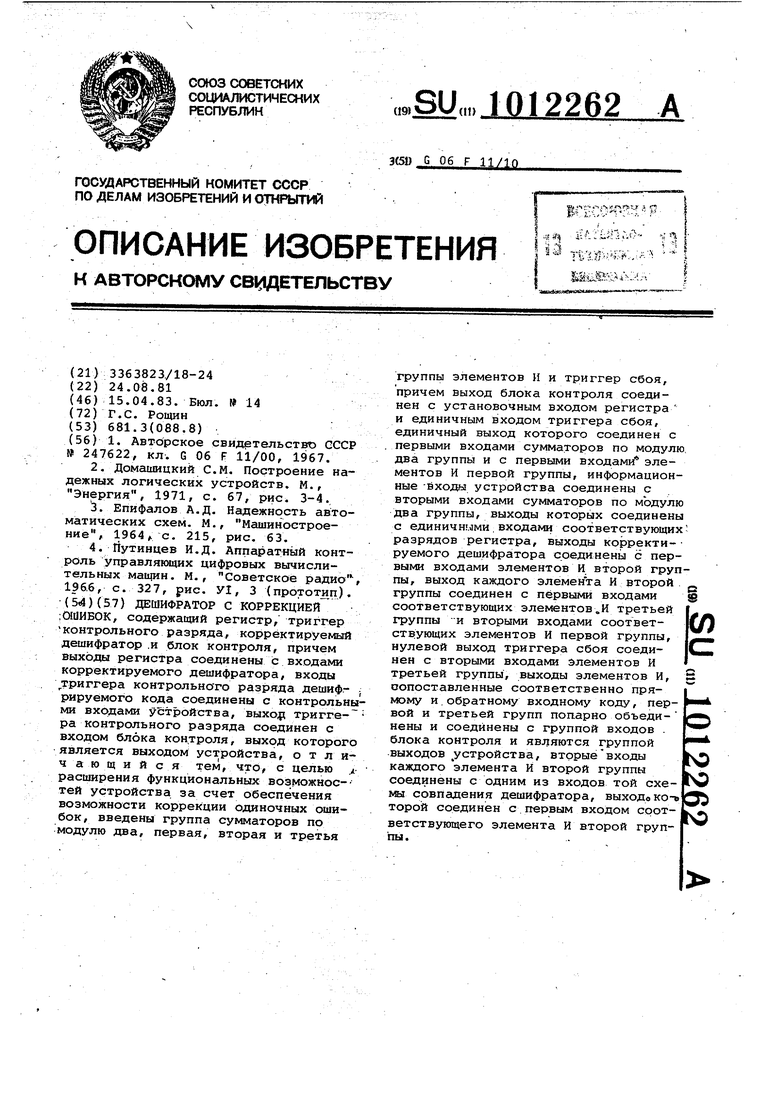

Изобретение относится к области автоматики и вычислительной техники и может найти применение в вычислительных устройствах, в системах автоматизированного управления и конт роля повьошенной надежности. Известно трехканальное резервиро ванное устройство для мажоритарного выбора, содержащее элементы совпадения, связанные с выходом через элементы сборки. Коррекция ошибок каждого из каналов осуществляется на основе принципа большинства fl. Недостатком этого устройства явл ется большая аппаратурная избыточность, а также наличие предела в повышении надежности, определяемого уро,внем надежности мажоритарных органов. Известно двухканальное резервированное устройство, содержащее в каждом канале резервируемые блоки, выходы которых соединены с входами восстанавливающих ррганов 23 Коррекция ошибок в этом устройстве осуществляется за счет маскирования нулевыми сигналами исправно го канала ошибок типа О - 1 неиспра ного при использовании в качестве восстанавливающего органа элемента И и маскирования единичными сигна лами исправного канала ошибок типа 1- О неисправного при использовани в качестве восстанавливающего орган элемента ИЛИ. По структуре такое устройство является наиболее просты Однако такое устройство может быть более надежным, чем одноканаль ное, только в случае преобладания одного типа ошибок. Это не позволяет эффективно применять данные устройства, когда отличие вероятностей обоих типов ошибок незначительно. Известно также двухканальное устройство для резервирования замещением, содержащее в каждом канале резервируемые блоки, соединенные с блоком контроля, выходы которого соединены с управляющими входами блока переключения, информационные входы которого соединены с выходами резервируемых блоков, а информацион ные выходы - с выходами устройства0 При нормальной работе каналов к выходу устройства подключен один и каналов. При отказе данного канала фиксируемом блоком контроля, этот канал отключается и подключается второй исправный. Устройство может работать также и по другому принцип при нормальной работе каналов к выходу подключены оба канала, после отказа одного из каналов последний отключается, а подключенным остаетс исправный. Недостатком этого устройства является большая аппаратурная избыточность. Наиболее близким к предложенному по техническому решению является дешифратор с контрольным разрядом по четности, содержащий входной регистр и схему контроля по модулю два, содержащую первый ивторой элементы ИЛИ, схему сравнения, причем выходы дешифратора соединены с входами соответствующих элементов ИЛИ, входы которых соединены со схемой сравнения, управляющий вход которой соединен с выходом триггера контрольного разряда,, выход схемы сравнения является выходом устройства . Недостатком такого устройства являются узкие функциональные возможности (устройство может только зафиксировать факт неверной работы дешифратора. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности коррекции одиночных ошибок дешифратора.. Поставленная цель достигается тем, что в дешифратор с коррекцией ошибок, содержащий регистр, триггер контрольного разряда, корректируемый дешифратор и блок контроля, причем выходы регистра соединены с входами корректируемого дешифратора, входы триггера контрольного разряда дешифрируемого кода соединены с контрольными входами устройства, выход триггера контрольного разряда соединен с входом блока контроля, выход которого является выходом устройства, введены группа сумматоров по модулю два,первая,вторая и третья группы элементов И и триггер сбоя, причем выход блока контроля соединен с установочным входом регистра и единичным входом триггера сбоя, единичный выход которого соединен с первыми входами сумматоров по модулю два группы и с первыми входами элементов И первой группы, информационные входы устройства соединены с вторыми входами сумматоров по модулю два группы, выходы которых соединены с единичными входами соответствующих разрядов регистра, выходы корректируемого дешифратора соединены с первыми входами элементов И второй группы, выход каждого элемента И второй группы соединен с первыми входами соответствующих элементов И третьей группы и вторыми входами соответствующих элементов 1L первой группы, нулевой выход триггера сбоя соединен с вторыми входами элементов И третьей группы, выхо:ды элементов И, сопоставленные соответственно прямому и обратному входному коду, первой и третьей групп попарно объединены и соединены с группой входов блока контроля и яв ляются.группой выходов устройства. вторые входы к&ждого элемента И вто рой группы соединены с одним из вхо дов той схемы совпадения дешифратора, выход которой соединен с первым входом соответствующего элемента И второй группы. . На. фиг. 1 приведена структур.ная схема предлагаемого устройства на фиг. 2 - структурная схема блока кон роля. Информационные входы устройства через группу сумматоров 1 по модулю два соединены с входами триггеров регистра 2, выходы которого соедине ны с входами корректируемого дешифратора 3, каждый выход которого сопо.ставленный подаваемому на вход матрицы прямому коду, последователь но через соответствующий элемент И второй группы 4 и элемент И третьей группы 5, а соответствующий ему выход дешифратора 3, сопоставленный и вертированному коду, -последова:телън через элемент И второй группы 4 и элемент И первой группы б соединен с. выходом .устройства, сопоставленны подаваемому на вход регистра 2 прям му коду, управляющий вход каждого элемента И второй группы 4 соединен с одним из входов той схемы совпадения дешифратора 3, выход которой соединен с управляемым входом этого элемента И второй группы 4, при этом выход блока 7 контроля соединен с входом 8 обнуления регистра 2 выходом 9 запроса вторичной посылки в устройство дешифрируемого прямого кода, а также со счетным входом триггера 10 сбоя, инверсный выход которого соединен с управляющими входами элементов И третьей группы 5, а основной.выход - с управляющим входами элементов И первой группы б и -входами группы сумматоров 1 по модулю два. Входы блока 7 контроля соединены с выходами устройства, а также с выходом триггера контрольного разряда 11. . В состав блока 7 контроля входят первый 12 и второй 13 сумматоры по модулю два, первый элемент И 14, первый элемент НЕ 15, второй .элемен И 16, второй 17 и третий 18 элементы НЕ и элемент ИЛИ-НЕ 19. Блок 7 контроля фиксирует следующие ошибки; отсутствие на выходе возбужденной шины, вызванное неиспЬ авностью схемы совпадения или одного из ключей/ возбуждение лишней шины, вызванное неисправностью со впадения;.-ил и ключа третьей группы возбуждение одной, но не-той шины, которая должна быть возбужден вызванное неисправностью одного из триггеров регистра. Устройство работает следующим образом. При поступлении на входы дешифратора 3 единичной комбинации сигна-, лов на выходе дешифратора 3 появляется единичный сигнал, который через соответствующий элемент И второй группы 4, открытый одним из единичных входных сигналов соответствующей схемы совпадения дешифратора 3, поступает на входы соответствующего элемента И третьей группы 5 и элемента И первой группы б. В случае исправной работы устройства триггер 10 находится в исходном состоянии, при котором единичный сигнал с инверсного выхода триггера поступает на управляющие входы элементов И третьей группы 5, разреядая прохождение на выходы устройства, сопоставленные прямым кодам на входах устройства, единичных сигналов с выводов элементов И первой группы 6, сопоставленных прямым кодам на входах дешифратора 3. Элементыи третьей труппы 5 в .данном случае остаются в закрытом состоянии, так как сигнал на основном выходе триггера 10 нулевой. Блок контроля 7 работает следующим образом. При подаче на исправное устройство комбинации двоичных сигналов с четным числом единиц триггер контрольного разряда 11 находится в единичном состоянии, а на одном из выходов устройства, подключенных к сумматору 12, появтугется единичный сигнал . В соответствии с логикой работы сумматора 12 на его выходе появляется также единичный сигнал, при этом на выходе второго сумматора 13 - нулевой сигнал. При такой комбинации значений переменных сигнал ошибки должен быть равен нулю. При подаче на вход устройства комбинации двоичных сигналов с нечетным числом единиц, блок работает аналогично, только триггер контрольного разряда 11 находится в нулевом состоянии, на выходе второго сумматора 13 - единичный сигнал, а на выходе сумматора 12 - нулевой. Для данной комбинации значений переменных сигнал сядибки также равен нулю. При появлении любой из перечис ленных однократных ошибок, одна из переменных принимает противоположное значение. Это приводит к тому, что при любой комбинации дяоичных сигналов (с четным или нечетньм числом единиц на. выходе блока контроля появляется единичный сигнал ошибъ ки. Единичный сигнал ошибки на входе 8 обнуляет регистр 2, а по счетному входу изменяет состояние триггера 10. При этом элементы И третьей

Группы 5 закрываются, запрещая прохождение на выходы устройства, сопоставленные прямым кодам на входах устройства, сигналов с выходов элементов И второй группы 4, сопоставленных прямым кодам на входах дешифратора 3, а элементы И nepBoff группы 6 открываются, разрешая прохождение на выходы устройства, сопоставленные прямым кодам на входах устройства, сигналов с выходов элементов И второй группы 4, сопоставленных соответствующим инвертированным кодам на входах дешифратора 3.

При этом инвертирование кода происходит на сумматорах 1 по модулю Два за счет подачи на их входы единичного сигнала с основного выхода триггера 10, а вторичная посылка кода на схемы происходит по сигналу блока 7 контроля на выходе 9. При Появлении очередной ошибки сигнал с блока 7 контроля приводит устройство в исходное состояние.

Таким образом, сигнал на любом из выходов устройства может формироваться двумя каналами: схема совпадения, дешифрующая прямой код - элемент И 4 второй группы - элемент И 4 второй группы - выход устройства, схема совпадения,дешифрирующая инвертированный сумматорами 1 прямой код, - элемент И второй группы 4 лемент И третьей группы 5.

Включение одной группы элементов И и выключение другой происходит по сигналу Ошибка с выхода блока 7 контроля.

Устройство при появлении описанных выше ошибок, вызванных неисп1 авностями или сбоями в работе конкрет;ных элементов, работает следующим образом.

Неисправность триггера регистра 2 проявляется тогда, когда при подаче входного сигнала, требующего изменения его состояния, он остается в прежнем состоянии. В результате на дешифратор 3 подается другой код а на выходе устройства возбуждается не тот выход, который должен быть возбужден под действием входных сигналов устройства. Это обнаруживается блоком 7 контроля и после вторичной посылки сигналов на вх:оды устройства происходит их инвертирование. В результате этого новый сигнал на входе неисправного триггера не требует изменения его состояния, т.е. неисправность не проявляется. Возбуждение выхода устройства, сопоставленному поданному на входы устpoftcfJBa прямому коду, происходит в этом случае по второму каналу, а первый будет закрыт соответствующим элементом И третьей группы 5.

Неисправности схем совпадения дешифратора 3 могут привести к аналогичной ошибке на одном чп HI.IXOJIOH устройства (возбуждению лншнехо пыхода), если соответствующигг неисправной схеме совпадения элемент И второй группы 4 будет закрыт. Влияние ошибки устраняется после инвертиро-, вания сигналов на входах схемы совпадения дешифратора 3, так как на соединенный с управляющим входом элемента И второй группы 4-вход схем совпадения дешифратора 3 подается вместо единичного инвертированный (нулевой сигнал, который закрывает пропускающий ложный сигнал элемента И третьей группы 5..

Неисправности, вызывающие ошибки типа 1- О, приводят к аналогичным ошибкам на выходах устройства (отсутствие возбужденной шины. Влияние этих ошибок устраняется за счет воз буждения необходимого выхода устройства по второму каналу, осуществляемого после инвертирова.ния входных сигналов..

Неисправности сумматоров 1 по модулю два могут привести к установк в ложное состояние одного из триггеров, в результате чего возбуждается другая выходная шина устройства, что обнаруживается блоком 7 контроля. Под действием сигнала ошибки изменяет, свое состояние триггер 10, в результате чего изменяется один из входных сигналов неисправного элемента. Это приводит к тому, что несоответствие определяемого логикой работы выходного сигнала и ложного устраняется, все триггеры регистра устанавливаются в заданное состояние и на выходе устройства возбуждается заданная ипна.

Любая неисправность одного из элементов И первой, вьорой или третьей групп может быть критична только в том случае, когда управляющий сигнал требует его противоположного по отношению к вызванному неисправностью (неисправностями состояния.

При обнаружении блоком 7 контроля ошибок, вызванных такими неисправностями (отсутствие возбужденного выхода при обрыве входа элемента И или возбуждение второго выхода при коротком замыкании элемента, изменяется триггер 10, и на неисправный элемент И подается управляющий сигнал, непротиворечащий вызванному неисправностью состоянию. При этом сигнал с выхода некоторой схемы совпадения дешифратора 3, ложно проводимый (непроводимый) на выход устройства, снимается, так как единичный набор вход нызГ си гнал о в этой заменяется нулевыми, а возбуждение необходимого выхода происходит по каналу дешифрацийинвертированного кода. Неисправности блока 7 контроля мргут вызвать ложный сигнал ошибки. Это не вызывает ошибкк на его выхода Ситуация ложной невыдачи сигнала аэшис}ки не рассматривается, так как это может произойти при одновременной неисправности блока 7 контроля и одного из элементов остальной час ти устройства. Условие же коррекции в устройстве ошибок, вызванных неисправностями нескольких , не ставится. При отсутствии других неисправностей неисправности триггера блока 7 контроля, вызывающие фиксацию ;его состояния,-не вызывают ошибок ,на. выходе устройства, так как устрой ство правильно работает при нахож- . дении триггера в .любом состоянии. Неисправности триггера контрольного разряда 11 могут привести к посылке ложного признака четности, в контроля и выдаче недостоверного сигнала ошибки в работе устройства, что приводит к смене одного исправного канала дешифрации входных сигналов другим. Таким образом, если сигнал ошибки на выходе блока 7 контроля нигде, кроме выше указанных случаев, не используется, то неисправности триггера контрольного разряда 11 не являются критичными. В предлагаемом устройстве корректируются любые ошибки дешифратора, вызванные однократными отказами его элементов. Однако, в отличие от прототипа, для осуществления принципа дублирования замещением в предлагаемом устройстве требуется существенно меньше элементов,-так как вместо второго набора регистра, дешифратора и блока контроля регистра и дешифратора используется блок элементов сложения по модулю два. Следовательно; предлагаемое устройство при одинаковой корректируквдей способности наиболее вероятных ошибок значительно проще прототипа и может быть использовано при.р ешетнии задач повьайения надежности дискретных устройств в условиях минимальных аппаратурных затрат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| КОЛЬЦЕВОЙ ДЕШИФРАТОР | 1972 |

|

SU342298A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1076952A1 |

| Устройство для записи-воспроизведения многоканальной информации | 1984 |

|

SU1190410A1 |

| Устройство для кодирования | 1985 |

|

SU1287294A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Устройство для контроля и коррекции информации | 1980 |

|

SU940160A1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1988 |

|

SU1580568A1 |

ДЕШИФРАТОР С КОРРЕКЦИЕЙ ;ОШИБОК, содержащий регистр, триггер контрольного разряда, корректируемый дешифратор .и блок контроля, причем выходы регистра соединены с входами корректируемого дешифратора, входы триггера контрольного разряда дешиф- ; рируёмого кода соединены с контрольными входами устройства, выхор тригге- ра контрольного разряда соединен с входом блока кон.троля, выход которого является выходом устройства, о т л ич а ю щ и и с я тем, что, с целью ./ расширения функциональных возможное-тей устройства за счет обеспечения возможности коррекции одиночных ошибок, введены группа сумматоров по модулю два, первая, вторая и третья I.., .. ;;п, .-.- группы элементов И и триггер сбоя, причем выход блока контроля соединен с установочным входом регистра и единичным входом триггера сбоя, единичный выход которого соединен с первыми входами сумматоров по модулю два группы и с первыми входами элементов И первой группы, информационные -входы устройства соединены с вторыми входами сумматоров по модулю два группы, выходы которых соединены с единичными входами соответствующих разрядов регистра, выходы корректи- руемого дешифратора соединены с первыми входами элементов И второй груп пы, выход каждого элемента И второй . группы соединен с первыми входами соответствующих элементов.И третьей (Л группы И вторыми входами соответствующих элементов И первой группы, нулевой выход триггера сбоя соединен с вторыми входами элементов И третьей группы, выходы элементов И, сопоставленные соответственно прямому и.обратному входному коду, первой и третьей групп попарно объединены и соединены с группой входов . блока контроля и являются группой ВЫХОДОВ устройства, вторыевходы каждого элемента И второй группы соединены с одним из входов той схемы совпадения дешифратора, выходе ко- торой соединен с.первым входом соответствующего элемента И второй группы .

Авторы

Даты

1983-04-15—Публикация

1981-08-24—Подача