1

Изобретение относится к области автоматики и вычислительной техники.

Известны устройства для пересчета не совпадающих по времени импульсов, содержащие триггеры с подключенными к их выходам эмиттерными повторителями, резистивно-диодный сумматор, источник постоянного напряжения, переключатель, резисторы и выходной дифференцирующий усилитель.

Цель изобретения - повыщение быстродействия.

Предлагаемое устройство отличается от известных тем, что в нем входы триггеров соединены со входными клеммами, а выходы эмиттерных повторителей подключены через резистивно-диодный сумматор ко входу выходного дифференцирующего усилителя, котоj)bf: через резисторы и переключатель присоединен к источнику ПОСТОЯННОГО напряжения.

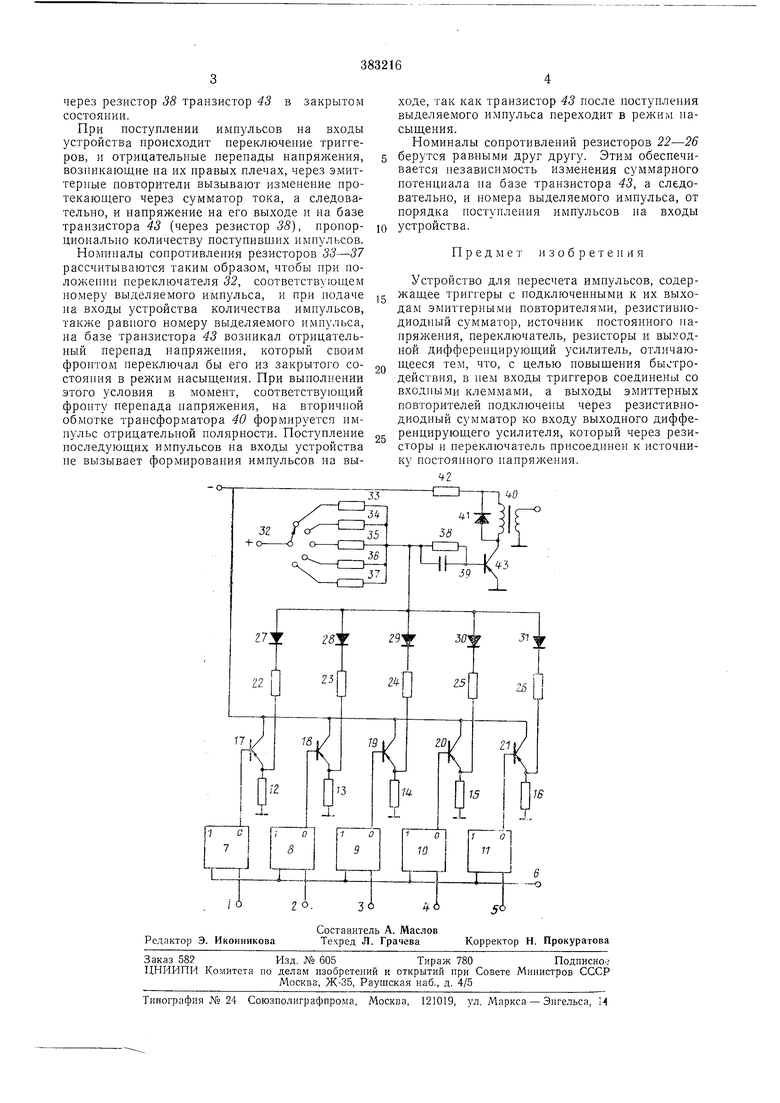

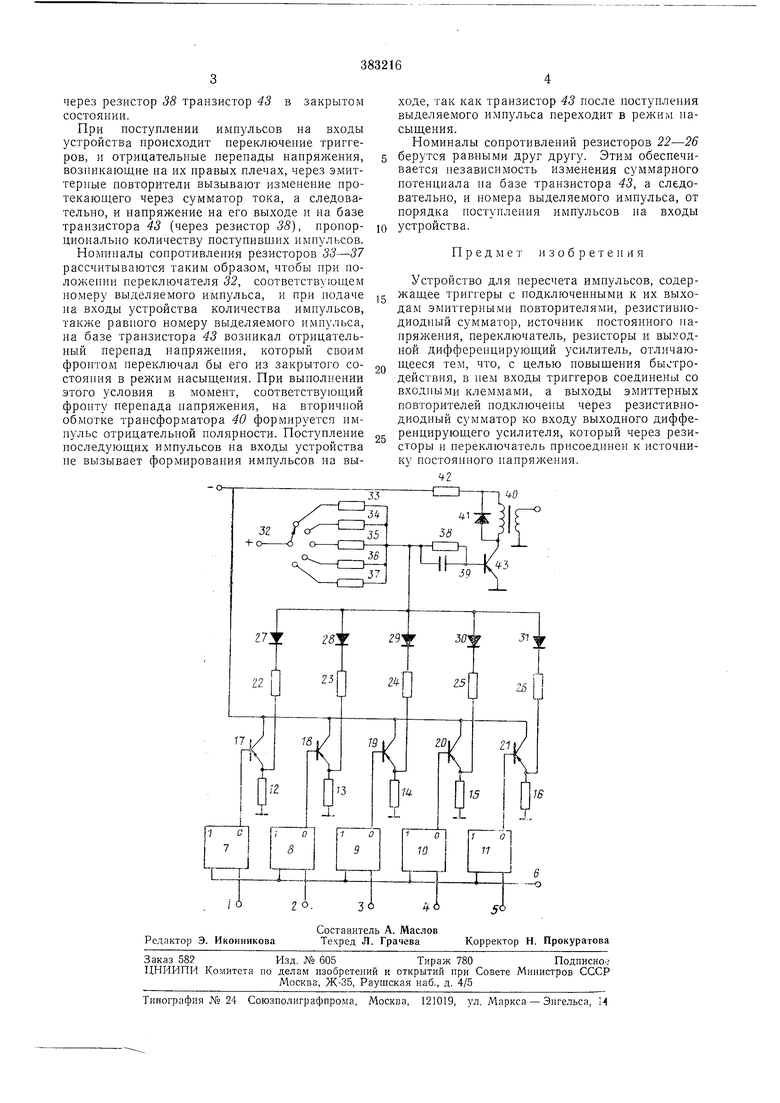

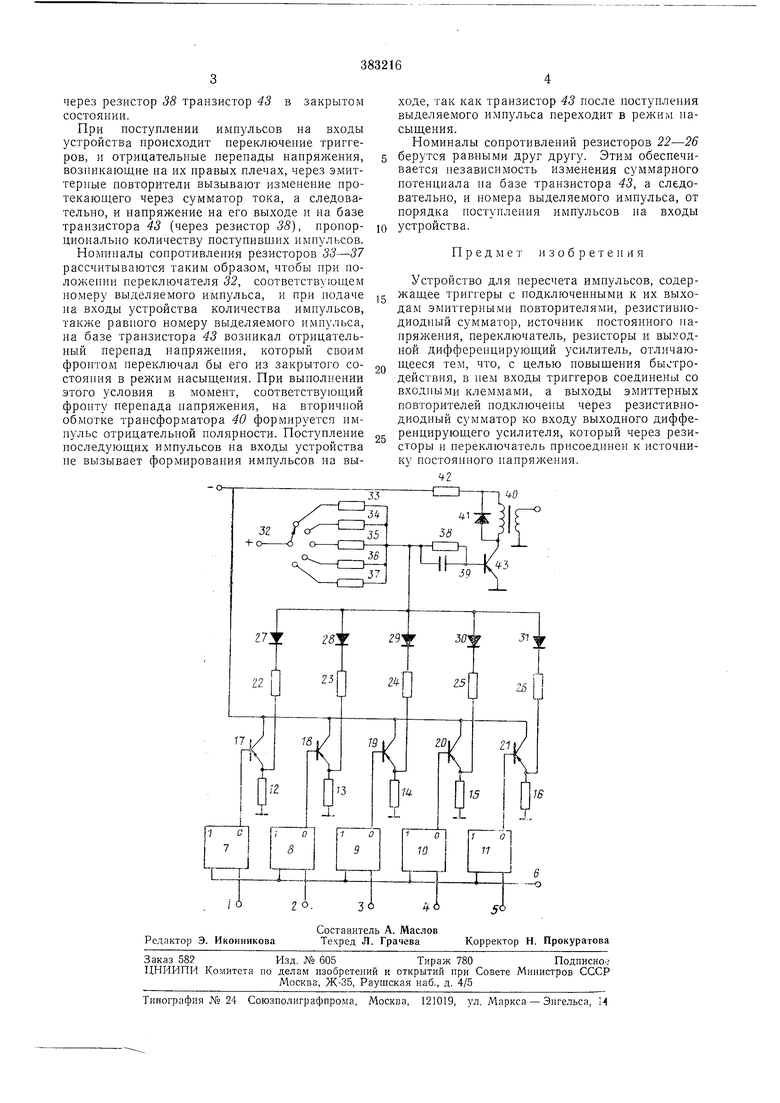

На чертеже приведен вариант схемы устройства на пять параллельных входов, обеспечивающего выделение от I до 5 импульсов.

Входами устройства являются выводы /-6 потенциальных триггеров 7-//, нравые плечи которых нагружены на эмиттерные повторители, выполненные на резисторах 12-16 и транзисторах 17-21.

Эмиттерные повторители нагружены на резисторный сумматор с диодной сборкой (резисторы 22-26 и диоды 27-31) и выполняют по отношению к нему функцию независимых

источников потенциальных сигналов. Положительные выводы диодов сборки объединены и являются выходом сумматора, который через коммутируемые переключатели 32, резисторы 33-37 соединен с источником напряжения положительной полярности (на чертеже не показан), а через ценочку, состоящую из резистора 38 и конденсатора 39, со входом дифференцирующего усилителя. Коллекторной нагрузкой дифференцирующего усилителя является импульсный трансформатор 40, последовательно с первичной обмоткой которого, щунтированной диодом 41 для гащения положительных выбросов напрялч:ения, включен резистор 42, ограничивающий коллекторный ток транзистора 43. Выходом устройства является вывод вторичной обмотки импульсного трансформатора.

Установка устройства в исходное состояние осуществляется подачей импульса отрицательной полярности на все потенциальные триггеры 7-// по входу 6. В исходном состоянии на правых плечах триггеров устанавливается нулевой, а на левых - отрицательный потенциалы (на схеме соответственно «О и «1).

Через один из резисторов 33-37, диоды 27-31 и резисторы 22-26 сумматора и через резисторы 2-16 эмиттерных повторителей протекает ток источника положительной полярности, за счет которого на выходе сумматора создается падение напряжения, поддерживающее

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1980 |

|

SU886225A1 |

| РЕГУЛИРУЕМЫЙ ПРЕЦИЗИОННЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ С ДВУПОЛЯРНЫМ ВЫХОДОМ | 1991 |

|

RU2037871C1 |

| ДВУХТАКТНЫЙ УСИЛИТЕЛЬ МОЩНОСТИ | 2002 |

|

RU2298282C2 |

| Импульсный модулятор | 1978 |

|

SU765998A1 |

| Трехфазный тиристорный ключ | 1979 |

|

SU851777A1 |

| УСТРОЙСТВО ПОДДЕРЖАНИЯ РЕЖИМА РАБОТЫ ПО ПОСТОЯННОМУ ТОКУ УСИЛИТЕЛЯ | 2001 |

|

RU2207712C2 |

| Стабилизированный источник питания | 1981 |

|

SU993228A1 |

| Пороговое устройство | 1984 |

|

SU1251019A1 |

| Двухтактный релаксатор | 1978 |

|

SU765987A1 |

| Стабилизированный преобразователь постоянного напряжения | 1989 |

|

SU1700539A1 |

Авторы

Даты

1973-01-01—Публикация