1

Изобретение относится к области вычислительной техники и си,стем автоматического поиска информации и .предназначено для использования в качестве базового элемента устройств последовательного дешифрирования (многотактвых дешифраторов).

Известно устройство для автоматического однозначного поиска информации, выполняющее последовательное дешифрирование, для которого используются входные многоразрядные регистры (для промежуточного запоминания символов входного алфавита), входные дешифраторы и дешифрирующая матрица. Для запоминания одного символа входного алфавита здесь требуется несколько двоияных запоминающих элементов, причем основное запоминание производится в оперативном запоминающем устройстве (ОЗУ) информационной машины, что требует обращения к ОЗУ в процессе дешифрирования и потому снижает быстродействие устройства.

Предложенная ячейка многотактного дешифратора отличается тем, что первый вход первой схемы совпадения соединен со входной шиной данной ячейки, а второй вход этой же схемы совпадения соединен с выходами усилителей предыдущих ячеек многотактного дешифратора, выход усилителя данной ячейки соединен со входом второй схемы совпадения этой же ячейки и со входами первых

схем совпадения последующих ячеек, выход схемы «ИЛИ соединен с нулевым входом входного триггера, а входы соединены с нулевыми выходами входных триггеров последующих ячеек, нулевой выход входного триггера данной ячейки соединен со входами схем «ИЛИ предыдущих ячеек.

Это позволяет упростить ячейку в результате использования только одного элемента памяти для запоминания символа входного алфавита, расширить функциональные возмож ности многотактного дещифратора путем расширения словаря в процессе эксплуатации информационной машины, ПОВЫСИТЬ быстродействие многотактного дешифратора в результате исключения обрашений к ОЗУ машины.

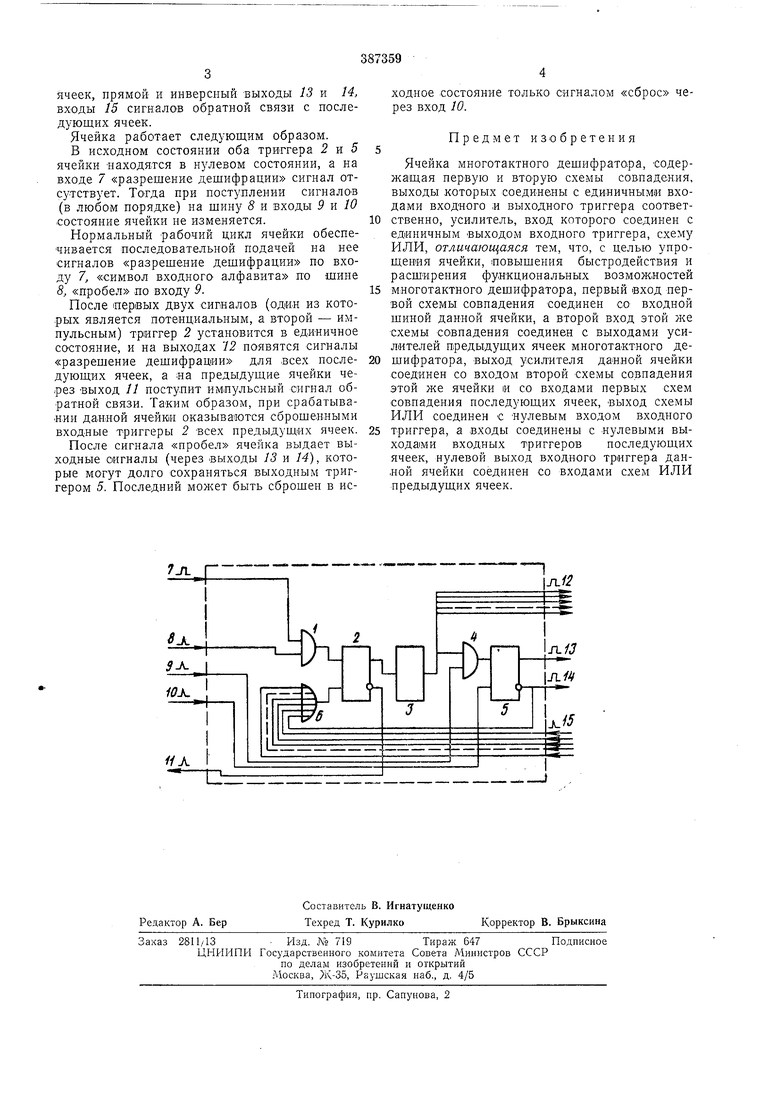

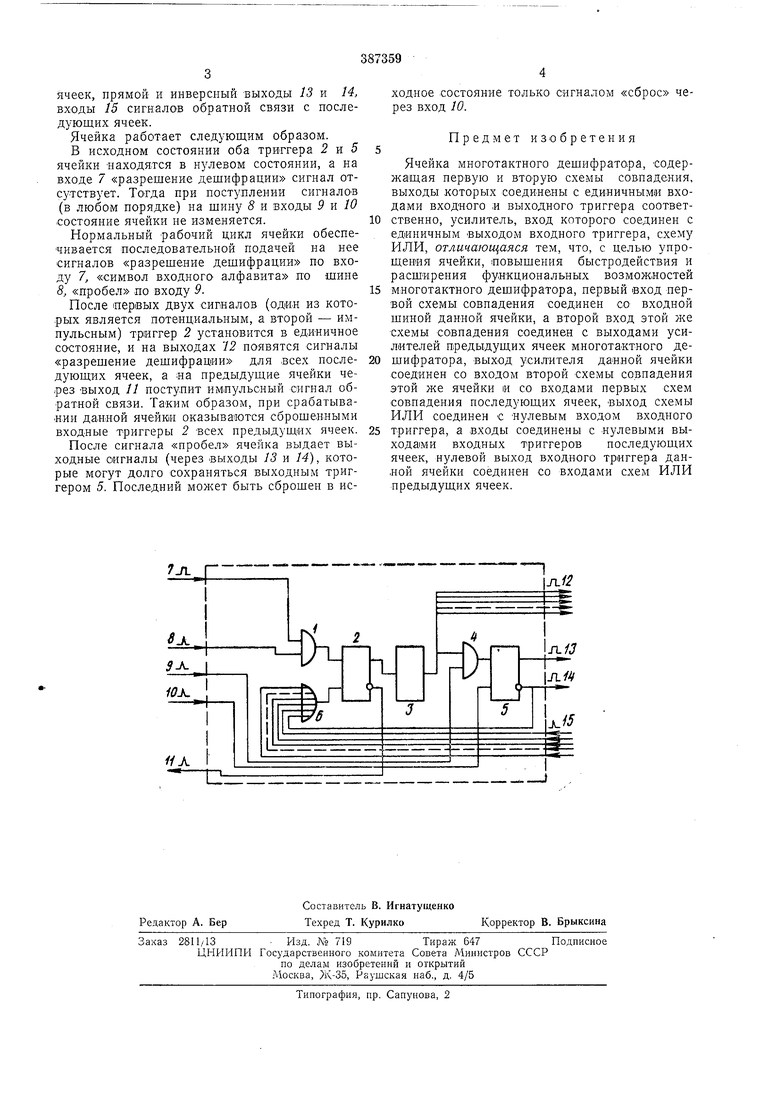

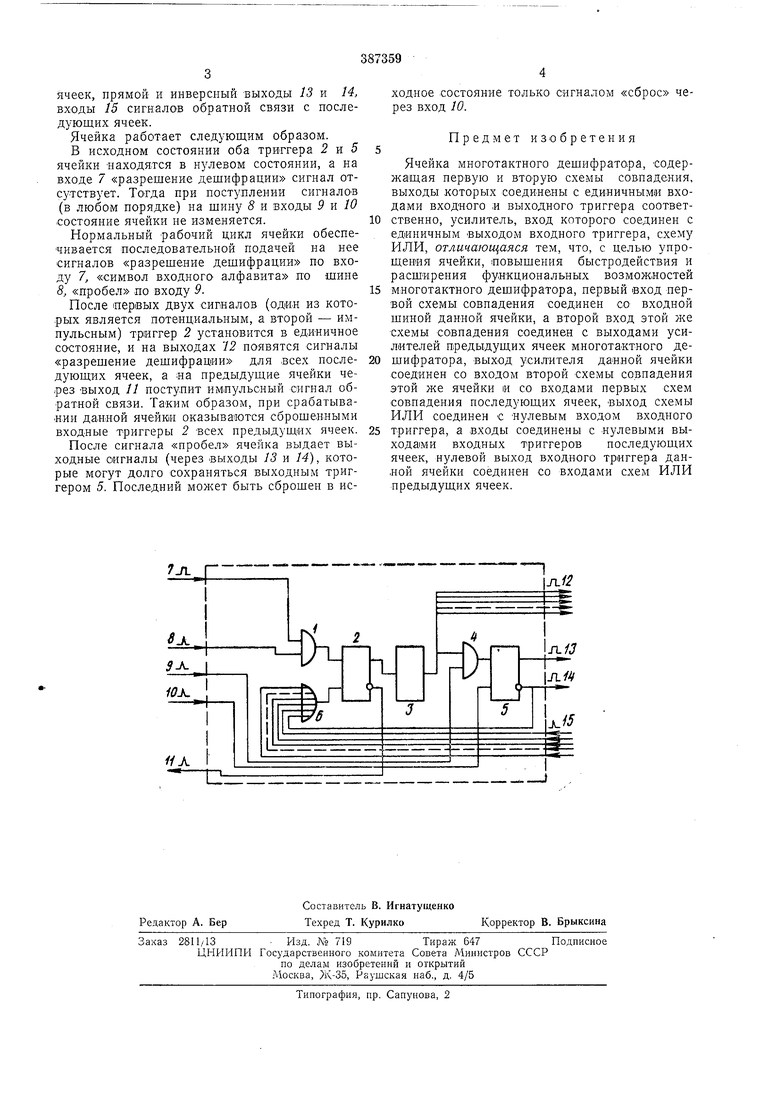

На чертеже изображена схема предложенной ячейки.

Ячейка содержит схему совпадения /, входной триггер 2, усилитель 3, схему совпадения 4, выходной триггер 5, схему «ИЛИ 6, вход 7 «разрешение дешифрации, который соединен с выходами усилителей 3 предыдущих ячеек, входную шину 8, по которой подается сигнал «символ входного алфавита, вход 9 сигнала «пробел (окончание слова), вход Ю сигнала «сброс, выход 11 сигнала обратной связи, соединенный со входами схем «ИЛИ 6 предыдуших ячеек, выходы 12 сигналов «разрешение дешифрации для последующих

ячеек, прямой и инверсный выходы 13 и 14, входы 15 сигналов обратной связи с последующих ячеек.

Ячейка работает следующим образом.

В исходном состоянии оба триггера 2 и 5 ячейки яаходятся в нулевом состоянии, а на входе 7 «разрещение дешифрации сигнал отсзтствует. Тотда при поступлении сигналов (в любом порядке) на шину 8 и входы 9 и 10 состоянне ячейки не изменяется.

Нормальный рабочий цикл ячейки обеспечивается последовательной подачей на нее сигналов «разрешение дешифрации по входу 7, «символ входного алфавита яо щипе 8, «пробел по входу 9.

После первых двух сигналов (одии из которых является потенциальным, а второй - импульсным) триггер 2 установится в единичное состояние, и на выходах 12 появятся сигналы «разрещение дешифрации для всех последующих ячеек, а иа предыдущие ячейки через ВЫХОД 11 поступит импульсный сигнал обратной связи. Таким образом, при срабатывании данной ячейки оказывааотся сброщенными входные триггеры 2 всех предыдущих ячеек.

После сигнала «пробел ячейка выдает выходные сигналы (через выходы 13 и 14), которые могут долго сохраняться выходным триггером 5. Последний может быть сброшен в исходное состоянне только сигналом «сброс через вход 10.

Предмет изобретения

Ячейка многотактного дешифратора, содержащая первую и вторую схемы совпадения, выходы которых соединены с единичными входами входного и выходного триггера соответственно, усилитель, вход которого соединен с единичным выходом входного триггера, схему ИЛИ, отличающаяся тем, что, с целью упрощения ячейки, повыщения быстродействия и расширения функциональных возможностей

многотактного дешифратора, первый вход первой схемы совпадения соединен со входной шиной данной ячейки, а второй вход этой же схемы совпадения соединен с выходами усилителей предыдущих ячеек многотактного дешифратора, выход усилителя данной ячейки соединен со входом второй схемы совпадения этой же ячейки и со входами первых схем совпадения последующих ячеек, выход схемы ИЛИ соединен с нулевым входом входного

триггера, а входы соединены с нулевыми выходами входных триггеров последующих ячеек, нулевой выход входного триггера данной ячейки соединен со входами схем ИЛИ предыдущих ячеек.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный дешифратор | 1977 |

|

SU705442A1 |

| Устройство распознавания многосимвольных слов | 1980 |

|

SU938279A1 |

| КОЛЬЦЕВОЙ ДЕШИФРАТОР | 1972 |

|

SU342298A1 |

| Последовательный дешифратор | 1977 |

|

SU734665A1 |

| Устройство для автоматического формирования строки к фотонаборной машине | 1979 |

|

SU1024309A1 |

| Последовательный дешифратор слов | 1981 |

|

SU978138A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| Биотехническое адаптируемое устройство для бесклавишного ввода информации | 1987 |

|

SU1576901A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ЗАКОНА УПРАВЛЯЮЩЕГО ВОЗДЕЙСТВИЯ | 1969 |

|

SU255659A1 |

| СПОСОБ И УСТРОЙСТВО СЖАТИЯ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ АССОЦИАТИВНОЙ ПАМЯТИ | 1995 |

|

RU2159989C2 |

М,

Авторы

Даты

1973-01-01—Публикация