Устройство относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передач с временным уплотнением.

Известно устройство для цикловой синхронизации [1], содержащее регистр сдвига, три схемы совпадения, блок выделения тактовой частоты, три анализатора совпадения синхросигнала, генератор импульсов, два элемента ИЛИ, три элемента НЕ, решающее устройство, два элемента И, элемент ИЛИ-НЕ, соединенные определенным образом.

Данное устройство обеспечивает повышение помехоустойчивости цифровых систем передач с временным уплотнением при искажении помехами управляющих сигналов о наличии или отсутствии стаффинга.

Однако указанное устройство имеет следующие недостатки. Реализация в нем последовательного поиска синхронизации увеличивает время вхождения в синхронизм, а применение входного регистра, особенно при синхронизации цифровых передач с рассредоточенной синхрокомбинацией, увеличивает его аппаратные затраты, т.к. разрядность регистра равна длине, в позициях, цикла передачи, длина которой может достигать нескольких тысяч позиций.

Наиболее близким по технической сущности к заявленному изобретению является выбранное в качестве прототипа устройство для цикловой синхронизации [2] , содержащее опознаватель циклового синхросигнала, анализатор совпадения сигнала, блок выделения тактовой частоты, распределитель импульсов, триггер, регистр, элементы И и ИЛИ, соединенные определенным образом.

Недостатками прототипа являются увеличение времени вхождения в синхронизм при реализация в нем последовательного поиска синхронизации, а применение входного регистра, особенно при синхронизации цифровых передач с рассредоточенной синхрокомбинацией, увеличивает его аппаратные затраты, т.к. разрядность регистра равна длине, в позициях, цикла передачи, длина которой может достигать нескольких тысяч позиций.

Технической задачей изобретения является уменьшение времени поиска синхронизма при распределенной синхрокомбинации с одновременным сокращением аппаратных средств.

Указанная задача решается тем, что в устройство для цикловой синхронизации, содержащее дешифратор, генераторное оборудование (ГО), состоящее из счетчика позиций, счетчика циклов, генератора импульсов, дешифратора нулевого состояния счетчиков (НСС), фазирующее устройство (ФУ), первый инвертор, причем тактовые сигналы поступают со входа устройства для цикловой синхронизации (ЦС ) через первый инвертор на тактовые входы счетчика позиций и счетчика циклов ГО, адресные выходы 1,...,m и 1,...,n ГО соединены с адресными выходами устройства для ЦС, выход ФУ соединен с соответствующим выходом устройства для ЦС, согласно изобретению введены оперативное запоминающее устройство (ОЗУ), распределитель, триггер, второй, третий и четвертый инверторы, первый и второй элементы И, элемент ИЛИ, регистр запоминания (РЗ), задающее устройство (ЗУ), причем адресные входы 1,...,m ОЗУ соединены с адресными выходами 1,...,m ГО, вход выбора ОЗУ соединен с земляной шиной, выход третьего инвертора соединен со входом разрешения чтения ОЗУ и со входом управления РЗ, вход разрешения записи ОЗУ соединен с выходом второго инвертора, входы/выходы 1,2,...,N-1,N ОЗУ соединены со входами/выходами 1,2,..., N-1,N РЗ, тактовый вход распределителя соединен с выходом первого инвертора, а вход распределителя соединен с выходом генератора импульсов ГО, первый выход распределителя соединен с тактовым входом триггера, информационный вход триггера соединен с шиной питания, второй выход распределителя соединен с входом РЗ, третий выход распределителя соединен с входом установки в ноль триггера и тактовым входом ФУ, четвертый выход распределителя соединен со входом второго инвертора, выход дешифратора НСС ГО соединен со вторым входом первого элемента И, выходы 0p, 1p, 2p,...,(N-1)p, Np РЗ соединены с соответствующими входами дешифратора, выход дешифратора соединен с третьим входом первого элемента И и со вторым входом второго элемента И, первый вход первого элемента И соединен с выходом четвертого инвертора, выход первого элемента И соединен со вторым входом элемента ИЛИ, выход второго элемента И соединен с первым входом элемента ИЛИ и входом установки в ноль ГО, выход элемента ИЛИ соединен с входом синхрокомбинации ФУ, выход нулевого состояния ФУ соединен со входом четвертого инвертора и первым входом второго элемента И, выходы 1,...,k ЗУ соединены со входами 1,...,k ФУ, выходы 1,...,р ЗУ соединены со входами 1,...,р ФУ, информационный вход устройства для ЦС соединен с информационным входом РЗ.

Известные устройства для цикловой синхронизации цифровых потоков с рассредоточенной синхрокомбинацией, как правило, осуществляют поисковый (последовательный) метод обнаружения первой синхрокомбинации. Осуществление ими оптимального (параллельного) метода требует больших аппаратных затрат, т. к. используется входной регистр, разрядность которого определяется количеством позиций соответствующего цифрового потока и может достигать нескольких тысяч.

Основное время при поиске синхронизации определяется временем нахождения первой синхрокомбинации.

Максимальное время нахождения первой рассредоточенной синхрокомбинации при последовательном поиске равно

Максимальное время нахождения первой рассредоточенной синхрокомбинации при параллельном поиске равно

где Т- время обнаружения первой синхрокомбинации, в с;

N - отрезок между соседними элементами синхрокомбинации, в позициях;

n - длина синхрокомбинации, в позициях;

F - скорость цифровой передачи, в бит/с.

Из приведенных соотношений видно, что среднее время нахождения неискаженной рассредоточенной синхрокомбинации при параллельном поиске в N/2 раз меньше, чем при последовательном.

Предлагаемое устройство для цикловой синхронизации позволяет осуществлять параллельный поиск рассредоточенной синхрокомбинации без увеличения аппаратных затрат.

Новизна технического решения заключается в применении в заявленном устройстве новых схемных элементов: оперативного запоминающего устройства ОЗУ, распределителя, регистра запоминания РЗ, задающего устройства ЗУ, триггера, второго, третьего и четвертого инверторов, первого и второго элементов И, элемента ИЛИ.

Таким образом, изобретение соответствует критерию "новизна".

Анализ известных технических решений в исследуемой и смежных областях позволяет сделать вывод о том, что введенные функциональные узлы известны. Однако введение их в устройство для цикловой синхронизации с указанными связями придает этому устройству новые свойства. Введенные функциональные узлы взаимодействуют таким образом, что позволяют осуществить параллельный поиск рассредоточенной синхрокомбинации без увеличения аппаратных затрат и, следовательно, уменьшить время вхождения в синхронизм при одновременном сокращении оборудования.

Таким образом, изобретение соответствует критерию "изобретательский уровень", т.к. оно для специалиста явным образом не следует из уровня техники.

Изобретение может быть использовано в цифровых системах передач с временным уплотнением.

Таким образом, изобретение соответствует критерию "промышленная применимость".

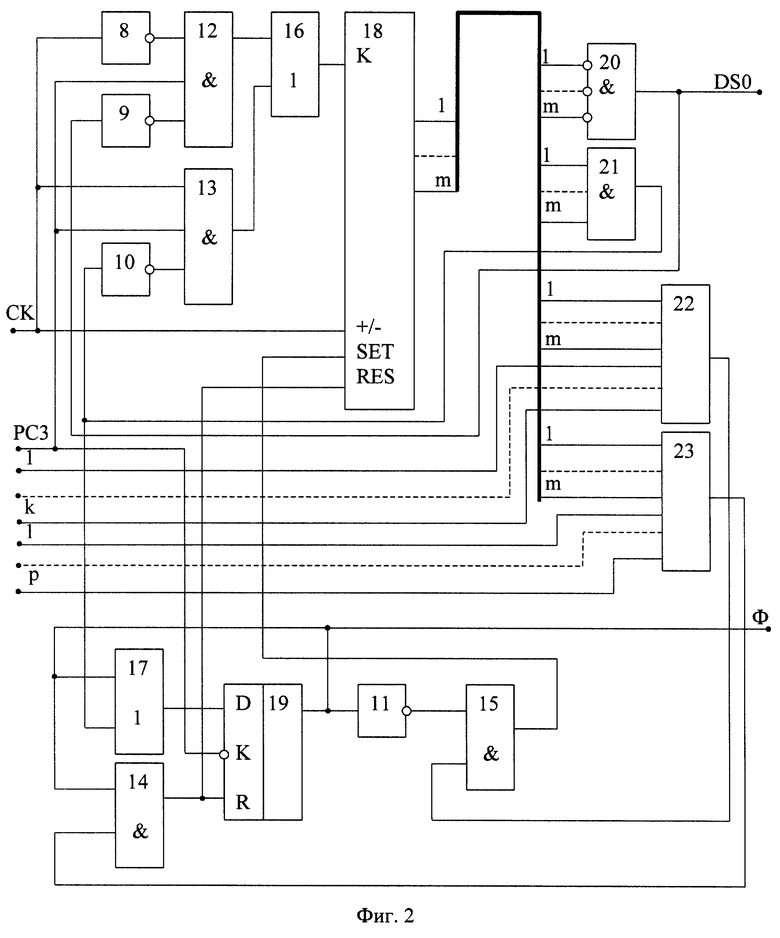

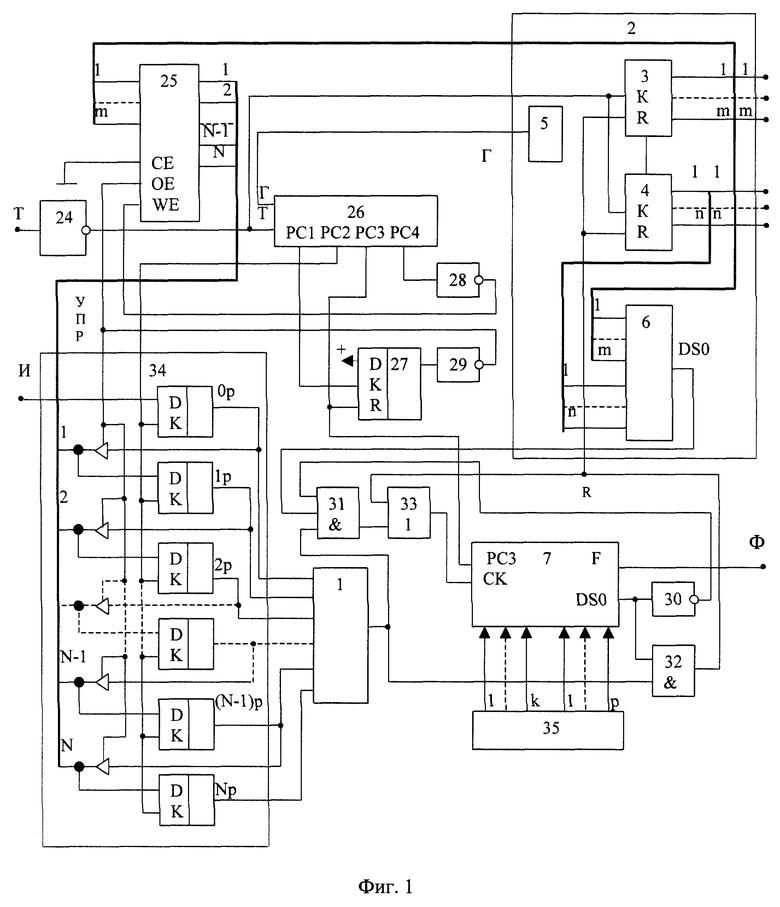

На фиг.1 изображена структурная электрическая схема устройства для цикловой синхронизации, на фиг. 2 изображена структурная электрическая схема фазирующего устройства.

Устройство для цикловой синхронизации (фиг.1) содержит дешифратор 1, генераторное оборудование (ГО) 2, состоящее из счетчика позиций 3, счетчика циклов 4, генератора импульсов 5, дешифратора нулевого состояния счетчиков (НСС) 6, фазирующее устройство (ФУ) 7, первый инвертор 8, оперативное запоминающее устройство (ОЗУ) 9, распределитель 10, триггер 11, второй 12, третий 13 и четвертый 14 инверторы, первый 15 и второй 16 элементы И, элемент ИЛИ 17, регистр запоминания (РЗ) 18, задающее устройство (ЗУ) 19, причем тактовые сигналы поступают со входа устройства для цикловой синхронизации (ЦС) через первый инвертор 8 на тактовые входы счетчика позиций 3 и счетчика циклов 4 ГО 2, адресные выходы 1,...,m и 1,...,n ГО 2 соединены с адресными выходами устройства для ЦС, выход ФУ 7 соединен с соответствующим выходом устройства для ЦС, адресные входы 1,...,m ОЗУ 9 соединены с адресными выходами 1,...,m ГО 2, вход выбора ОЗУ 9 соединен с земляной шиной, выход третьего инвертора 13 соединен со входом разрешения чтения ОЗУ 9 и со входом управления РЗ 18, вход разрешения записи ОЗУ 9 соединен с выходом второго инвертора 12, входы/выходы 1,2,...,N-1,N ОЗУ 9 соединены со входами/выходами 1,2, ...,N-1,N P3 18, тактовый вход распределителя 10 соединен с выходом первого инвертора 8, а вход распределителя 10 соединен с выходом генератора импульсов 5 ГО 2, первый выход распределителя 10 соединен с тактовым входом триггера 11, информационный вход триггера 11 соединен с шиной питания, второй выход распределителя 10 соединен с входом P3 18, третий выход распределителя 10 соединен с входом установки в ноль триггера 11 и тактовым входом ФУ 7, четвертый выход распределителя 10 соединен со входом второго инвертора 12, выход дешифратора НСС 6 ГО 2 соединен со вторым входом первого элемента И 15, выходы 0p, 1p, 2p,...,(N-1)p, Np P3 18 соединены с соответствующими входами дешифратора 1, выход дешифратора 1 соединен с третьим входом первого элемента И 15 и со вторым входом второго элемента И 16, первый вход первого элемента И 15 соединен с выходом четвертого инвертора 14, выход первого элемента И 15 соединен со вторым входом элемента ИЛИ 17, выход второго элемента И 16 соединен с первым входом элемента ИЛИ 17 и входом установки в ноль ГО 2, выход элемента ИЛИ 17 соединен с входом синхрокомбинации ФУ 7, выход нулевого состояния ФУ 7 соединен со входом четвертого инвертора 14 и первым входом второго элемента И 16, выходы 1,...,k ЗУ 19 соединены со входами 1,...,k ФУ 7, выходы 1,...,р ЗУ 19 соединены со входами 1, . . .,р ФУ 7, информационный вход устройства для ЦС соединен с информационным входом P3 18.

Фазирующее устройство (фиг.2) содержит инверторы 20, 21, 22, 23, элементы И24, И25, И26 и И27, элементы ИЛИ28 и ИЛИ29, реверсивный счетчик 30, триггер 31, дешифратор нулевого состояния реверсивного счетчика 32, дешифратор максимального состояния реверсивного счетчика 33, элементы совпадения 34 и 35, причем вход синхрокомбинации (вход СК) ФУ 7 соединен со входом инвертора 20, первым входом элемента И25 и входом прямого или обратного счета +/- реверсивного счетчика 30, тактовый вход (вход РСЗ) ФУ 7 соединен с тактовым входом (вход К) триггера 31, вторым входом элемента И24 и вторым входом элемента И25, входы 1,...,k ФУ 7 соединены с соответствующими входами элемента совпадения 34, входы 1, . . .,р ФУ 7 соединены с соответствующими входами элемента совпадения 35, выход инвертора 20 соединен с первым входом элемента И24, выход инвертора 21 соединен с третьим входом элемента И24, выход которого соединен с первым входом элемента ИЛИ 28, выход инвертора 22 соединен с третьим входом элемента И25, выход которого соединен со вторым входом элемента ИЛИ28, выход которого соединен с тактовым входом (вход К) реверсивного счетчика 30, выходы разрядов 1,...,m которого соединены с соответствующими входами дешифратора нулевого состояния реверсивного счетчика 32, дешифратора максимального состояния реверсивного счетчика 33 и элементов совпадения 34 и 35, выход дешифратора нулевого состояния реверсивного счетчика 32 соединен со входом инвертора 21 и выходом нулевого состояния (выход DCO) ФУ 7, выход дешифратора максимального состояния реверсивного счетчика 33 соединен со входом инвертора 22 и вторым входом элемента ИЛИ 29, выход которого соединен с информационным входом (вход D) триггера 31, выход элемента совпадения 34 соединен со вторым входом элемента И27, выход которого соединен со входом установки в максимальное состояние (вход SET) реверсивного счетчика 30, выход элемента совпадения 35 соединен со вторым входом элемента И26, выход которого соединен со входом установки в ноль R триггера 31 и входом установки в ноль RES реверсивного счетчика 30, выход триггера 31 соединен со входом инвертора 23, первым входом элемента И26, первым входом элемента ИЛИ29 и выходом ФУ 7, выход инвертора 23 соединен с первым входом элемента И27.

Устройство для цикловой синхронизации работает следующим образом.

По тактовым сигналам, поступающим со входа (вход Т) устройства для цикловой синхронизации через первый инвертор 8 на тактовые входы (входы К) счетчика позиций 3 и счетчика циклов 4 ГО 2, счетчик позиций 3 осуществляет подсчет количества позиций между соседними элементами рассредоточенной синхрокомбинации цифрового потока, а счетчик циклов 4 подсчитывает количество циклов, число которых определяется количеством элементов синхрокомбинации. Выходы 1,...,m разрядов счетчика позиций 3 ГО 2 поступают на адресные входы 1,...,m ОЗУ 9. Работа ОЗУ 9 разрешена нулевым потенциалом на его входе выбора СЕ, соединенного с земляной шиной. При наличии на входе разрешения чтения ОЕ ОЗУ 9 сигнала Лог. "1", а на входе разрешения записи WE сигнала Лог. "0" осуществляется запись информации, поступившей на 1,2...N-1,N входы/выходы ОЗУ 9, в ячейки выбранного адреса. При наличии на входе разрешения записи WE сигнала Лог. "1", а на входе разрешения чтения ОЕ сигнала Лог. "0" осуществляется считывание информации из соответствующих ячеек выбранного адреса ОЗУ 9 на его 1,2...N-1,N входы/выходы. Тактовые сигналы, кроме этого, поступают на тактовый вход Т распределителя 10, на другой вход Г которого поступают сигналы с генератора импульсов 5 ГО 2. Частота генератора импульсов 5 подобрана таким образом, чтобы за период тактового сигнала, поступившего на тактовый вход Т распределителя 10, в последнем сформировалась распределенная во времени последовательность сигналов РС1, РС2, РС3, РС4. Информационные сигналы с выхода И устройства для ЦС поступают на информационный вход D триггера 0р РЗ 18. Сигналом, поступившим с первого выхода (выход РС1) распределителя 10 на тактовый вход (вход К) триггера 11, последний устанавливается в единичное состояние, т.к. информационный вход (вход D) этого триггера соединен с шиной питания. Сигнал с выхода триггера 11 через третий инвертор 13 поступает на вход управления (вход УПР) РЗ 18. При этом выходы вентилей РЗ 18 переводятся в третье состояние, блокируя прохождение через них сигналов с триггеров 0р, 1p, 2p,..., (N-1 )р, Np. Также сигналом, поступающим с выхода инвертора 13 на вход разрешения чтения ОЕ ОЗУ 9, последнее осуществляет считывание информации, записанной в него по соответствующему адресу во время предыдущего цикла работы. Сигналом, поступившим с второго выхода (выход РС2) распределителя 10 на вход РЗ 18, в его триггере Ор запоминается текущий информационный сигнал, поступающий с информационного входа (вход И) устройства для ЦС, а в триггерах 1p, 2p,..., (N-1)p, Np P3 18 - ранее запомненные в ОЗУ 9 и считанные по соответствующему адресу сигналы на входах/выходах 1,2, . . . ,N-1,N ОЗУ 9. Сигналом, поступившим с третьего выхода (выход РС3) распределителя 10 на вход установки в ноль (вход R) триггера 11, последний устанавливается в нулевое состояние. При этом прекращается сигнал разрешения считывания, поступающий на вход разрешения чтения ОЕ ОЗУ 9, и разрешается работа управляемых вентилей P3 18. Причем запомненная информация с выходов 0р, 1p, 2p,..., (N-1)p триггеров P3 18 через открытые управляемые вентили и его входы/выходы 1,2,...,N-1,N поступает соответственно на входы/выходы 1,2, . ..,N-1,N ОЗУ 9. Сигналом, поступившим с четвертого выхода (выход РС4) распределителя 10 через второй инвертор 12 на вход разрешения записи WE ОЗУ 9, в последнем осуществляется запись пришедшей на его входы/выходы информации. Таким образом, работу ОЗУ 9 во взаимодействии с работой P3 18 можно представить как работу М сдвигающих регистров, где М равно количеству позиций между элементами рассредоточенной синхрокомбинации, а разрядность каждого регистра равна числу N, где N - длина синхрокомбинации, в позициях. При этом в каждом адресе ОЗУ 9 запомнены значения предыдущих N-1 разрядов P3 18, а текущее значение запоминается в триггере 0р P3 18. С выходов P3 18 текущий информационный сигнал и сигналы, считанные из ОЗУ 9, поступают на входы дешифратора 1. До появления первого положительного отклика на выходе дешифратора 1 сигналом лог. "1" с выхода нулевого состояния DCO ФУ 7, поступающим на первый вход второго элемента И 16, разрешается работа последнего, а через четвертый инвертор 14 запрещается работа первого элемента И 15. Первый сигнал положительного отклика о дешифрации синхрокомбинации, поступивший через открытый второй элемент И 16 на вход установки в ноль (вход R) счетчика позиций 3 и счетчика циклов 4 ГО 2, последние устанавливает в нулевое состояние. Этот же сигнал, поступивший через элемент ИЛИ 17 на вход синхрокомбинации СК ФУ 7, увеличивает состояние его реверсивного счетчика 30 на единицу. После чего сигналом Лог. "0" на выходе нулевого состояния DCO ФУ 7 второй элемент И 16 закрывается, а через четвертый инвертор 14 открывается по первому входу первый элемент И 15. После этого проверка правильности дешифрации синхрокомбинации производится при нулевых состояниях счетчика позиций 3 и счетчика циклов 4 ГО 2. Теперь при нулевых состояниях счетчиков 3 и 4 ГО 2 по выходному сигналу дешифратора нулевого состояния счетчиков НСС 6 ГО 2 разрешается по второму входу работа первого элемента И 15. При этом сигнал положительного или отрицательного отклика с выхода дешифратора 1 через первый элемент И 15 и элемент ИЛИ 17 поступает на вход синхрокомбинации СК ФУ 7 и по сигналу, поступающему с третьего выхода РС3 распределителя 10 на соответствующий вход ФУ 7, последнее изменяет свое состояние.

Фазируюшее устройство работает следующим образом.

При отсутствии на входе синхрокомбинации СК ФУ 7 первого сигнала положительного отклика дешифрации синхрокомбинации реверсивный счетчик 30 находится в нулевом состоянии. При этом сигналом с выхода дешифратора нулевого состояния реверсивного счетчика 32 ФУ 7 через инвертор 21 запрещается работа элемента И 24 и тем самым запрещается прохождение тактового сигнала со входа РС3 фазирующего устройства 7 на тактовый вход К реверсивного счетчика 30 и последний удерживается в нулевом состоянии. При поступлении на вход синхрокомбинации СК ФУ 7 первого сигнала положительного отклика дешифрации синхрокомбинации реверсивный счетчик 30 по его входу прямого или обратного счета +/- устанавливается в режим положительного счета и по тактовому сигналу РС3 ФУ 7, поступающему через открытый по первому и третьему входу элемент И 25 и элемент ИЛИ 28 на тактовый вход К реверсивного счетчика 30, последний увеличивает свое состояние на единицу. После этого сигналом Лог. "0" дешифратора нулевого состояния реверсивного счетчика 32 через инвертор 21 разрешается при сигнале отрицательного отклика на входе синхрокомбинации СК прохождение тактового сигнала со входа РС3 через открытый элемент И 24 и элемент ИЛИ 28 на тактовый вход К реверсивного счетчика 30. Таким образом, при сигнале положительного отклика на входе СК ФУ 7 реверсивный счетчик 30 увеличивает свое состояние на единицу, а при сигнале отрицательного отклика на входе СК - уменьшает свое состояние на единицу. Когда разность количества сигналов положительного и отрицательного откликов при дешифрации синхрокомбинации достигнет заданного значения критерия входа в синхронизм, сигнал с выхода элемента совпадения 34 через открытый элемент И 27 поступает на вход установки в максимальное состояние SET реверсивного счетчика 30 и при поступлении со входа синхрокомбинации СК ФУ 7 следующего сигнала положительного отклика по сигналу с тактового входа РС3 реверсивный счетчик 30 устанавливается в максимальное состояние, а триггер 31 отрицательным фронтом тактового сигнала со входа РС3 ФУ 7 устанавливается в единичное состояние. Таким образом, устройство для ЦС переходит в режим синхронизма и его удержания, который индицируется сигналом наличия синхронизации Ф, поступающим с выхода триггера 31 на выход ФУ 7 и далее на выход устройства для ЦС. Единичным выходным сигналом с триггера 31 через инвертор 23 запрещается работа элемента И 27 и разрешается работа элемента И 26. Сигналы выбранного критерия входа в синхронизм поступают с входов 1,...,k ФУ 7 на входы 1,...,k элемента совпадения 34. Сигналы выбранного критерия выхода из синхронизма поступают с входов 1,...,р ФУ 7 на входы 1,...,р элемента совпадения 35.

Когда разность количества сигналов отрицательного и положительного откликов при дешифрации синхрокомбинации достигнет заданного значения критерия выхода из синхронизма, сигнал с выхода элемента совпадения 35 через открытый элемент И 26 поступает на вход установки в ноль RES реверсивного счетчика 30 и вход установки в ноль R триггера 31, устанавливая их в начальное состояние. Устройство вновь переходит в режим поиска синхронизма, как было описано выше.

Для технической реализации устройства для цикловой синхронизации использованы статическое оперативное запоминающее устройство (ОЗУ) импортного производства типа 7С199 (фирма CYPRESS SEMICONDICTOR) и программируемая пользователем логическая интегральная схема (ППЛИС) импортного производства типа ХС 3195(фирма XILINX).

Предлагаемое изобретение позволяет уменьшить время поиска синхронизма при распределенной синхрокомбинации с одновременным сокращением аппаратных средств.

Источники информации

1. Патент РФ 2136111, кл. Н 04 L 7/08.

2. Патент РФ 2019046, кл. Н 04 L 7/08.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2286020C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2002 |

|

RU2224378C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1998 |

|

RU2136111C1 |

| УСТРОЙСТВО ДЛЯ ДЕМУЛЬТИПЛЕКСИРОВАНИЯ | 2005 |

|

RU2296431C2 |

| Устройство для цикловой синхронизации | 2014 |

|

RU2612620C2 |

Изобретение относится к технике цифровой связи, а именно к устройствам для цикловой синхронизации цифровых систем передачи информации с временным уплотнением. Устройство цикловой синхронизации содержит дешифратор синхрокомбинации, генераторное оборудование, состоящее из счетчика позиции, счетчика циклов, генератора импульсов и дешифратора нулевого состояния счетчиков, фазирующее устройство и первый инвертор, а также вновь введенные оперативное запоминающее устройство, распределитель, триггер, второй, третий и четвертый инверторы, первый и второй элементы И, элемент ИЛИ, регистр запоминания и задающее устройство. Устройство для цикловой синхронизации позволяет уменьшить время поиска синхронизма при распределенной синхрокомбинации с одновременным сокращением аппаратурных средств, в чем и состоит технический результат, достигаемый при реализации данного изобретения. 2 ил.

Устройство для цикловой синхронизации, содержащее дешифратор, генераторное оборудование (ГО), состоящее из счетчика позиций, счетчика циклов, генератора импульсов, дешифратора нулевого состояния счетчиков (НСС), фазирующее устройство (ФУ), первый инвертор, причем тактовые сигналы поступают со входа устройства для цикловой синхронизации (ЦС) через первый инвертор на тактовые входы счетчика позиций и счетчика циклов ГО, адресные выходы 1, . . . , m и 1, . . . , n ГО соединены с адресными выходами устройства для ЦС, выход ФУ соединен с соответствующим выходом устройства для ЦС, отличающееся тем, что введены оперативное запоминающее устройство (ОЗУ), распределитель, триггер, второй, третий и четвертый инверторы, первый и второй элементы И, элемент ИЛИ, регистр запоминания (РЗ), задающее устройство (ЗУ), причем адресные входы 1, . . . , m ОЗУ соединены с адресными выходами 1, . . . , m ГО, вход выбора ОЗУ соединен с земляной шиной, выход третьего инвертора соединен со входом разрешения чтения ОЗУ и со входом управления РЗ, вход разрешения записи ОЗУ соединен с выходом второго инвертора, входы/выходы 1,2, . . . , N-1, N ОЗУ соединены со входами/выходами 1,2, . . . , N-1, N РЗ, тактовый вход распределителя соединен с выходом первого инвертора, а вход распределителя соединен с выходом генератора импульсов ГО, первый выход распределителя соединен с тактовым входом триггера, информационный вход триггера соединен с шиной питания, второй выход распределителя соединен с входом РЗ, третий выход распределителя соединен с входом установки в ноль триггера и тактовым входом ФУ, четвертый выход распределителя соединен со входом второго инвертого, выход дешифратора НСС ГО соединен со вторым входом первого элемента И, выходы 0р, 1p, 2p, . . . , (N-1)p, Np PЗ соединены с соответствующими входами дешифратора, выход дешифратора соединен с третьим входом первого элемента И и со вторым входом второго элемента И, первый вход первого элемента И соединен с выходом четвертого инвертора, выход первого элемента И соединен со вторым входом элемента ИЛИ, выход второго элемента И соединен с первым входом элемента ИЛИ и входом установки в ноль ГО, выход элемента ИЛИ соединен с входом синхрокомбинации ФУ, выход нулевого состояния ФУ соединен со входом четвертого инвертора и первым входом второго элемента И, выходы 1, . . . , k ЗУ соединены со входами 1, . . . , k ФУ, выходы 1, . . . , р ЗУ соединены со входами 1, . . . , р ФУ, информационный вход устройства для ЦС соединен с информационным входом PЗ.

| SU 1608811 A1, 23.11.1990 | |||

| US 54128614 A, 27.06.1995 | |||

| DE 3412736 С1, 17.10.1995 | |||

| US 4727558, 23.02.1988 | |||

| ПРОЕКТОР ДЛЯ КОНТРОЛЯ РАЗМЕРОВ ДЕТАЛЕЙ | 0 |

|

SU258621A1 |

Авторы

Даты

2002-09-27—Публикация

2000-03-07—Подача