Изобретение относится к телемеханике, цифровым вычислительным машинам, системам контроля и управления.

Известны кольцевые дешифраторы, содержащие кольцевой регистр сдвига, схему считывания и элемент разрешения исполнения. В этих устройствах могут появляться следуюш.ие одиночные характерные неисправности:

нет считывания информации с любой одной ячейки регистра;

неисправность на информационном входе одной любой ячейки;

неисправность на одном из двух выходов одной любой ячейки;

один из двух управляющих сигналов не поступет на одну любую ячейку.

Цель изобретения - увеличение числа обнаруживаемых ошибок. Достигается она тем, что предлагаемый кольцевой дешифратор дополнительно содержит триггериую ячейку, два сумматора по модулю 2, три элемента «ИЛИ и один элемент «И, причем счетный вход триггера соединен со входной клеммой устройства, а выходы подключены к первым входам сумматоров по модулю 2, вторые входы которых через элементы «ИЛИ соединены с выходами разрядов кольцевого регистра, а выходы сумматоров подключены через двухвходовый элемент «ИЛИ к первому входу элемента «И, второй вход которого

соединен с выходом элемента разрешения исполнения.

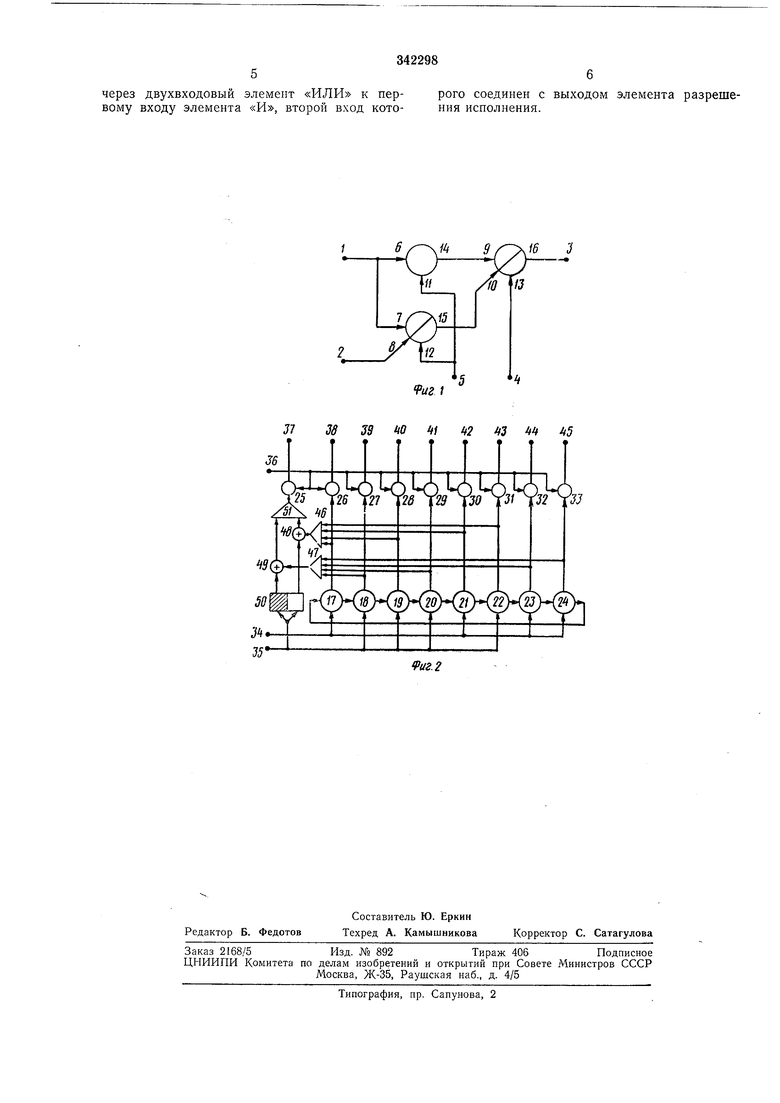

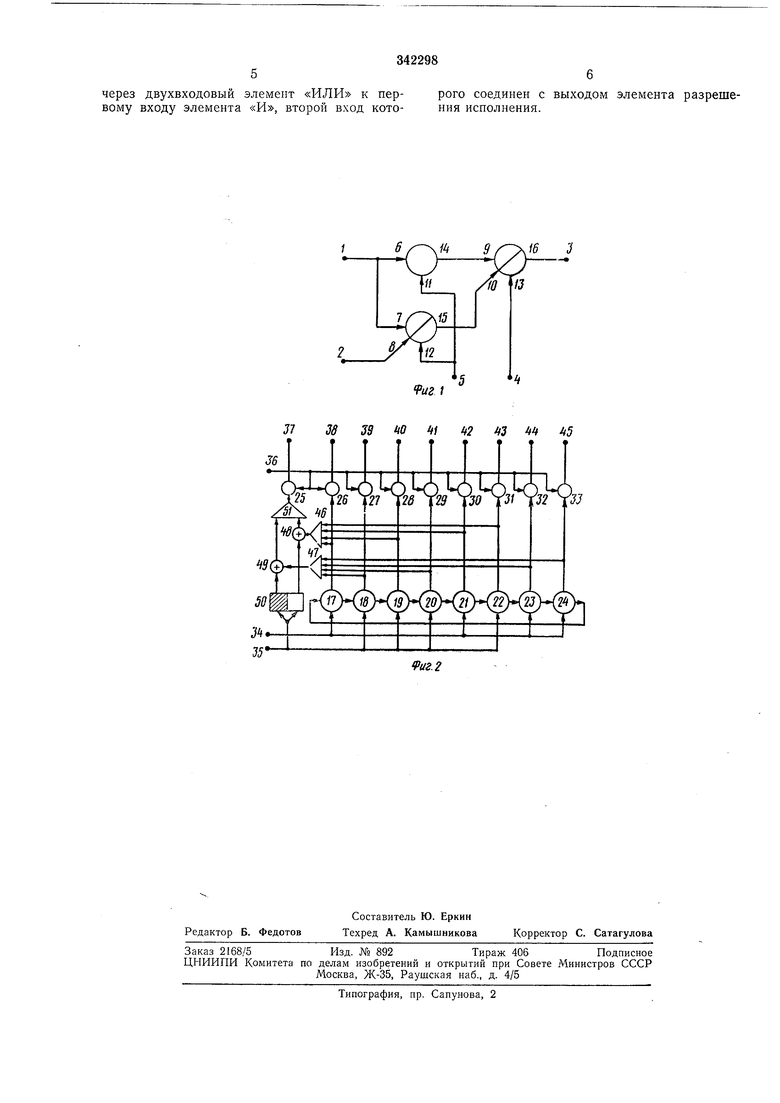

На фиг. 1 показана схема ферритовой ячейки кольцевого дещифратора безизбыточного трехэлементного двоичного кода; на фиг. 2 - схема кольцевого дешифратора на осноце кольца безизбыточного трехэлементного кода - Q1I 10100-.

Представленная ячейка (фиг. 1) совмещает в себе функции элемента единичной задержки и логической схемы «И, т. е. Yi-Xl/ Vi:Ii, где Y принимает значение «I или «О в зависимости от состояния ячейки, X принимает

значение «1 или «О в зависимости от того, поступает управляющий сигнал на данную ячейку или нет, i - номер ячейки, - тактовое время. Ячейка на фиг. 1 работает цо двухфазной схеме. Это значит, что за один

такт последовательно поступают два синхроимпульса. Ячейка содержит информационный вход 1, на который поступает сигнал с предыдущего разряда регистра; управляющий вход 2, на который поступают декодируемьте символы X; выход 3, входы и 5, на которые поступают синхроимпульсы первой и второй фаз; входные (записывающие) обмотки 6-10 ферритов, считьшающие обмотки //-13, выходные обмотки 14-16. Характерными неис. 34229 3 ей обрывы обмоток. Нетрудно заметить, что из-за обрыва одной из обмоток 7, 10, 12, 15 функция исправной ячейки , р rt-i меняется на функцию повторения У г ,s а из-за обрыва одной из обмоток 6, 8, 9, 11, 13, 14, 16 - на функцию константу У г 0. В соответствии с этим все характерные неисправности можно условно подразделить на неисправности первого вида и неисправностиЮ второго вида. Неисправности первого вида могут привести к ошибкам дешифрирования, заключающимся в появлении двух или нескольких возбужденных выходных шин по окончании декодирования. При этом одна15 шина истинная, а остальные - ошибочные, такие, что кодовое расстояние между дешифрируемой кодовой комбинацией и комбинациями, соответствуюпдими ошибочно возбужденным шинам, d. Неисправности второго20 вида могут привести к ошибкам дешифрирования, заключаюшимся в отсутствии возбужденных выходных шин. Предлагаемый кольцевой дешифратор автоматически вырабатывает сигнал ошибки при25 появлении ошибок, вызванных любой одиночной характерной неисправностью. В качестве примера на фиг. 2 показана схема кольцевого дешифратора, построенного на основе кольца безизбыточного кода30 -01110100-. Устройство содержит восьмиразрядный кольцевой регистр, построенный из ячеек 17-24; схему считывания, состояШую из двухвходовых схем совпадения 25- 55; шину нулевого сигнального признака 34,35 шину единичного сигнального признака 35, шину разрешения исполнения 36, шину сигнала ошибки 37, выходные шины 38-45. Выходы ячеек регистра разбиты на две групиы. Первую группу составляют выходы ячеек40 17, 19, 21, 22, соответствуюшие входным последовательностям с четным числом единиц. вторую - выходы ячеек 8, 20, 23, 24, соответствующие входным последовательностям с .нечетным числом единиц. Сигналы с выходов45 первой труппы подаются на собирательную схему «ИЛИ 46/ а с выходов второй группы - на схему «ИЛИ 47. Выходы схем «ИЛИ 46 и 47 подключены ко входам сумматоров 48 и 49 по модулю 2. Вторые входы50 этих сумматоров соединены с выходами триггера 50, счетный вход которого соединен с шиной единичного сигнального признака 55. С выходов сумматоров 48 и 49 сигналы поступают на схему «ИЛИ 51, с выхода кото-55 рой сигнал через схему совпадения 25 по сигналу с шины разрешения исполнения 36 поступает на шину сигнала ошибки 57. Рассмотрим работу устройства на примере дешифрирования последовательности 001.60 При исправной работе устройства после 4 .рирования третьего символа «1 - ячейка 18 и при очередном синхроимпульсе и сигнале на шине разрешения исполнения 56 возбуждается выходная шина 59. Пусть в ячейке 17 произошел обрыв одной из обмоток 7, 10, 12, 15. При дешифрировании первого символа «О в состоянии «1 оказываются ячейки 17, 21, 23, 24, после дешифрирования второго символа «О - ячейки 17 и 24 и после дешифрирования третьего символа «1 ячейки 17 и 18, сигналы с которых иосле очередного синхроимпульса попадают на схемы «ИЛИ 46 и 47 соответственно, Триггер 50 неред началом дешифрирования всегда устанавливается в одно и то же состояние, а именно, его выход, соединенный с сумматором 48, единичный, а выход, соединеиный с сумматором 49, нулевой. В исходное состояние триггер 50 может устанавливаться тем же импульсом, который устанавливает в исходное состояние все разряды регистра, После дешифрирования последовательности с нечетным числом единиц триггер 50 опрокидывается, а после дешифрирования последовательности с четным числом единиц остается в исходном состоянии. При дешифрировании последовательности 001 на сумматор 49 поступает сигнал с триггера 50 и со схемы «ИЛИ 47, а на сумматор 48 - только со схемы «ИЛИ 46, а на схему «ИЛИ 51 поступает «1 с сумматора 48. Сигнал с выхода схемы «ИЛИ 51 по сигналу с шины разрешения исполнения 36 проходит через схему совпадения 25 в шину сигнала ошибки 57. Подобным образом обнаруживается любой обрыв. При отсутствии возбужденных выходных шин сигнал поступает только с триггера 50 на один из сумматоров 48 или 49. Через схему «ИЛИ 51 и схему совпадения 25 этот сигнал проходит в шину сигнала ошибки 57. При нормальной работе дешифратора по окончании дешифрирования входной последовательности на один из сумматоров 48 или 49 обязательно поступают два сигнала. На шине сигнала ошибки 57 сигнал в этом случае не появляется, Предмет изобретения Кольцевой дешифратор, содержащий кольценой регистр сдвига, схему считывания и элемент разрешения исполнения, отличающийся тем, что, с целью увеличения числа обнаруживаемых ошибок, вызванных неисправностями в элементах дешифратора, последний дополнительно содержит триггерную ячейку, два сумматора по модулю 2, три элемента «ИЛИ и один элемент «И, причем счетный вход триггера соединен со входной клеммой устройства, .а выходы подключены 5 через двухвходовый элемент «ИЛИ к первому входу элемента «И, второй вход кото6рого соединен с выходом элемента разрешения исполнения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| ДЕШИФРАТОР ЦИКЛИЧЕСКОГО КОДА | 1970 |

|

SU267184A1 |

| КОЛЬЦЕВОЙ ДЕШИФРАТОР | 1973 |

|

SU390666A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для программирования блоков постоянной памяти | 1987 |

|

SU1453447A1 |

| Тренажер для выработки координарно-моторного рефлекса | 1983 |

|

SU1168199A1 |

| Устройство для обнаружения и исправления ошибок | 1985 |

|

SU1368995A1 |

| Декодер | 1978 |

|

SU896614A1 |

| Запоминающее устройство с обнаружением и коррекцией ошибок | 1983 |

|

SU1138836A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1987 |

|

SU1539783A1 |

J7 38 39 tiO 1 2 П -V 5

аг 1

9иг.2

Даты

1972-01-01—Публикация