1

Изобретение относится к вычислительной техни се и может быть использовано для хранения и переработки дискретной информации.

Известно логическое полноточное запоминающее устройство, содерл ащее накопитель с числовыми линейками с элементами памяти на двух сердечниках с прямоугольной петлей гистеризиса (ППГ), прошитых адресными шинами записи и считывания и разрядными шинами записи, считывания и чтения, регистр слова, регистр признака обращения, адресные вентили, адресные формирователи. Операции выполняются между операндами, один из которых находится в регистре слова, а другой - в выбранной числовой линейке. В таком запоминающем устройстве (ЗУ) можно функционально выполнить полный набор логических операций с получением результата в числовой линейке или на шинах чтения. Однако известное устройство характеризуется сложностью схемы и большим количеством дополнительного оборудования особенно в разрядных цепях, что снижает его информационную надежность и повышает стоимость.

Цель изобретения - упрощение и повышение надежности работы устройства.

Для этого предлагаемое устройство содержит генераторы тока запрета, тока прямоугольной формы и тока пилообразной

формы, управляющие вентили, разрядные элементы задержки и вентили единичного и нулевого входов, причем выходы генераторов тока занрета, тока прямоугольной формы и тока пилообразной формы через управляющие вентили соединены с соответствующими входами разрядных вентилей, выходы усилителей чтения соединены со входами разрядных элементов задержки, выходы которых через вентили нулевого и единичного входов подключены к соответствующим входам триггеров регистра слова.

В таком ЗУ выполняются 14 логических операций, включая операции равнозначности и неравнозначности. За один обращения к ЗУ реализуются три опе(рации. Результат одной операции получается в выбранной числовой линейке, результат второй операции снимается с выходов усилителей чтения i первом такте обращен 1я и результат третьей операции снимается с выходов усилителей чтения во втором такте обращения к ЗУ.

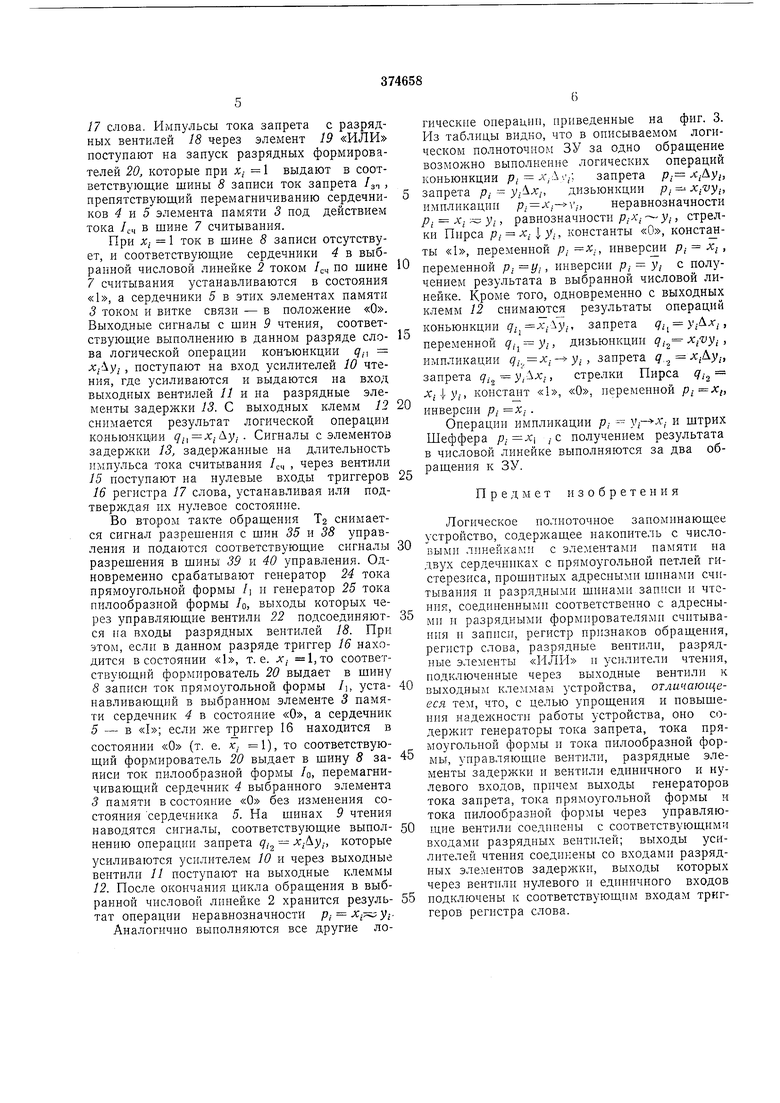

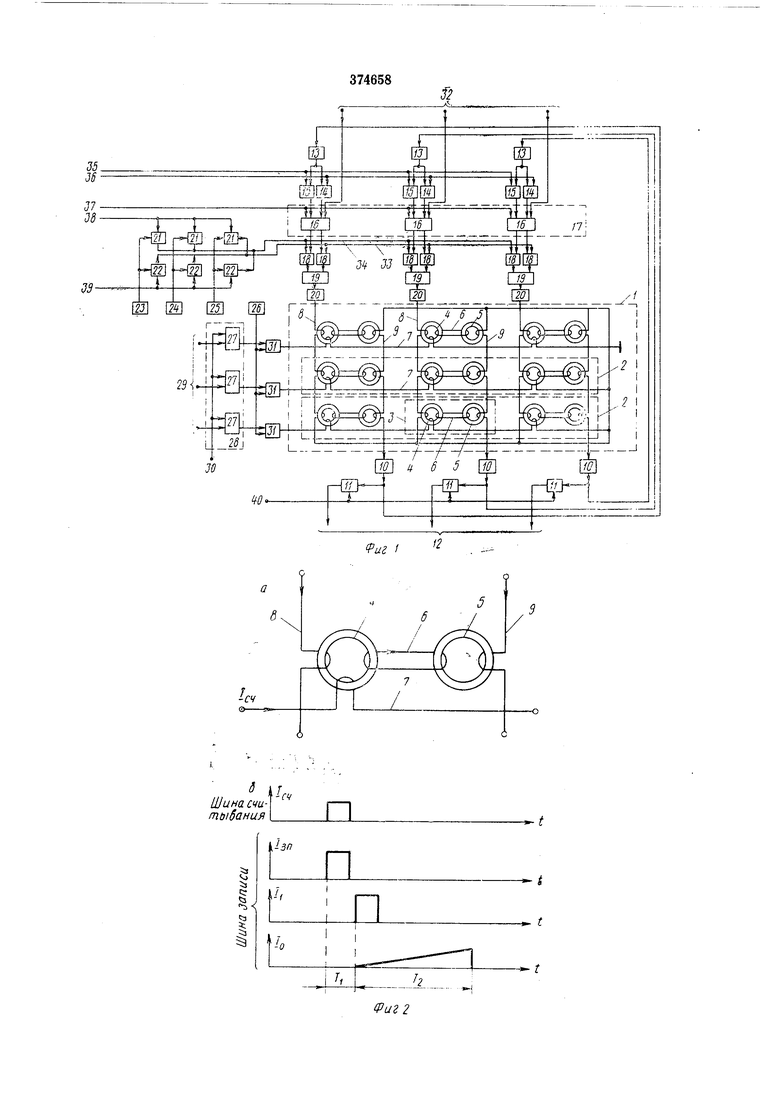

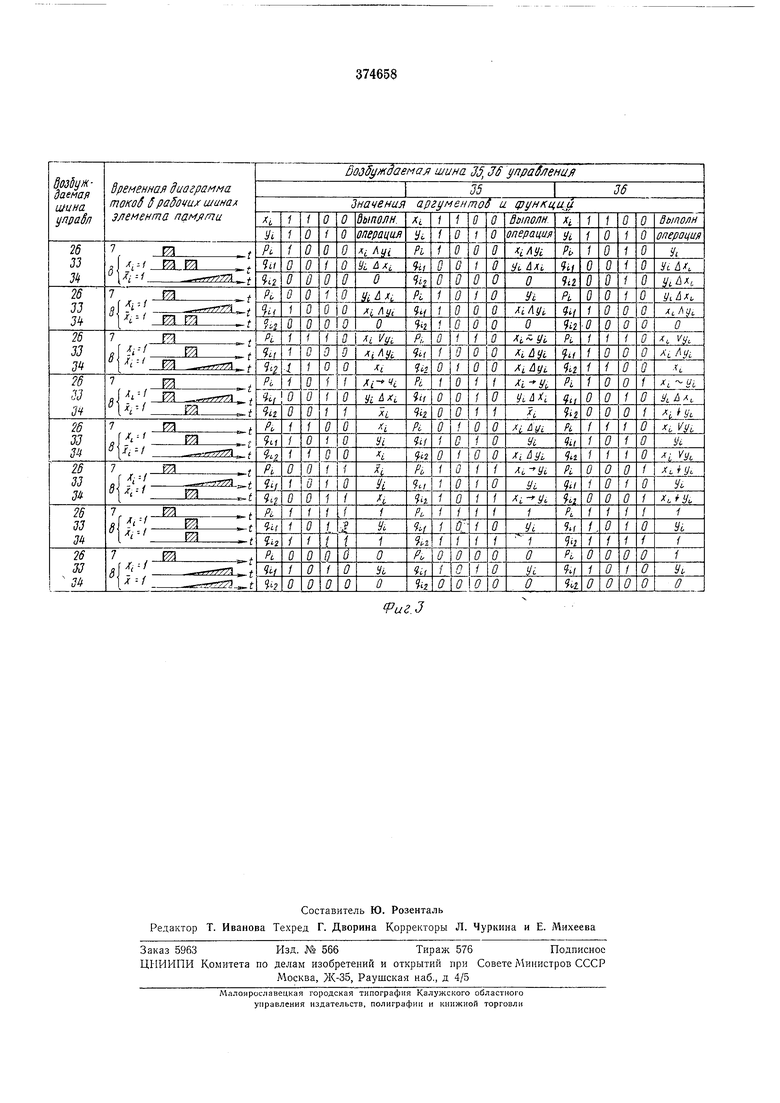

На фиг. 1 изображена принципиальная схема предлагаемого устройства; на фиг. 2 - схема отдельного элемента памяти и временная диаграмма его работы; на фиг. 3 - таблица реализуемых функций.

Устройство содержит накопитель / с числовыми линейками 2 на элементах памяти 3, в состав которых входят сердечники 4 и 5,

объединенные витками 6 связи, адресные шины 7 считывания, разря71,ные шины 8 записи, разрядные шины 9 чтения, усилители 10 чтения, выходные вектнли 11, выходные клеммы 12, разрядные элементы 13 задержки, вентили 14 единичного входа, вентили 15 нулевого входа, триггеры 16 регистра 17 слова, разрядные вентили 18, разрядные элементы 19 «ИЛИ, разрядные формирователи 20 тока записи, управляюш,ие вентили 21 обратного кода, управляюш,ие вентили 22 нрямого кода, генератор 23 тока заирета, генератор 24 тока прямоугольной формы, генератор 25 тока пилообразной формы, формирователь 26 тока считывания, триггеры 27 регистра 28 признаков обращения с входными шинами 29, шину 30 сброса, адресные формирователи 31, входные клеммы 32, шину 53 разрешення прямого кода, шнну 34 .разрешения обратного кода, шины 35-40 управления.

Устройство работает следующим образом.

В исходиом состоянии все сердечники 4 установлены в состяние «О, а в сердечниках 5 хранится код операнда у. Второй операнд наход; тсяв регистре слова. На фиг. 26 приведена временная диаграмма работы рассматриваемой ферритовой пары. Обращение к ЗУ осуществляется в два такта. В первом такте Т импульс тока I, в соответствии с адресом поступает в шину 7 считывания одной из числовых линеек 2 и одновременно в шину записи. При определенных логических операциях в зависимости от кода операнда X поступает импульс тока запрета /зп , препятствующий перемагпнчиванию сердечников ферритовой пары. При отсутствии тока запрета /зп сердечник 4 иеремагиичивается в состояние «1, а сердечник 5 током в витке 6 связи устанавливается в положение «О, в шинах 9 чтения наводятся выходные сигналы. Во нтором такте Т, в шину 8 записи в зависимости от кода слова х и выполняемой логической операции поступает импульс тока прямоугольной 1 или пилообразной /о формы. При этом, если в первом такте в сердечник-# была запнсаиа «1 (ток запрета /з. отсутствовал), а во втором такте в шине 8 записи протекает ток /ьто ссрдечиик4перемагничивается в состояние «О, а сердечиик 5 - в состояние «1. Если во втором такте в шине 8 записи протекает ток /о, то сердечник 4 медленно перемагнпчпвается в «О, а состоя 1ие сердечиика 5 ие меняется.

В исходном состоянии в регистре 17 слова хранится входное слово к (л ,,..., х-, ,..., х), а в каждой числовой линейке 2 накопителя 1 некоторое слово у (у,,..., У;,..., У), где х,- - i-ый разряд входного слова, хранящийся в i-OM триггере/5 регистра 7 слова; у,- i-ый разряд слова, хранящийся в сердечнике .З числовой линейки 2; п - количество разрядов.

Триггер 27 регистра 28 признаков обращения той числовой линейки 2, в которой должна выполняться логическая операция, устаиовлен в состояние «1.

Логические операции над словами являются поразрядными операциями, поэтому достаточно рассмотреть реализацию логической операции в одном разрядном сечении. Через K - 1 обозначают разрядные сигналы возбуждения, получаемые с прямых выходов триггеров 16, находящихся в состоянии «1, а через х - разрядные сигналы возбуждения, получаемые с инверсных выходов триггеров 16, находящихся в состоя}1ии «О. Через Pi обозначают переключательную функцию, реализуемую в г-ом заноминающем сердечнике 5 выбранной числовой линейки 2, значение которой соответствует состояниям этого сердечника после воздействия на памяти 3 разрядного сигнала л;,- или Xi, при условии, что исходное состояние сердечника 5 соответствовало значению у/-. Через л обозначают переключательную функцию, реализуемую г-ным запоминающим сердечником 5 выбранной числовой линейки 2, значение которой получается на щине 9 чтения, пронизывающей данный сердечник 5, в первом такте обращения TI в момент воздействия на этот сердечник с исходным состоян1-1ем У/ или У,- разрядного сигнала Х; или Xi, причем единичному зиачеиию «Уд соответствует наличие импульсиого сигнала на шине 9 чтения, а нулевому - его отсутствие. Через (7/2 обозначают переключательную функцию, реализуемую i-ным сердечником 5 выбранной числовой линейки 2, значение которой получается па шине 9 чтения, пронизывающей даииый сердечник 5 во втором такте обращения Т2 в момент воздействия на элемеит 5 памяти тока прямоугольной /1 или пилообразиой формы /о.

Выиолиенпе некоторой логической операции иад входным словом и словом, хранящимся в выбранной числовой линейке, происходит при подаче сигналов }азрещения иа И1ПНЫ 35-40 управления (см. фиг. 3). Логические операцпи и времеииые диаграммы токсп в рабочих элемента 3 прп выполиенпп этих операций приведены иа фиг. 3.

В качестве примера рассмотрим выполнение логическпх операцпи неравнозначност Р,- X; г- У; ; коиъюнкцпп qi, x,Ay,. и запрета ,. Прп выполкенип дапных операцпи в первом такте обращения TI в шины 35, 38 и 40 управления выдаются сигналы разрешения. Одновременно запускается формирователь 26 тока считывании и генератор 23 тока запрета. Прп этом возбуждается адресный формирователь 31 той числовой лпнейки 2, триггер 27 иризнака обращения которой находится в состоянии «1, а импульс с генератора 23 через управляющий вентиль 2J по шине 34 разрешения обратного кода поступает па входы разрядных вентилей 18, вторые входы которых подключены к нулевым выходным шинам триггеров 16 регистра

17 слова. Импульсы тока запрета с разрядных вентилей 18 через элемент 19 «ИЛИ поступают на запуск разрядных формирователей 20, которые при х - выдают в соответствующие шины 8 записи ток запрета /зп , препятствующий перемагничиванию сердечкиков 4 и 5 элемента памяти сЗ под действием тока /сч в щине 7 считывания.

При KI 1 ток в шине 8 записи отсутствует, и соответствующие сердечники 4 в выбранной числовой линейке 2 током /сч по шине

7считывания устанавливаются в состояния «1, а сердечники 5 в этих элементах памяти 3 током и внтке связи - в положение «О. Выходные сигналы с шин 9 чтения, соответствующие выполнению в данном разряде елова логической операции конъюнкции q/, - , поступают на вход усилителей 10 чтения, где усиливаются и выдаются на вход выходных вентилей 11 и на разрядные элементы задержки 13. С выходных клемм 12 снимается результат логической операции КОНЪЮНКЦИИ 9;i X;Ay;. С И гн а Л ы С э Л ементоз задержки 13, задержанные на длительность импульса тока считывания /сч , через вентили

15поступают на нулевые входы триггеров

16регистра 17 слова, устанавливая или подтверждая их нулевое состояние.

Во втором такте обращения Т2 снимается сигнал разрешения с шин 35 и 38 управления и подаются соответствующие сигналы разрешения в щины 39 и 40 управления. Одновременно срабатывают генератор 24 тока прямоугольной формы /1 и генератор 25 тока пилообразной формы /о, выходы которых через управляющие вентили 22 подсоединяются на входы разрядных вентилей 18. При этом, если в данном разряде триггер 16 находится в состоянии «1, т.е. Jc/ 1,то соответствующий формирователь 20 выдает в щину

8записи ток прямоугольной формы /ь устаиавливающий в выбранном элементе 3 памяти сердечник 4 в состояиие «О, а сердечник

5 - в если же триггер 16 находится в состоянии «О (т. е. х,. 1), то соответствующий формирователь 20 выдает в шину 8 записи ток пилообразной формы /о, перемагничивающий сердечник 4 выбранного элемента 3 памяти в состояиие «О без изменения состояния сердечника 5. На щинах 9 чтения наводятся сигналы, соответствующие выполнению операции запрета q/ - ,-Ду;, которые усиливаются усилителем 10 и через выходные вентили 11 поступают на выходные клеммы 12. После окончания цикла обращения в выбранной числовой линейке 2 хранится результат операции неравнозначности p/ .. Аналогично выполняются все другие логические операции, приведенные на фиг. 3. Из таблицы видно, что в описываемом логическом полноточном ЗУ за одно обращение возможно выполнение логических операций конъюнкции Pi ,--,; запрета р,. -,-Лу;, запрета р,- у,, дизьюнкции Р,- - , импликации /5,. ,,., неравнозначности А; - у,, равнозначности р,-А-,. - у,., стрелки Пирса Pi - Xfly, константы «О, константы «1, переменной Р; л;,-, инверст р, переменной р-.-у-,, инверсии р,- у,- с получением результата в выбранной числовой линейке. Кроме того, одновременно с выходных клемм 12 снимаются результаты операций конъюнкции 9/1 ); запрета ; у.Д.х., переменной , дизьюнкции (, . импликации 9/., .V; запрета 9,.д:;Ауг, запрета (,X;, стрелки Пирса /з- .Х;|у;, констант «1, «О, переменной ,

инверсии PI х.; .

Операции импликации р; У,,, и штрих Шеффера ,. с получением результата в числовой линейке выполняются за два обращения к ЗУ.

Предмет изобретения

Логическое полноточное запоминающее устройство, содер кащее накопитель с числовыми линейками с элементами памяти на двух сердечниках с прямоугольной петлей гистерезиса, прошитных адресными шинами считывания и разрядными шинами записи и чтения, соединенными соответственно с адресными н разрядными формирователями считывания и записи, регистр признаков обращения, регистр слова, разрядные вентили, разрядные элементы «ИЛИ и усилители чтения, подключенные через выходные вентили к выходным клеммам устройства, отличающееся тем, что, с целью упрощения и повышения надежности работы устройства, оно содержит генераторы тока запрета, тока прямоугольной формы и тока пилообразной формы, управляющие вентили, разрядные элементы задержки и вентили единичного и нулевого входов, причем выходы генераторов тока запрета, тока прямоугольной формы и тока пилообразной формы через управляющие вентили соединены с соответствующими входами разрядных вентилей; выходы усилителей чтения соединены со входами разрядных элементов задержки, выходы которых через вентили нулевого и единичного входов подключены к соответствующим входам триггеров регистра слова.

рф

НЙ-Н

| название | год | авторы | номер документа |

|---|---|---|---|

| Логическое полноточное запоминающее устройство | 1974 |

|

SU470861A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Логическое запоминающее устройство | 1979 |

|

SU801101A2 |

| Логическое запоминающее устройство | 1980 |

|

SU886052A2 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

S if

-rv

Шина считыбания

с;

f3

иг.З

Даты

1973-01-01—Публикация