Известно многоканальное запоминающее устройство, содержащее матрицу с числовыми линейками на тороидальных сердечниках с прямоугольной петлей гистерезиса, пронизанных линейными и разрядными шинами записи и считывания, подключенными к соответствующим формирователям, а также выходными линейными шинами, соединенными через цепи управления с линейными триггерами.

Предложенное устройство отличается от известных тем, что каждая числовая линейка содержит линейную шину установки, пронизывающую сердечники данной числовой линейки в соответствии с коэффициентом пересчета, формирователь, подключенный к линейной шине установки, и вентиль, вход которого соединен с выходом линейного триггера, а выход связан с формирователем.

Это позволяет установить коэффициент пересчета по каждому каналу.

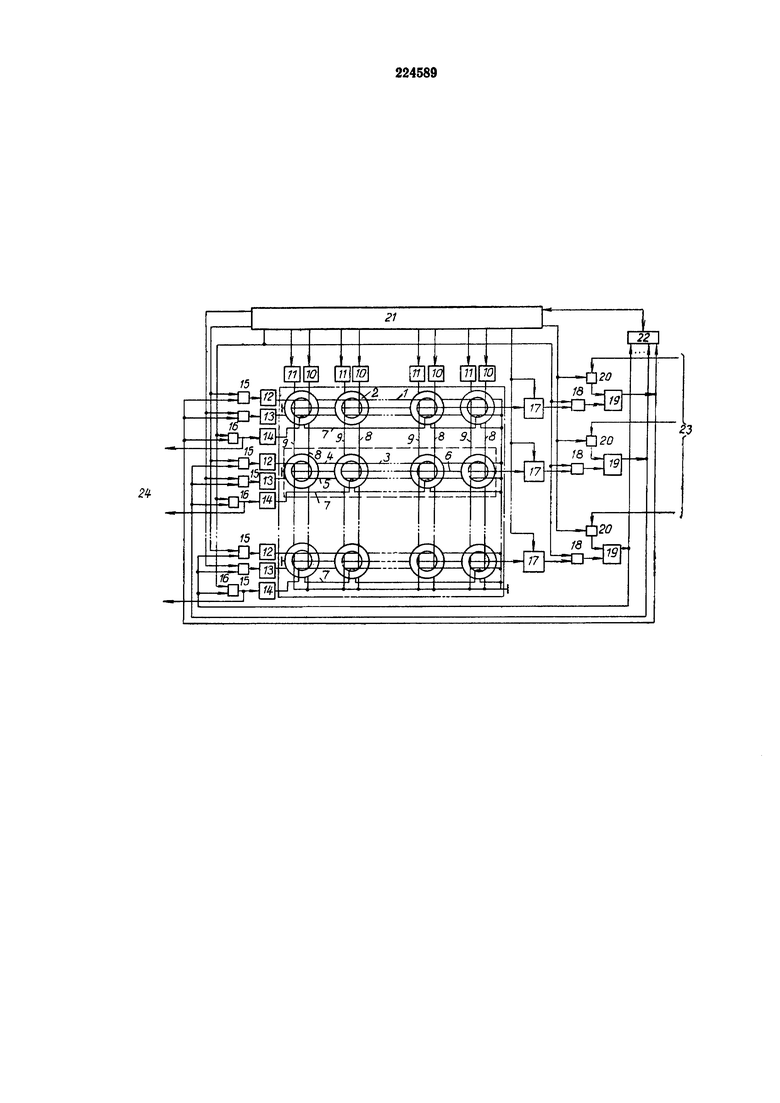

На чертеже представлена схема предлагаемого устройства.

Матрица 1 построена по принципу выбора сердечника 2 при совпадении разрядного и линейного полутоков. Каждая числовая линейка 3 матрицы 1 имеет линейную шину записи 4, линейную шину считывания 5 и линейную шину чтения 6, пронизывающие все сердечники 2 данной числовой линейки, а также линейную шину установки 7, пронизывающую лишь определенные сердечники 2 этой числовой линейки. Все сердечники 2 одноименных разрядов числовых линеек 3 пронизаны разрядной шиной записи 8 и разрядной шиной считывания 9, к которым подключены соответственно выходы разрядного формирователя полутока записи 10 и разрядного формирователя полутока считывания 11. Каждая числовая линейка снабжена линейным формирователем полутока записи 12, линейным формирователем полутока считывания 13, линейным формирователем полутока установки 14, линейными вентилями 15, вентилем установки 16, усилителем чтения 17, вход которого соединен с линейной шиной чтения 6, а выход - со входом схемы «ИЛИ» 18. Выход схемы «ИЛИ» 18 соединен со входом сброса линейного триггера 19, вход установки которого соединен с выходом соответствующего входного вентиля 20.

Блок управления 21 обеспечивает Последовательное срабатывание разрядных формирователей полутоков записи 10 и считывания 11 и вырабатывает управляющие сигналы, поступающие на другие блоки устройства. Блок управления 21 состоит из задающего генератора и распределительного устройства. Схема «ИЛИ-НЕ» 22 предназначена для фиксации момента окончания суммирования по всем каналам поступивших единичных приращений и имеет число входов, равное числу каналов. Входы схемы «ИЛИ-НЕ» 22 соединены с единичными выходами линейных триггеров 19, а ее выход соединен со входом блока управления 21.

Импульсы, подлежащие перерасчету, поступают на входы 23, а сигналы, вырабатываемые устройством после поступления на входы 23 числовых линеек определенного числа импульсов по каждому сигналу, поступают на выходы 24.

В исходном состоянии каждой числовой линейки записано некоторое число Nj, такое, что коэффициент пересчета данной числовой линейки

Kj=2n-Nj,

где j - номер числовой линейки,

n - число разрядов числовой линейки.

Числа Nj устанавливаются перед началом работы путем одновременного возбуждения всех линейных формирователей 14. Каждая линейная шина установки 7 пронизывает все сердечники данной числовой линейки в соответствии с двоичным кодом Nj.

В режиме пересчета устройство работает следующим образом.

В такте приема информации подлежащие пересчету импульсы каналов поступают на входы 23 и через входные вентили 20 устанавливают соответствующие линейные триггеры 19 в единичное состояние.

Затем в числовых линейках 3 матрицы 1 начинается одновременное суммирование поступивших единичных приращений последовательно по разрядам, начиная с младшего. Суммирование в каком-либо разряде числовых линеек осуществляется в два такта: в первом такте вписываются «1» в сердечники этого разряда соответствующих числовых линеек и выявляются переносы в следующий разряд. При отсутствии переноса суммирование в данной ячейке закончено. При наличии дальнейшего переноса во втором такте в те же сердечники записываются «0», а выявленные сигналы используются для прибавления единицы к следующему разряду.

В первом такте сигналы с находящихся в единичном состоянии линейных триггеров 19 через линейные вентили 15 возбуждают соответствующие линейные формирователи полутоков записи 12. Одновременно сигнал с блока управления 21 вызывает срабатывание разрядного формирователя полутока записи 10 младшего разряда. При этом осуществляется запись единиц в данной разрядной позиции соответствующих числовых линеек и происходит выявление сигналов переноса в следующий старший разряд.

Если первоначально сердечник младшего разряда некоторой числовой линейки находился в состоянии «0», то при подаче линейного и разрядного полутоков записи этот сердечник перемагничивается и на соответствующей линейной шине чтения 6 появляется сигнал, который проходит через усилитель чтения 17, схему «ИЛИ» 18 и сбрасывает триггер 19. Переход триггера 19 в нулевое состояние указывает на отсутствие дальнейшего переноса и на окончание суммирования поступившего по данному каналу единичного приращения. Однако, если сердечник младшего разряда некоторой числовой линейки находился в состоянии «1», то под воздействием линейного и разрядного полутоков записи его состояние не изменится. Следовательно, на линейной шине чтения 6 данной числовой линейки сигнал не появляется, и соответствующий линейный триггер 19 остается в единичном состоянии, указывая на наличие переноса в следующий старший разряд. Таким образом, по окончании первого такта в единичном состоянии остаются только линейные триггеры 19 тех числовых линеек, в которых имеются переносы в следующий разряд. Для получения правильного значения разрядных сумм в младший разряд этих числовых линеек необходимо записать «0». С этой целью во втором такте возбуждаются линейные формирователи полутоков считывания 13 тех числовых линеек, у которых линейные триггеры 19 остались в единичном состоянии. Одновременно сигналом из блока управления 21 возбуждается разрядный формирователь полутока считывания 11 младшего разряда. Под действием линейных и разрядного полутоков считывания происходит переключение в состояние «0» сердечников младшего разряда соответствующих числовых линеек. Возникающие при этом на линейных шинах чтения 6 сигналы на входы линейных триггеров 19 не проходят, так как усилители чтения 17 в этом такте не стробируются.

Далее описанный двухтактный цикл работы устройства повторяется для каждой из последующих разрядных позиций до окончания процесса суммирования ло всем каналам. В этот момент все линейные триггеры 19 будут находиться в нулевом состоянии, а схема «ИЛИ-НЕ» 22 вырабатывает сигнал, поступающий на блок управления 21, который подготавливает устройство к приему новой информации.

После поступления по определенному каналу Kj - 1 единичных приращений все сердечники соответствующей числовой линейки будут находиться в состоянии «1». Суммирование следующего единичного приращения сопровождается возникновением последовательного переноса через все разряды числовой линейки и последовательным переходом всех сердечников этой числовой линейки в нулевое состояние, а при этом линейный триггер 19 остается в состоянии «1».

Поступающий в следующем такте из блока управления 21 сигнал проходит через вентиль установки 16 числовой линейки на выход 24 и одновременно возбуждает линейный формирователь полутока установки 14, в результате чего в числовую линейку записывается код Nj

Одновременно через схему «ИЛИ» 18 происходит сброс линейного триггера 19 данной линейки. Аналогично происходит пересчет и по остальным каналам.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПАМЯТИ и РЕГИСТРАЦИИ | 1968 |

|

SU217463A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU428450A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Ассоциативное логическое запоминающее устройство | 1972 |

|

SU485501A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| Логическое запоминающее устройство | 1976 |

|

SU650103A1 |

Многоканальное запоминающее устройство, содержащее матрицу с числовыми линейками на тороидальных сердечниках с прямоугольной петлей гистерезиса, пронизанных линейными и разрядными шинами записи и считывания, подключенными к соответствующим формирователям, а также выходными линейными шинами, соединенными через цепи управления с линейными триггерами, отличающееся тем, что, с целью установки коэффициента пересчета по каждому каналу, каждая числовая линейка содержит линейную шину установки, пронизывающую сердечники данной числовой линейки в соответствии с коэффициентом пересчета, формирователь, подключенный к линейной шине установки, и вентиль, вход которого соединен с выходом линейного триггера, а выход связан с формирователем.

Авторы

Даты

1968-11-27—Публикация

1967-07-13—Подача