Изобретение относится к вычис.тптелыкм технике.

Известны элементы памяти на полупроводниковых приборах с S-образиыми характеристиками. Они характеризуются высокими требования.ми к стаб11Л1)ИОСти иапряження включения приборов.

Целью изобретеппя является новышеиие быстродействия, упрои еппе схемы управления памятью, сииженне требований к стабильности иараметров приборов. Отличительной особенностью иредлагаемого элемента памяти является то, что анод и /;-база управляющего тирпстора соединены со входными иифор.маинопиыми , аиод заиомпнающего тпрпстора соединен с выходной информационной шипо1|, которая через резистор подключена к источнику иитаиия, а катоды обоих тиристоров соединены с адресной шиной.

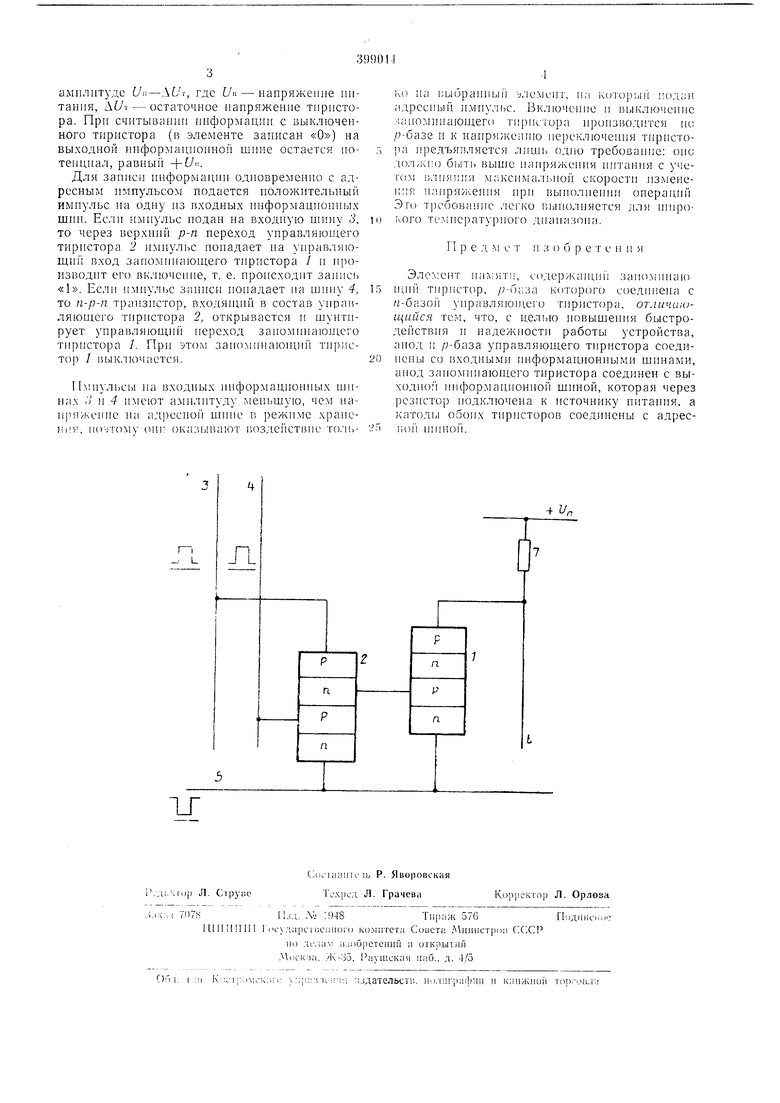

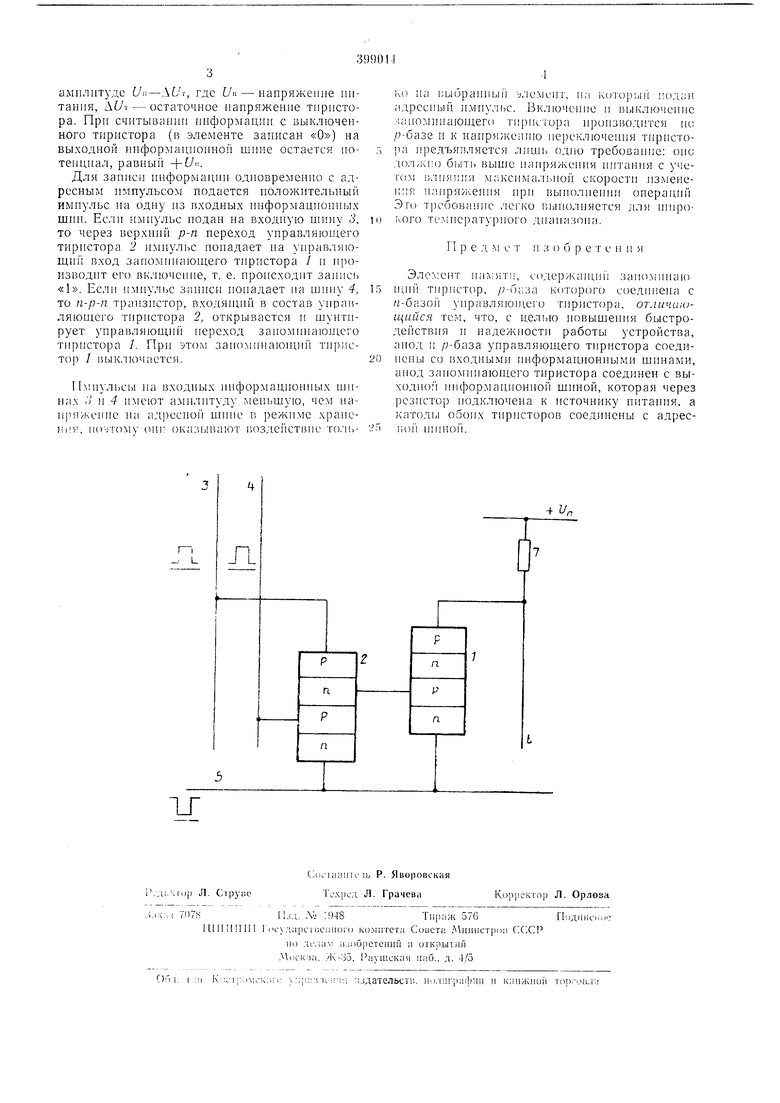

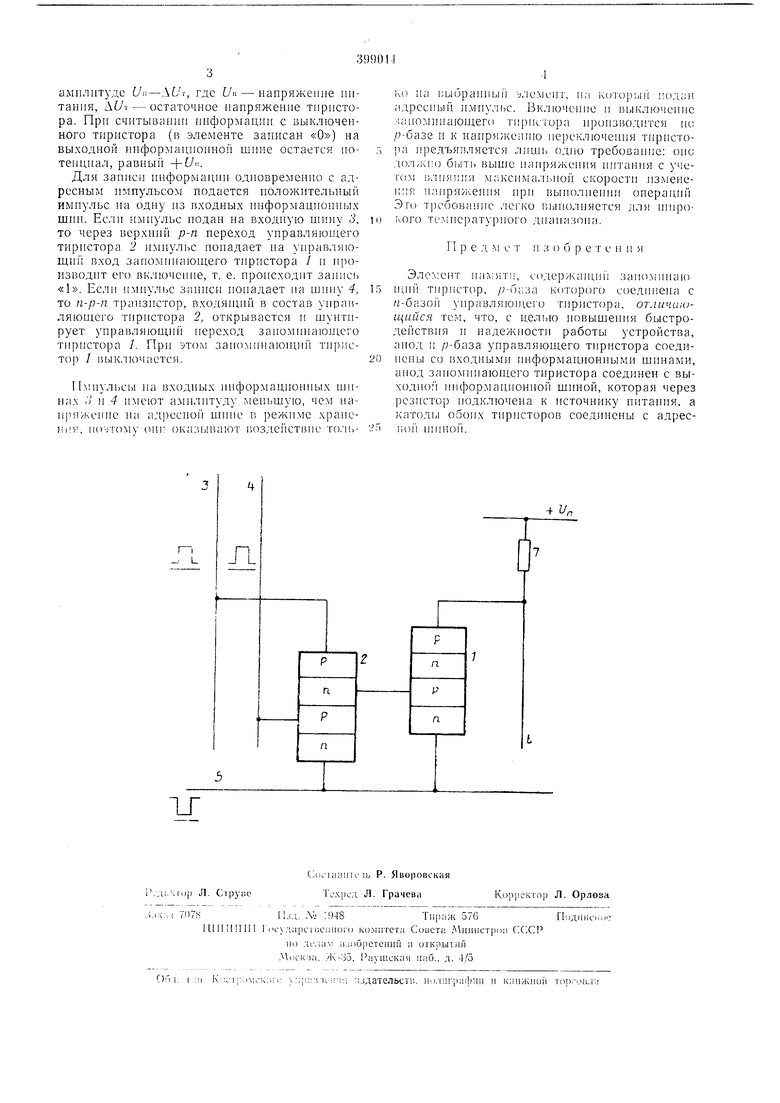

Схема э.темента намяти приведена па чертеЛ С.

Элемент намятп состонт из заиоминаюп1его Тиристора / и управляюн1его тирпстора 2. Лпод п /7-база управляющего тпристора 2 соедппепы соответственно со входнымп ипфор.мапиоиными шина.ми ,) и 4. Катоды заиомиnaioiuero и уиравляюи|,его тиристоров соединены с адресной шшюй 5, а анод запоминающего TiipiicTopa соединен с выходной информаnnoHnoii 6. Выходная информацноиная

шнна 6 через резистор / соединена с источником иитаиия.

Резистор 7 яв.тяется обии1м для всех элементов памяти данного разряда, что позволяет выполнять ячейку .малых геометрических размеров п достигать высокоГ стеиени интеграции.

Устройство работает следующим образом. В режпме хранеппя информации адресная шипа 5 и.меет высокий потепциал, равный наиряженню источника иитания ( + L:i); на нее подаются восстанавлнваюнию имиульсы отрицательной иоляриости. При иоступлепии импульсов адресная шппа 5 подключается к «минусу псточннка питаппя. Входные информационные П1ПИЫ о и -/ имеют низкий уровень сигнала.

Частоту следования восстанавливающих имнульсов шггания выбирают такой, чтобы пауза между имиульсами была меньше времени выключеиия заиоминаюитего тиристора. Благодаря нмиул ;спому пптапню средняя мопщость, потребляемая элементом намятн, оказывается очег.ь мало).

Сч 1ты15;1ппе ннформацпп нропзводнтся в паузах лгежду восстанавлнвающимн импульса.ми питания иодачей на адресную шину 5 имнульсов. аналогичиых восстанавливающим. Если заиомииаюнип тиристор включен (в элементе памяти заиисана «1), то ири подаче адресного имиульса н.а выходной шине 6 появляется отр1И1ательны| 1 импульс, равньп по

3

амплитуде U i-AL-r, где L/K - напряжение питания, Af/T - остаточное напряжение тиристора. Прн считыв;и11И ппформации с выключепного тиристора (в элементе записан «О) на выходной информационной шине остается иотеициал, равный заинсп информации одновременно с адресным импульсом подается положительный импульс на одну нз входных ннформационных шин. Если импульс подан на входную шину 3, то через верхннй р-п переход управлякяцего тирпстора 2 имиульс иоиадает па управляющий вход запоминающего тиристора / п производит его включение, т. е. пропсходнт 3ainic «1. Если импульс з;1ииси иоиадает иа шину 4, то п-р-п транзистор, входянии в состав yHpaisляющего тнрнстора 2, открывается и шунтирует уиравляющнй переход заиомппающего тнристора /. При этом заиомпнающий тиристор / выключается.

Имиульсы иа входных информациоипых шинах .) и 4 имеют а.милитуду меньшую, чем наиря/ че11ие иа адресной шние в )ежнме хранеио-ггпму они оказывают воздействие только иа |;ыораипы11 -лчемсчгг, иа кот(.).)1,1Г1 и(.д;:н адресный импульс. Включите и выключепне лапомниаюидего тиристора производится ио /7-базе и к напря;кеиию иереключеиия тиристора иредъяпляется лишь одно требование: оио дол.кпо бьп|) вьш1е ианряжеиня иитанпя с учетом 1;, няи1;я мг;кснма. скорости изменег.пя иагфяжеиия ири выиолненнп операцнй Эго требование легко выиолияется для ншрокого темноратуриого днаиазона.

П р е д м е т и з о б р е т е н п я

Элслхчгг иал:ят, с()дер 1 аии1и заио.мпиаю 1иий тиристор, /7-база которого соедниеиа с /г-базо уиравляющего тиристора, отличающийся тем, что, с целью новышенпя быстродействия и надежностн работы устройства, анод и /;-база управляющего тнрнстора соединены со входными и фopмaциoнными шинами, анод заноминаюнгего тиристора соединен с выходно; информапиониой шиной, которая через )езисто1) нодключена к псточннку ннтання, а катоды обонх тнрнсторов соединены с адресной П1НИОЙ.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВПТБ Ш14Ш11Жу1 | 1973 |

|

SU409292A1 |

| КОЛЬЦЕВОЙ РАСПРЕДЕЛИТЕЛЬ | 1971 |

|

SU303731A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1969 |

|

SU236873A1 |

| Импульсный модулятор | 1974 |

|

SU539377A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК ИМПУЛЬСОВ | 1956 |

|

SU424324A1 |

| Генератор импульсов для электроэрозионной обработки | 1977 |

|

SU634897A1 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| СИГНАЛИЗАТОР НАПРЯЖЕНИЯ | 1970 |

|

SU275222A1 |

| Способ управления тиристорным преобразователем | 1971 |

|

SU541257A1 |

| Шкальный индикатор | 1990 |

|

SU1767339A1 |

JT

I I L

Авторы

Даты

1973-01-01—Публикация