1

Изобретение относится к вычислительной технике.

Известна ячейка памяти, состоящая из двух тиристоров с двумя катодами, транзистора и резистора.

Для повышения быстродействия при малой потребляемой мощности в режиме хранения, новышения номехоустойчивост1И и уменьшения размеров ячейки в предлагаемой ячейке аноды тиристоров объединены и через резистор нагрузки подключены к источнику питания, /г-база каждого тиристора соединена с уо-базой другого тиристора перекрестно, коллектор транзистора соединен с источником питания, и цепь коллектор-эмиттер транзистора включена параллельно части резистора нагрузки, база транзистора и катоды тиристоров соединены с адресным входом ячейки, а другие катоды тиристоров - с соответствующими информационными входами ячейки.

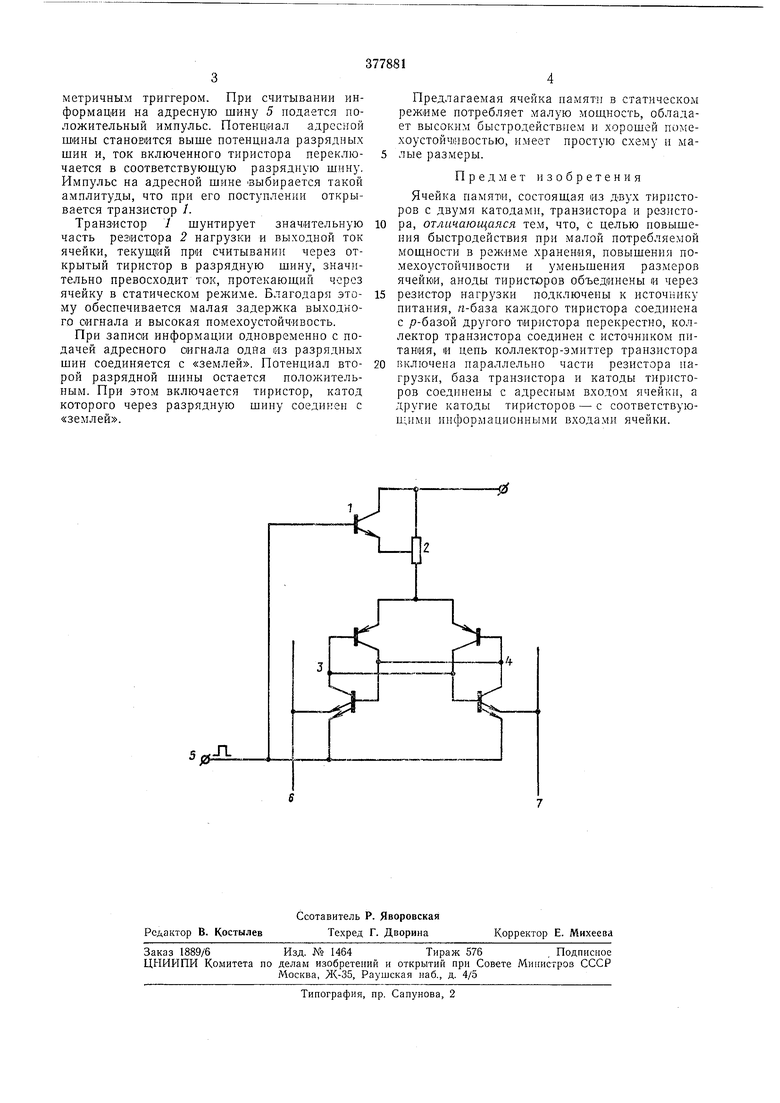

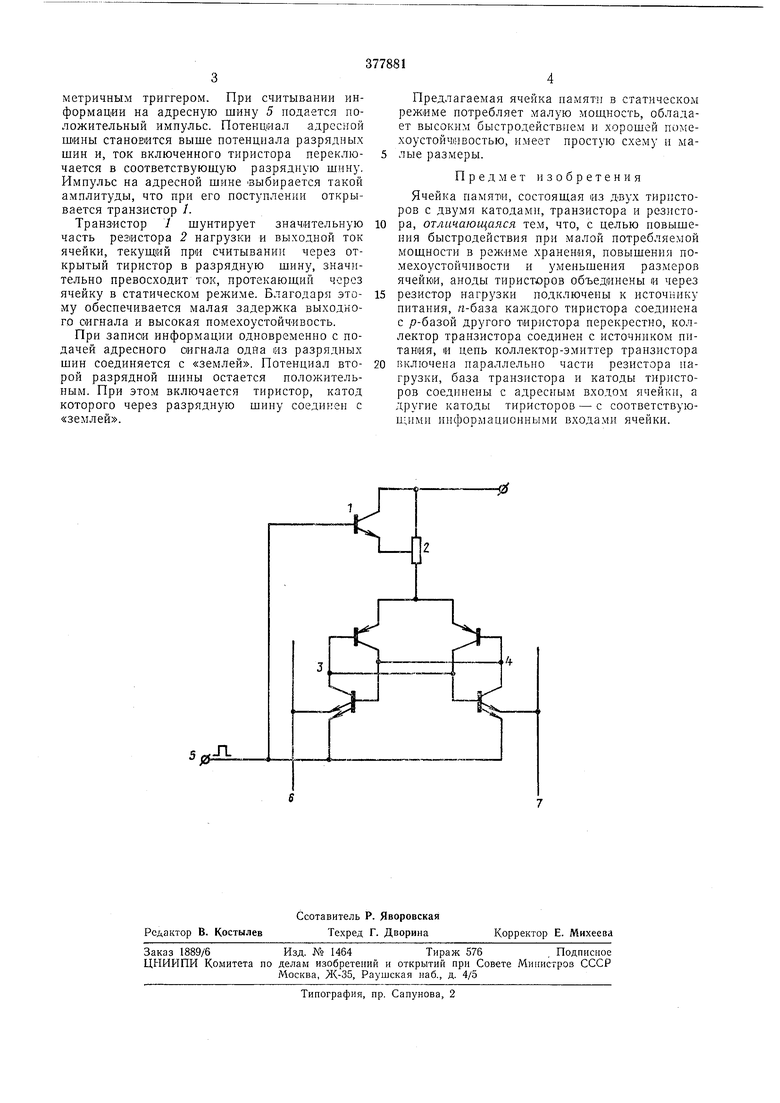

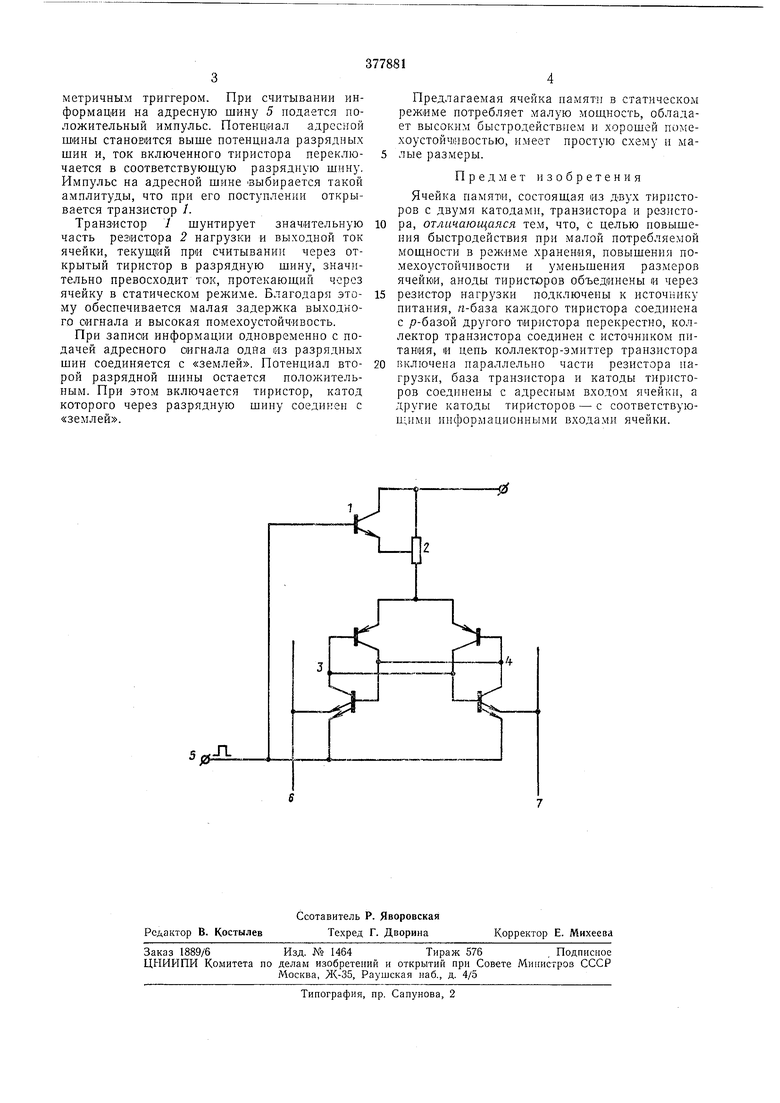

На чертеже приведена схема предлагаемой ячейки.

Ячейки состоят из коммутирующего транзистора /, резистора 2, двух тиристоров 5 и 4 со структурой р-п-р-п.

На чертеже тиристоры представлены в виде схемы, состоящей из п-р-п и р-п-р транзисторов. В интегральном исполнении р-п-р транзистор изготавливается в одном технологическом цикле с п-р-п транзистором в виде

так называемого «поперечного транзистора; п-р-п и р-п-р транзисторы составляют единую р-п-р-п структуру, расположенную в одной изолированной области. Коммутирующий

транзистор / также выполняется в одной изолированной области с резистором 2. Каждый тиристор имеет но два катода. Один из катодов обоих тиристоров соединяется с адресной (словарной) щиной 5. К адресной щине 5 нодсоединена также база транзистора /, коммутирующего нагрузочное сопротивление. Другие катоды тиристоров 3 и 4 подсоединяются к разрядным шинам 5 и 7 соответственно. Аноды обоих тиристоров соединены вместе и

подключены к резистору 2 нагрузки, /г-база каждого тиристора соединяется с /9-базой другого тиристора, образуя перекрестную обрагную связь. Ячейка работает следующим образом.

В режиме хранения информации адресная щина 5 имеет низкий иотенциал (подключена к «земле). Коммутирующий транзистор / заперт, и ток через ячейку определяется величиной сопротивления резистора 2. Один из тнристоров включен, другой - выключен, причем п-р-п и р-п-р транзисторы, входящие в состав включенного тиристора, щунтнруют оба базовых перехода другого тиристора. Это придает схеме более высокую помехоустойчивость по сравнению с транзисторным сим

метричным триггером. При считывании информации на адресную шину 5 подается положительный импульс. Потенциал адресной шины станоЕится выше потенциала разрядных шин и, ток включенного тиристора переключается в соответствуюш;ую разрядную шину. Импульс на адресной шине выбирается такой амплитуды, что при его поступлении открывается транзистор /.

Транзистор 1 шунтирует значительную часть резистора 2 нагрузки и выходной ток ячейки, текущий при считывании через открытый тиристор в разрядную шину, значительно превосходит ток, протекаюш;ий через ячейку в статическом режиме. Благодаря этому обеспечивается малая задержка выходного сигнала и высокая помехоустойчивость.

При записи информации одновременно с подачей адресного сигнала одна из разрядных шин соединяется с «землей. Потенциал второй разрядной шины остается положительным. При этом включается тиристор, катод которого через разрядную шину соединен с «землей.

Предлагаемая ячейка памяти в статическом режиме потребляет малую мош,ность, обладает высоким быстродействием и хорошей помехоустойчивостью, имеет простую схему и малые размеры.

Предмет изобретения

Ячейка памяти, состоящая из двух тиристоров с двумя катодами, транзистора и резистора, отличающаяся тем, что, с целью повышения быстродействия при малой потребляемой мощности в релшме хранения, повышения помехоустойчивости и уменьшения размеров ячейки, аноды тиристоров объединены и через

резистор нагрузки подключеиы к источнику питания, «-база каждого тиристора соединена с р-базой другого тиристора перекрестно, коллектор транзистора соединен с источником питания, и цепь коллектор-эмиттер транзистора

включена параллельно части резистора иагрузки, база транзистора и катоды тиристоров соединены с адресным входом ячейки, а другие катоды тиристоров - с соответствующими информационными входами ячейки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВПТБ Ш14Ш11Жу1 | 1973 |

|

SU409292A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Симметричный тиросторный элемент памяти | 1976 |

|

SU652613A2 |

| ОДНОВИБРАТОР | 1972 |

|

SU341143A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| СИММЕТРИЧНЫЙ ТИРИСТОРНЫЙ ЭЛЕМЕНТ НАМЯТИ | 1973 |

|

SU381098A1 |

| Ячейка памяти | 1977 |

|

SU637866A1 |

| Матричный накопитель для интегральных запоминающих устройств | 1977 |

|

SU710075A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

Авторы

Даты

1973-01-01—Публикация