I

Изобретение относится к вычислительной технике и может быть использовано в вычислительных и измерительных устройствах, обрабатывающих частотно-импульсную информацию.

Известен время-импульсный функциональный преобразователь, содержащий умножитель частоты, множительно-делительные блоки, реверсивные счетчики, логические триггеры и частотно-импульсный следящий блок. Однако он имеет низкую точность функционального преобразования, обусловленную погрешностью ключевых элементов, нелинейностью характеристик и конечным значением коэффициента усиления усилителя.

Для повыщения точности функционального преобразования устройства в нем входы вычитания реверсивных счетчиков множительноделительных блоков через умножитель частоты подключены к входу преобразователя, к одному входу триггера первого множительноделительного блока и через триггер к входу первой импульсно-потепциальной схемы другие импульсно-потенциальные схемы «И через триггеры, вторые входы которых подключены к щине опорной частоты, присоединены ко вторым входам триггеров и к выходам реверсивных счетчиков множительно-делительных блоков, входы суммирования которых через соответствующие импульсно-потенциальные схемы «И подключены к щине опорной частоты и к выходам триггеров множительно-делительных блоков.

Первые входы последних соединены с выходами предыдущих но номеру множительноделительных блоков.

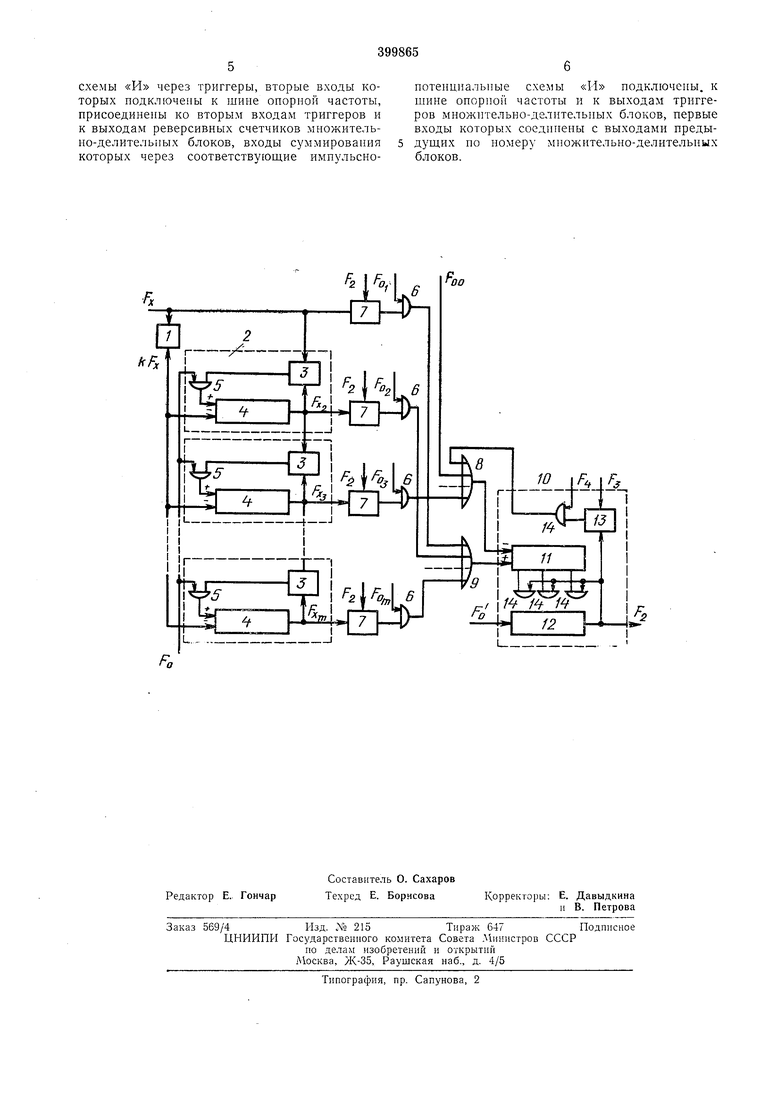

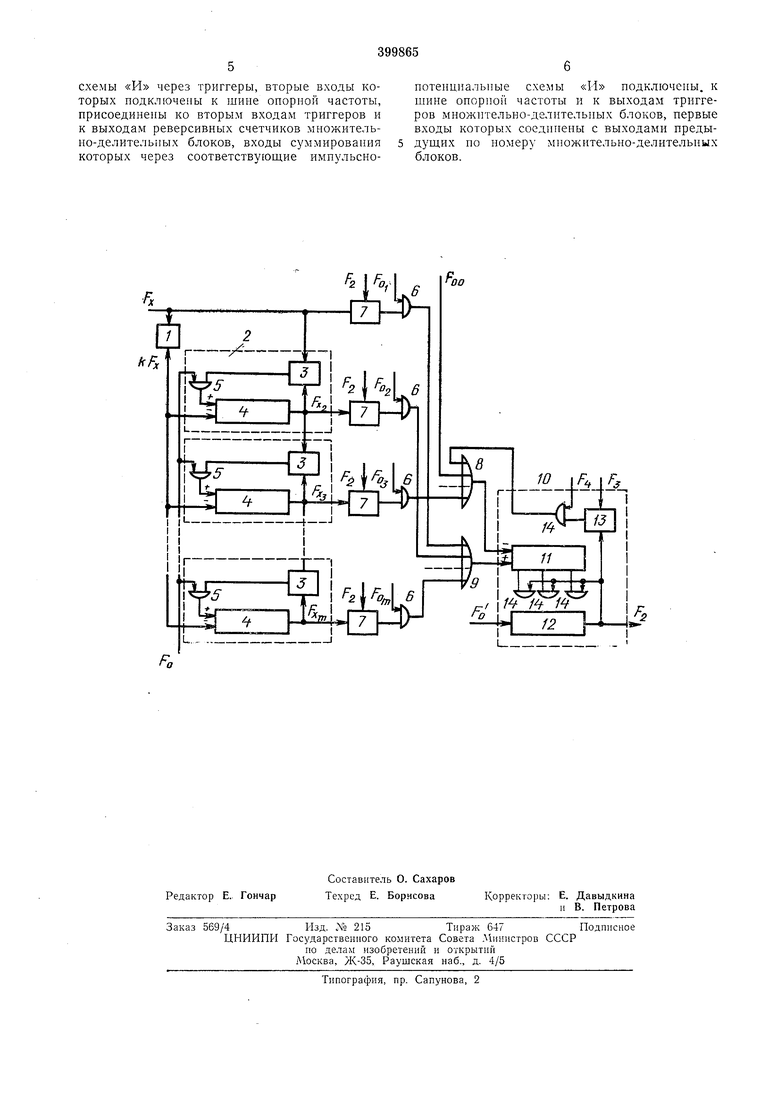

На чертеже приведена схема устройства. Она содержит умножитель частоты I, SiHOжительно-делительные блоки 2, состоящие из триггеров 3, реверсивных счетчиков 4, импульсно-потенциальных схем «И 5, импульсно-потенциальные схемы «И 6, триггеры 7, две схемы «ИЛИ 8 и 9, и частотно-импульсный следящий блок 10, состоящий из реверсивного счетчика 1, управляемого делителя частоты 12, триггера 13 и группы схем «И 14.

Вход преобразователя подключен к входу умножителя частоты , в котором входная частота FX умножается на коэффициент . Выход у.множителя частоты соединен с вычитающими входами реверсивных счетчиков 4 множительно-делительных блоков 2. Кроме того, вход преобразователя подключен ко входу триггера 7 и ко входу трнггера 3 первого множительно-делительного блока 2, выход которого соединен со входом триггера 3 второго множительпо-делительного блока 2 и т. д. Выходы множительно-делительных блоков 2. соответственно связаны со входами триггеров 7, вторые входы которых подключены к шине опорной частоты F, а выходы - к потенциальным входам импульсно-потенциальных схем «И 6, соединенных соответственно своими импульсными входами с шинами образцовых частот Foi, f 02, -, Рот- Выходы схем «И 6 и шина образцовой частоты FQ через схемы «ИЛИ 8 и 9 подключены к вычитаюшему и суммирующему входам реверсивного счетчика 11 частотно-импульсного следяш,его блока 10, в цепь обратной связи которой включены триггер 13 и импульснопотенциальная схема «И 14. Выход импульсно-потенциального следящего блока 10 является выходом преобразователя. Работа устройства заключается в следующем. Входная частотно-импульсная последовательность поступает на вход умножителя частоты 1, умножающего входную частоту FX на коэффициент /C l const. Использование умножителя 1 в функциональном преобразователе обеспечивает необходимое быстродействие. Частотно-импульсная последовательность kFx с выхода умножителя частоты 1 и входная FX поступают на соответствующие входы последовательно соединенных множительноделительных блоков 2. В множительно-делительном блоке 2, моделирующем квадратичную функцию, каждый импульс выходной частоты Fxz, являющийся импульсом переполнения реверсивного счетчика 4, переводит триггер 3 в состояние, при котором в течение периода Тх входной частоты в реверсивный счетчик 4 записывается число FoTy, которое списывается импульсами частоты kFx в течение периода выходной частоты Fx4 первого однорегистрового множительно-делительного блока, т. е. F,T ,,(1) . -ГНа выходе второго множительно-делительного блока 2 аналогично50 3 f лз -гг(3) и на выходе (i-1)-го устройства, моделирую- S5 щего степенную функцию х f i-Dfi Частотно-импульсные последовательности (/-1) 65 (, 2, 3 ..., т) поступают соответственно на входы триггеров 7 формирующих прямоугольные импульсы сквал :ности 0.. -, которые управляют импульсно-потенциальными «И 6 схемами. Импульсы в.г-г заполняются импульсами образцовых частот Foi, пропорциональных коэффициентам а; степенного ряда, аппроксимирующего воспроизводимую функцию. Тогда частота па выходе (i-1)-ой схемы «И 6 равна l(i-i)pi Р.1 Foi.i - -ITTC Частоты F-ii и образцовая частота FUO, соответствующая коэффициенту ряда, через схемы «ИЛИ 8 и 9 в зависимости от знаков слагаемых степенного ряда поступают на суммирующий или вычитающий входы реверсивного счетчика 11 частотно-импульсного следящего блока 10, реализующей операцию hjг сложения частотно-импульсных последовательностей. Иоскольку в цепь обратпой связи следящего блока 10 включены триггер 13, на вход которого подается частота FS и импульсно-потенциальная схема «И 14, на вход которой подается частота FH, то помимо суммирования частотно-импульсный следящий блок 10 реализует и множительно-делительную операцию. В установившемся режиме выражение для выходной частоты следящего блока 10 имеет вид .f F,.F(Из моделирующей зависимости (6) устройства видно, что оно производит также множительно-делительную операцию независимых переменных, представленных в виде частоты. Предмет изобретения Частотно-импульсный функциональный преобразователь, содержащий умножитель частоты, множительно-делительные блоки с триггерами, импульспо-потенциальными схемами «И и реверсивными счетчиками, триггеры и частотно-импульсный следящий блок, входы которого через схемы «ИЛИ и импульсно-потенциальные схемы «И подключены к щинам образцовых частот, отличающийся тем. что, с целью повышения точности, в нем входы вычитания реверсивных счетчиков множительно-делительных блоков через умножитель частоты подключены ко входу преобразователя, к одному входу триггера первого множительно-делительного блока и через триггер ко входу первой импульсно-потепциальной схемы другие импульсно-потенциальные

схемы «И через триггеры, вторые входы которых подключены к шине опорной частоты, присоединены ко вторым входам триггеров и к выходам реверсивных счетчиков множительно-делительиых блоков, входы суммирования которых через соответствующие импульснопотенциальные схемы «И подключены, к шине опорной частоты и к выходам триггеров множителы-ю-делительных блоков, первые входы которых соединены с выходами предыдуш,их по номеру множительно-делительных блоков.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1973 |

|

SU407317A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU419921A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU363990A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU385290A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU425182A1 |

| ВРЕМЯ-ИМПУЛЬСНЫЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU353343A1 |

| ПАТЕНТКО-ТЕХ;1И'!ЕСНАеБИБЛИОТЕКА | 1971 |

|

SU306473A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ УСТРОЙСТВО для ВЫЧИСЛЕНИЯ ТРИГОНОМЕТРИЧЕСКИХ ФУНКЦИЙ | 1973 |

|

SU389517A1 |

| Цифровой следящий частотомер | 1980 |

|

SU892335A1 |

| ЧАСТОТНО-ИМПУЛЬСНЫЙ ИНТЕГРАТОР | 1972 |

|

SU350013A1 |

Авторы

Даты

1973-01-01—Публикация