1

Изобретение относится к области электроизмерительной техники и может быть использовано при построении устройств для вычисления логарифмов, децибелметров, а также нри построении множительно-делительных устройств.

Известны логарифмические функциональные преобразователи, содержащие генератор экспоненциального напряжения, схему сравнения, триггер, выход которого связан с управляющим входом ключа, соединенного с сумматором. Такие преобразователи имеют низкую точность, небольщой динамический диапазон, низкое быстродействие. Кроме того, для получения результата в цифровом виде необходим дополнительный преобразователь.

Цель изобретения - повышение точности и быстродействия логарифмических преобразователей. Это достигается тем, что в преобразователь введены блок управления, подключенный к одному из входов триггера и к управляющему входу ключа формирователя линейно нарастающего напряжения, и функциональный частотный преобразователь, один вход которого подключен к выходу интегратора, другой - к источнику опорного напряжения, а выход через ключ управления сумматором соединен со счетчиком.

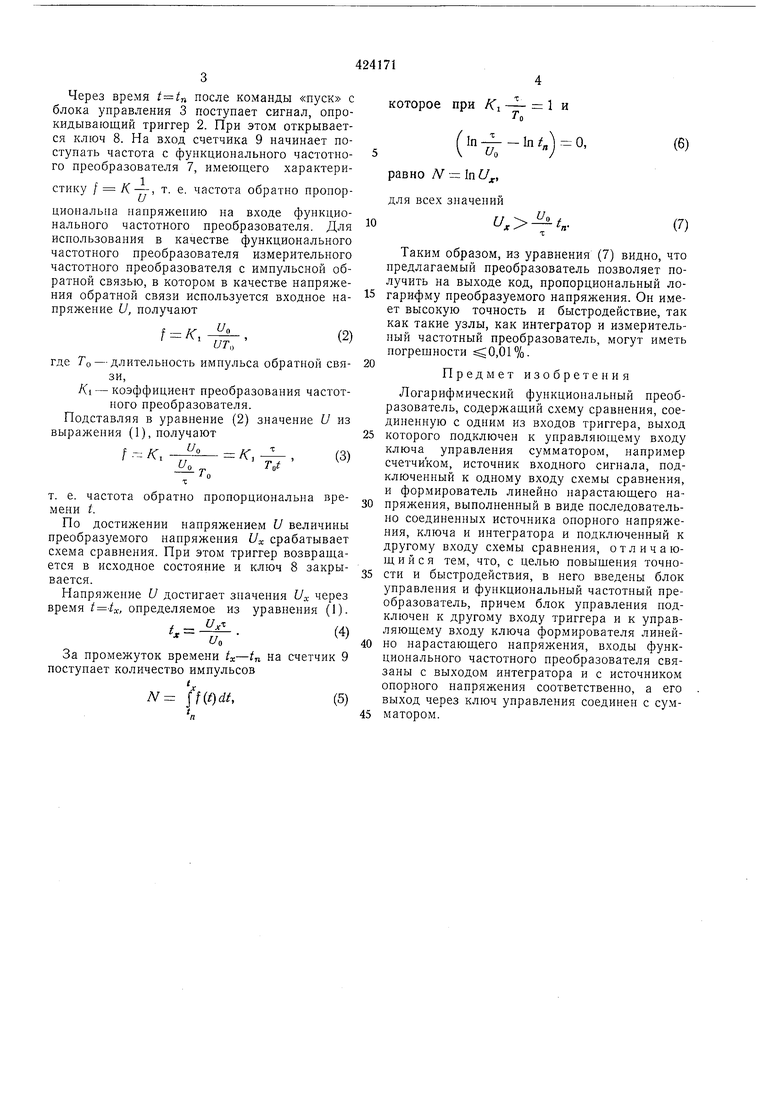

На фиг. 1 изображена блок-схема предлагаемого логарифмического функционального

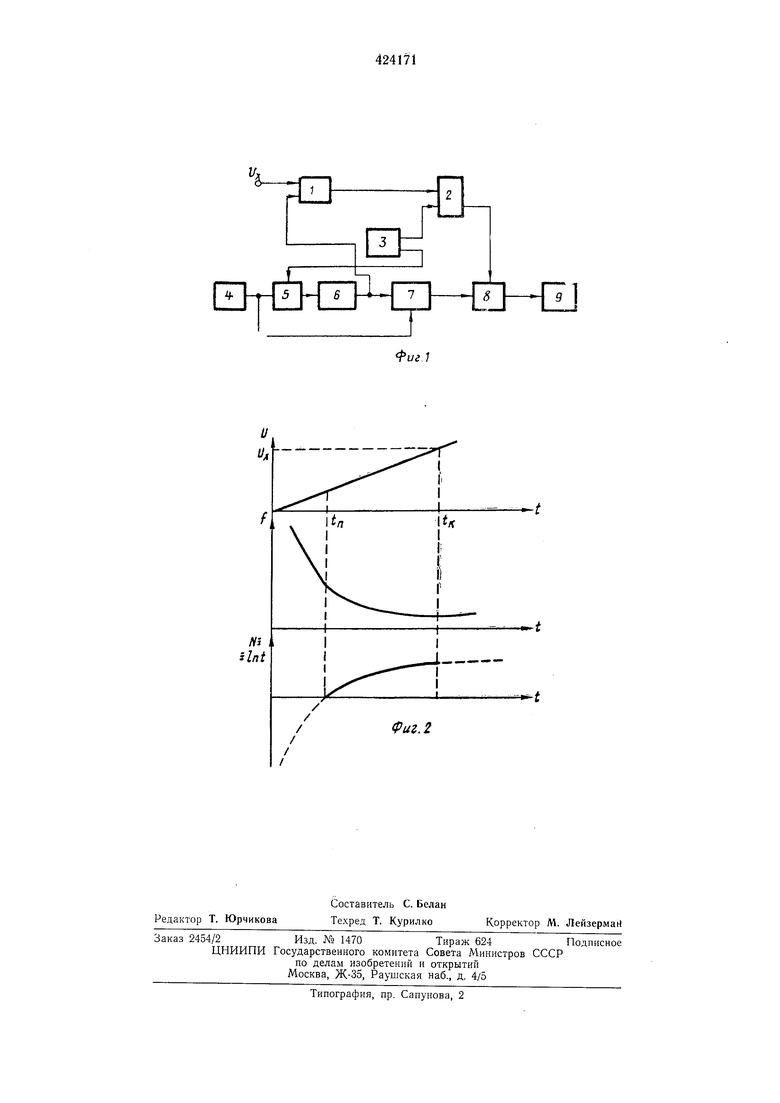

преобразователя; на фиг. 2 - временные диаграммы, поясняющие его работу.

В преобразователе напряжение L/x подведено к одному из входов схемы 1 сравнения, выход которой подключен к триггеру 2. Второй вход триггера соединен с блоком 3 управления. Выход источника 4 опорного напряжения соединен с ключом 5, второй вход которого подк.тючен к блоку управления. Выход ключа

через интегратор 6 подключен к другому входу схемы сравнения и к входу функционального частотного преобразователя 7, выход которого через ключ 8 соединен с сумматором, выполненным на счетчике 9. Второй вход ключа 8 подключен к выходу триггера, а второй вход функционального частотного преобразователя - к выходу источника опорного напряжения.

В исходном состоянии ключи 5 и 8 закрыты, на один из входов схемы сравнения подается преобразуемое напряжение U. По команде «пуск с блока 3 открывается ключ 5 и напряжение UQ с блока 4 поступает на вход интегратора 6. На выходе интегратора напряжение изменяется по закону

,(1)

где т - постоянная времени интегратора, 30t - время.

Через время после команды «пуск с блока управления 3 поступает сигнал, опрокидывающий триггер 2. При этом открывается клЕОч 8. На вход счетчика 9 начинает поступать частота с функционального частотного преобразователя 7, имеющего характеристику / /( -, т. е. частота обратно пропорциональна напряжению на входе функционального частотного прео;бразователя. Для использования в качестве функционального частотного преобразователя измерительного частотного преобразователя с импульсной обратной связью, в котором в качестве напряжения обратной связи используется входное напряжение и, получают

и.

(2)

f K,

ит,

где Го - длительность импульса обратной связи,

/Ci - коэффициент преобразования частотного преобразователя.

Подставляя в уравнение (2) значение U из выражения (1), получают

f - К. -- К,,(3)

г

T,t

- о

т

т. е. частота обратно пропорциональна времени t.

По достижении напряжением И величины преобразуемого напряжения Ну срабатывает схема сравнения. При этом триггер возвращается в исходное состояние и ключ 8 закрывается.

Напряжение U достигает значения Их через время , определяемое из уравнения (1).

JV.

(4) с/о

За промежуток времени 4-tn на счетчик 9 поступает количество импульсов /„

N lf(t)dt,

(5)

которое при ATi - 1 и

TU

()

(6)

(7)

tnТаким образом, из уравнения (7) видно, что предлагаемый преобразователь позволяет получить на выходе код, пропорциональный логарифму преобразуемого напряжения. Он имеет высокую точность и быстродействие, так как такие узлы, как интегратор и измерительный частотный преобразователь, могут иметь погрешности 0,01%.

Предмет изобретения

Логарифмический функциональный преобразователь, содержащий схему сравнения, соединенную с одним из входов триггера, выход

которого подключен к управляющему входу ключа управления сумматором, например счетчиком, источник входного сигнала, подключенный к одному входу схемы сравнения, и формирователь линейно нарастающего напряжения, выполненный в виде последовательно соединенных источника опорного напряжения, ключа и интегратора и подключенный к другому входу схемы сравнения, отличающийся тем, что, с целью повыщения точности и быстродействия, в него введены блок управления и функциональный частотный преобразователь, причем блок управления подключен к другому входу триггера и к управляющему входу ключа формирователя линейно нарастающего напряжения, входы функционального частотного преобразователя связаны с выходом интегратора и с источником опорного напряжения соответственно, а его выход через ключ управления соединен с сумматором.

nu

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический преобразователь | 1978 |

|

SU765819A1 |

| Логарифмический функциональный преобразователь | 1974 |

|

SU484529A1 |

| Логарифмический преобразователь | 1974 |

|

SU512475A1 |

| Аналого-цифровой преобразователь двойного интегрирования | 1981 |

|

SU1001464A1 |

| Логарифмический аналого-цифровой преобразователь | 1978 |

|

SU729840A1 |

| Функциональный кодирующий преобразователь | 1973 |

|

SU484639A1 |

| Устройство для возведения в степень | 1977 |

|

SU653619A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Логарифмический функциональный преобразователь | 1974 |

|

SU516050A1 |

| Функциональный частотный преобразователь | 1973 |

|

SU447723A1 |

Ы1ыи

t

Фиг. 2

Даты

1974-04-15—Публикация

1972-12-08—Подача