1

Изобретение относится к устройствам, предназначенным для логарифмического преобразования сигналов, и может быть использовано в аналоговых вычислительных машинах.

Известен логарифмический аналогоцифровой преобразователь, содержащий генератор экспоненциального напряжения , компаратор, блок синхронизации Cl JНедостатком этого устройства явлется малый диапазон входного сигнала.

Наиболее близким к предложенному является логарифмический аналогоцифровой преобразователь, содержащий КС-цепь, между резистором которой и общей шиной включен первый ключ, источник опорного напряжения, соединенный через второй ключ с RC-цепью и неинвертирующим входом буферного усилителя, выход которого соединен с его инвертирующим входом и первым входом компаратора, выход которого подключен к первому входу блока управления, второй вход которго соединен с генератором импульсов первьсй и второй, выходы блока управления соответственно подключены к управляющим входам первого и второг ключа, третий и четвертый выход соответственно к входу счетчика ста ших и младших разрядов, пятый выход - к установочному входу счетчика, а шестой выход - к разрядному ключу интегратора, выход интегратора подключен кпервому входу сумматора, второй вход которого соединен с входной шиной, а выход подключен к первому входу компаратора, второй вход которого подключен к первому входу дифференциального усилителя через дополнительный усилитель, а к второму входу - непосредственно,вхо интегратора соединен с выходом дифференциального усилителя C2L

Однако известное устройство обладает узким диапазоном величин входного сигнала и сложной функциональной схемой.

Целью изобретения является расширение диапазона входного сигнала и упрощение преобразователя.

Эта цель достигается тем, что в логарифмический аналого-цифровой преобразователь, содержащий накопительный конденсатор, первая обкладк которого через разрядный резистор соединена с шиной нулевого потен18482

циала, источник опорного -,пряжения, выход которого через перВ)ГЙ ключ подключен к первой обкладке накопительного конденсатора, вторая обк-падка которого соединена с шиной нулевого потенциала, операционньй усилитель, выход которого подключен к тактирующему входу блока синхронизации, первый выход

jQ которого соединен с управляющим

входом первого ключа, к входу переда чи импульсов блока синхронизации подключен выход генератора импульсов, второй выход блока синхрониза ции подключен к входу запуска реверсивного счетчика, счетный вход которого соединен с третьим выходом блока синхронизации, второй и третий ключи, введены запоминающий конденд сатор, токоограничительный резистор, первый я второй масштабные резисторы и пороговый элемент, причем первый вывод первого масштабного резистора является входом преобразователя,

а второй вывод соединен с первым выводом второго масштабного резистора, с инвертирующим входом операционного усилителя и с первым выводом токоограничительного резистора,второй вывод которого через запоминающий конденсатор подключен к неинвертир 1ощему входу операционного усилиТзля, второй вывод токоограничительного резистора через второй ключ соединен с шиной нулевого потенциа5 ла, кеинвертирующий вход операционного усилителя через третий ключ соединен с шиной нулевого поТен14иала, ме.-аду инвертирующим входом и выходом операционного усилителя подключен пороговый элемент,управляющий вход второго ключа соединен с четвертьм выходом блока синхронизации, первый выход которого подключен к управляющему входу третьего ключа, выход переноса реверсивного счетчика подключен к входу останова блока синх зонизации, установочный вход реверсивного счетчика является

входом начального кода преобразова0 теля.

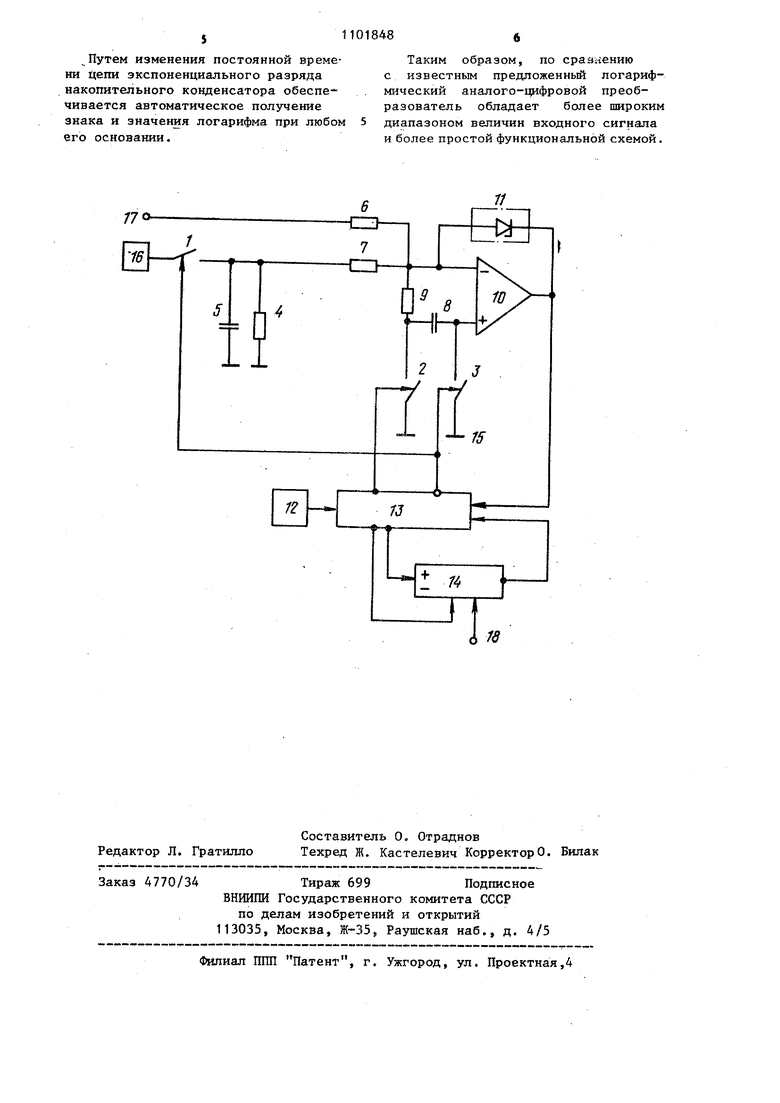

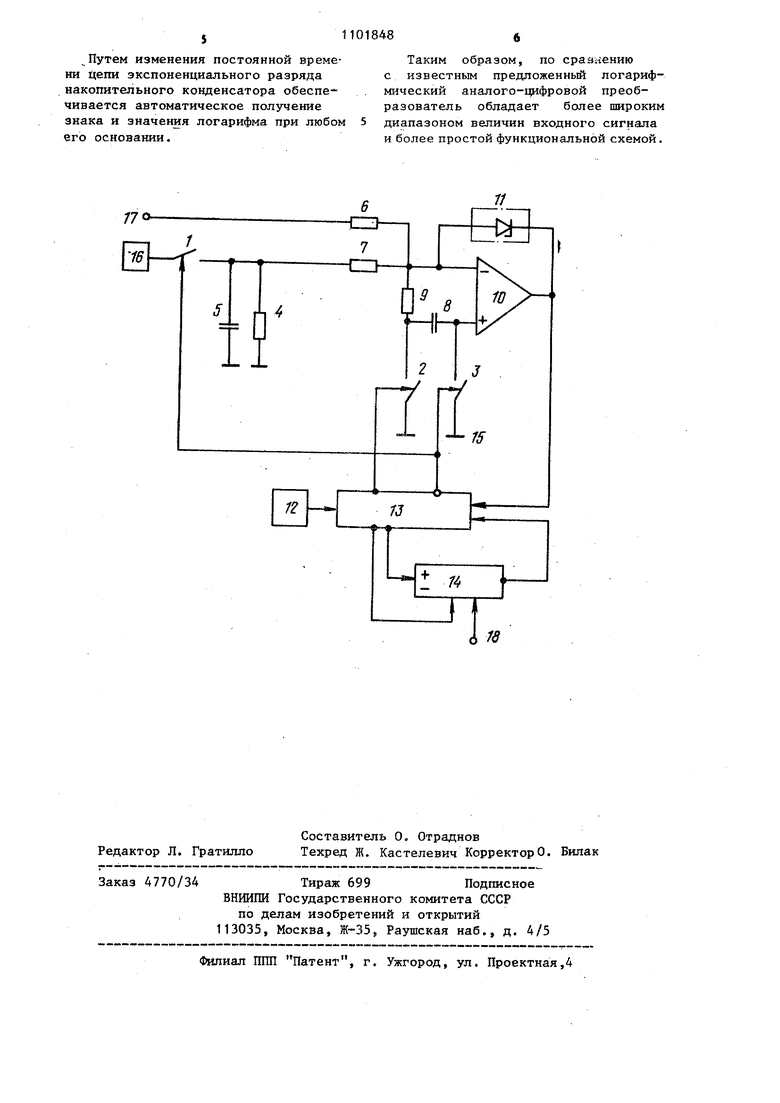

На чертеже изображена функциональная схема логарифмического аналого-цифрового преобразователя.

Устройство содержит первый,второй 5 к третий ключи 1-3, разрядный резистор 45 накопительный конденсатор 5, первый и второй масштабные резисторы 6 и 7, запомг-гнающий конденсатор 8, токоограничительный резистор 9, опе рационньй усилитель 10, пороговый элемент 11, выполненный на стабилит не, генератор 12 импульсов,блок 13 синхронизации, реверсивный счетчик 14, шину 15 нулевого потенциала, источник 16 опорного напряжения, вход 17, вход 18 начального кода. Логарифмический аналого-цифровой преобразователь работает следующим образом. В исходном положении первый и тр тий ключи 1 и 3 замкнуты, а второй ключ 2 разомкнут. Напряжение на накопительном конденсаторе 5 равно опорному напряжению. Это напряжение через второй масштабный резистор 7 приложено к неинвертирующему входу операционного усилителя 10, используемому в качестве компаратора, а напряжение с входа 17 через первый масштабньй резистор 6 приложено к инвертирующему входу операционного усилителя 10 полярностью, противопо ложной опорному напряжению. Операционный усилитель 10 пороговым элементом 11, в качестве которого можн использовать, например, стабилитрон установлен в активный режим, чем обеспечивается на его инвертирующем входе потенциал, близкий к нулю. Напряжение смещения нуля на инверти рующем входе операционного усилител 10 запоминается на запоминающем конденсаторе 8. По команде Пуск производится установка начального кода реверсивного счетчика 14 и перевод его в режим вычитания, первый и третий ключи 1 и 3 размыкаются, второй клю 2 замыкается и начинается экспоненциальный разряд запоминающего конденсатора 5 через разрядный 4 и вто рой масштабный 7 резисторы. При этом операционный усилитепь 10 производит сравнение токов по цепи второго масштабного резистора 7 со стороны экспоненциального напряжения и первого масштабного резистора 6 со стороны напряжения с входа 17 За счет переключения второго и трет его ключей 2 и 3 по сигналу Пуск неинвертирующий вход операционного усилителя 10 прикладывается напряже ние, равное напряжению смещения нуля, но противоположное по знаку, чем обеспечивается его компенсация за счет активного режима работы опе рационного усилителя 10. По достижению баланса токов в цепи первого и второго масштабных резисторов 6 и 7 происходит смена знака тока компенсации по цепи порогового .элемента 11 блоком 13 синхронизации и осуществляется перевод преобразователя в исходное положение , при этом от момента подачи сигнала Пуск до выработки перепада на выходе операционного усилителя 10 блоком 13 синхронизации формируется временной интервал, пропорциональный логарифму входного напряжения . Во время экспоненциального разряда накопительного конденсатора 5 сигнал с выхода генератора 12 импульсов поступает на реверсивньш счетчик 14 до момента завершения преобразования. При этом в реверсивном счетчике 14 запишется число, эквивалентное значению напряжения. В зависимости от уровня входного напряжения возможны два вида преобразования . Если логр.рифм входного напряжения больше нуля, то реверсивньш счетчик 14 работает на вычитание без смены направления счета. Если логарифм меньше нуля, то по достижению в реверсивном счетчике 14 нулевого значения кода происходит смена направления счета (переход на режим сложения). При этом в реверсивном счетчике 14 по завершению преобразования фиксируется число, пропорциональное значению логарифма входного напряжения. Знак полученного цифрового значения логарифма всегда противоположен знаку (направлению) счета реверсивного счетчика 14 на конец преобразования. При равных величинах первого и второго масштабных резисторов 6 и 7 установочный код реверсивного счетчика 14 равен значению логарифма опорного напряжения. За счет уменьшения в предлагаемом логарифмическом аналого-илкровом преобразователе активных элементов расширяется диапазон преобразуемых напряжений в сторону больших величин, а за счет компенсации смещения нуля операционного усилителя обеспечивается преобразование входного напряженя в области малых величин. Кроме того, предложенньпЧ логарифмический аналого-цифровой преобразователь имеет более простую функциональную схему. Путем изменения постоянной време ни Депн экспоненциального разряда накопительного конденсатора обеспе-чивается автоматическое полз чение знака и значения логарифма при любом его основании. Таким образом, по сравнению с известным предложенный логарифмический аналого-цифровой преобразователь обладает более широким диапазоном величин входного сигнала и более простой функциональной схемой.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Логарифмическое вычислительное устройство | 1987 |

|

SU1543425A1 |

| Функциональный преобразователь | 1980 |

|

SU883924A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112374A1 |

| Устройство для логарифмирования отношения сигналов | 1982 |

|

SU1112375A1 |

| Логарифмический аналого-цифровой преобразователь | 1981 |

|

SU947874A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Логарифмический аналого-цифровойпРЕОбРАзОВАТЕль | 1979 |

|

SU836637A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

ЛОГАРИФМИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий накопительньй конденсатор, первая обкладка которого через разрядный резистор соединена с шиной нулевого потенциала, источник опорного напряжения, выход которого через первый ключ подключен к первой обкладке накопительного конденсатора, вторая обкладка которого соединена с шиной нулевого потенциала, операционный усилитель, выход которого подключен к тактирующему входу блока синхронизации, первый выход которого соединен с управляющим входом первого ключа,к входу передачи импульсов блока синхронизации подключен выход генератора импульсов, второй выход блока синхронизации подключен к входу запуска реверсивного счетчика, счетный вход которого соединен с третьим выходом блока синхронизации, второй и третий ключи, отличающийся тем, что, с целью расширения диапазона входного сигнала и упрощения преобразователя, в него введены запоминающий конденсатор, токоограничительный резистор , первьй и второй масштабные резисторы.и пороговый элемент, причем первый вывод первого масштабного резистора является входом преобразователя, второй вывод соединен с первым выводом второго масштабного резистора, с инвертирующим входом операционного усилителя и с первым выводом токоограничительного резистора,второй вывод которого через запоминающий конденсатор подключен к неинвертирующему входу операционного усили§ теля, второй вывод токоограничительного резистора через второй ключ (Л соединен с шиной нулевого .потенциала, с неинвертирующий вход операционного усилителя через третий ключ соединен с шиной нулевого потенциала, между инвертирующим входом и выходом операционного усилителя подключен пороговый злемент, управляющий вход второго ключа соединен с четвертым выходом блока синхронизации,первый 00 4;: выход которого подключен к управляющему входу третьего ключа, выход переноса реверсивного счетчика под00 ключен к входу останова блока синхронизации, установочный вход реверсивного счетчика является входом начального кода преобразователя.

77

18

Авторы

Даты

1984-07-07—Публикация

1982-05-03—Подача