Аналого-цифровой преобразователе двойного интегрирования предназначен для использования в цифровой электроизмерительной технике.

Известен преобразователь, содержащий два ключа, первый и второй триггеры упра:вления ключами, интегратор, блок сравнения, третий триггер, элемент совпадения на два входа, тактовый генератор и счетчик. В этом преобразователе в течение двух тактов интегрирования преобразуемого и эталонного напряжений формируется цифровой код, который является линейной функцией входного напряжения IjНедостатком этого преобразователя является невозможность получения кода, пропорционального логарифму входного напряжения.

Цель изобретения - расширение функциональных возможностей аналогоцифрового преобразователя двойного интегрирования.

Поставленная цель достигается тем, что в аналого-цифровой преобразователь двойного интегрирования/ содержащий два ключа, первые входы которых соединены соответственно с шинами входного сигнала и эталонного напряжения, вторые входы соответственно с выходами первого и второго триггеров, а выходы - с входом интегратора, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с шиной опорного напряжения, первый выход - с первым входом третьего триггера, второй выход - с

10 вторым входом третьего триггера и первьм входом второго триггера, второй вход которого соединен с пер- вым входом первого триггера, второй вход которого соединен с шиной

15 Запуск, введены трехвходовой элемент И, генератор переменной частрты, блок управления частотой, элемент задержки счета, вспомогательный счетчик, блок управления счето

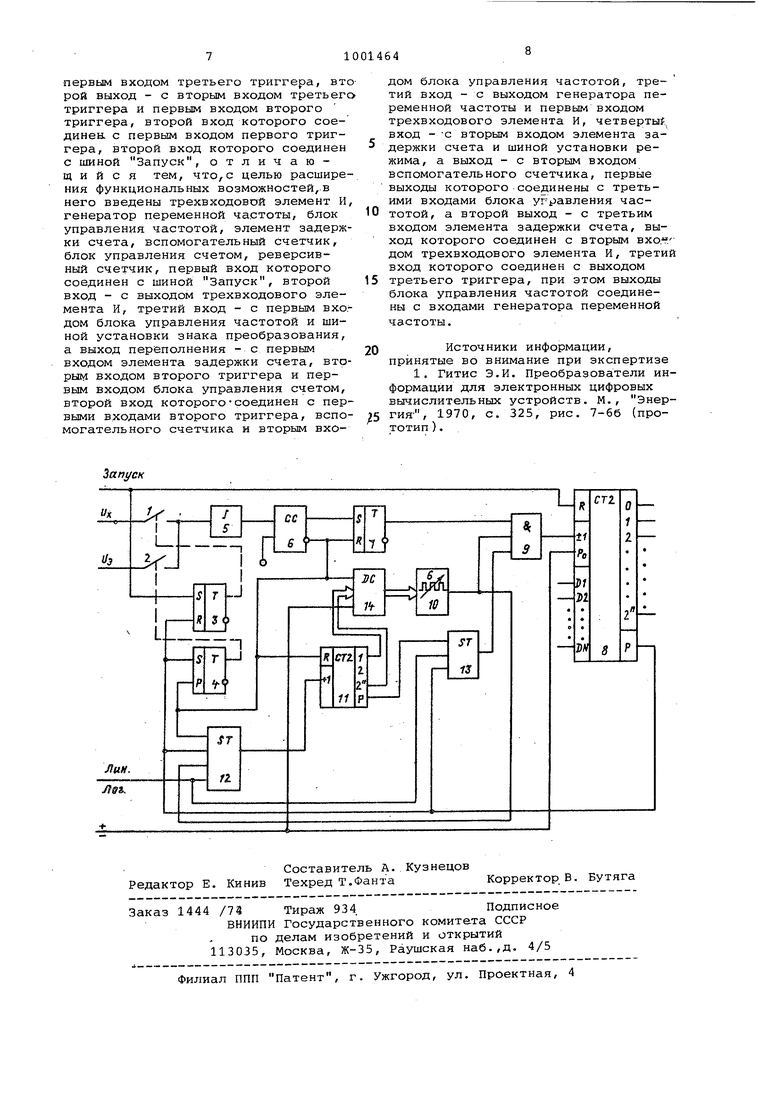

20 реверсивный счетчик, первый вход которого соединен с шиной Запуск, второй с выходом трехвходового элемента И, третий вход - с первым входом блока управления час25тотой и шиной установки знака преобразования, а выход импульса переполнения - с первым входом элемен- . та задержки счета, вторым входом второго триггера и первым входом 30 блока управления счетом, второй вход которого соединен с первыми выходам второго триггера, вспомогательного счетчика и вторым входом блока упр ления частотой, третий вход - с вы ходом- генератора переменной частоты и первым входом трехвходового элемента И, четвертый вход - с вто рым входом элемента задержки счета, и шиной установки режима преобразователя, а выход - с вторым входом вспомогательного счетчика, первые выходы которого соединены с третьими входами блока управления частотой, а второй выход - с треть им входом элемента задержки .счета, выход которого -соединен с вторым в .дом трехвходового элемента И, третий вход которого соединен с выходом третьего триггера, при этом выходы блока управления частотой соединены с входами генератора пер менной частоты. На чертеже представлена схема аналого-цифрового преобразователя двойного интегрирования. Преобразователь содержит два клю ча 1 и 2, два триггера 3 и 4 управ ления ключами, интегратор 5, блок сравнения, третий триггер 7, ревер сивный счетчик 8, трехвходовый эле мент И 9, генератор 10 изменяемой частоты, вспомогательный счетчик 1 блрк 1-2 управления счетом, элемент 13 задержки счета, блок 14 управле ния частотой. Ключи 1 и 2, управляющие входы, которых подключены к выходам триггеров 3 и 4., подключены к входу интегратора 5, Вход S-триггера 3 подключен к входу Запуск преобразова теля, R триггера 3 и вход 5 триггера 4 подключены к выходу пере полнения счетчика 8, а вход R. триггера 4 подключен к инверсному выходу блока б сравнения. Выход интегратора 5 подключен к первому входу блока 6 сравнения, второй вход предназначен для подачи на него опорного напряжения. Прямой и инверсный выходы блока б сравнения подключены к выходам 9 и R третьего триггера 7, к выходу которого по ключен первый вход элемента И 9-, второй вход ее подключен к выходу генератора 10, а третий вход - к элемента 13 задержки счета. Выход элемента И 9 подключен к счет ному входу реверсивного счетчика, на управляющий вход которого подключен вход + преобразователя. К входам-управления генератора 10 подключены выходы блока 14 управления частотой, к входам которого подключены инверсный выход блока 6 сравнения, вход + преобразователя и выходы счетчика 11 Один из выходов счетчика 11 подключен к входу элемента 13 задержки счета, к второму входу которой подключен вход Лин/лог преобразователя, к третьему входу подключен выход переполнения счетчика 8. К счетному входу счетчика 11- подключен выход блока 12 управления счетом, к первому входу которого подключен инверсный выход блока б сравнения, к второму входу подключен выход переполнения счетчика 8, к третьему - выход генератора 10 и к четвертому - вход Лин/лог преобразователя. При работе преобразователя в линейном режиме блок 12 управления счетом по сигналу на управляющем входе Лин/лог преобразователя переводится в такое состояние, при котором импульсы с выхода генератора 10 изменяемой частоты не проходят через него. Реверсивный счетчик 8 устанавливается в режим суммирования, а вспомогательный счетчик 11 во время первого и второго такта интегрирования остается установленным в нулевое состояние, поэтому частота генератора 10 изменяемой частоты остается неизменной. На выходе элемента 13 задержки счета при этом все время поддерживается единичный разрешающий сигнал, а преобразователь работает в режиме линейного преобразования входного напряжения в цифровой код. Сигналом по входу Запуск реверсивный счетчик 8 устанавливается в нулевое состояние, а триггер 3 - в единичное состояние. Сигнал с выхода триггера 3 открывает ключ,, через который подается на вход интегратора 5 преобразуемое напряжение. Когда напряжение на выходе интегратора 5 превышает опорное напряжение UQ блок 6 сравнения устанавливает триггер 7 в единичное состояние. Сигнал с единичного выхода триггера 7 открывает трехвходовый элемент И 9. Импульсы с выхода тактового генератора 10 начинают посту пать на счетный вход реверсивного счетчика 8 (работает в режиме суммирования }. После переполнения счетчи ка 8 импульсом с выхода переполнения R триггер 3 устанавливается в нулевое состояние, а триггер 4 в единичное. Ключ 1 закрывается, а ключ 2 открывается сигналом с выхода триггера 4,и напряжение U подается на вход интегратора 5. Полярность напряжения Ug противоположна полярности преобразуемого напряжения и емкость интегратора 5 начинает разряжаться, одновременно продолжается поступление импульсов на вход счетчика 8,

После уменьшения выходного нэпряжения интегратора до значения меньшего, чем опорное, блок 6 сравнения переходит в исходное состояние. При этом триггер 7 устанавливается в нулевое состояние, трехвходовой элемент и 9 запирается и прекращается подача импульсов на вход счетчика 8, После этого с выходов счетчика считывается результат преобразования и цикл работы в преобразователе заканчивается.

Установка логарифмического режим работы обеспечивается подачей соответствующего сигнала по управляющему входу преобразователя Лин/ лог. При этом в течение первого такта интегрирования преобразова-тель работает так же, как и в линейном режиме. Блок 12 управления счетом остается закрытым ( не пропускает импульсы на вход вспомогательного счетчика),и с выхода элемента 13 задержки счета подается единичный (разрешающий) сигнал на вход трехвходового элемента И 9. После прохождения импульса переполнения с выхода счетчика 8 ключи 1 и 2, триггеры 3 и 4, интегратор 5, блок б сравнения и триггер 7 работают так же, как и в линейном режиме, но при этом открывается блок 12 управления счетом, поступают импульсы на вход вспомогательного счетчика и устанавливается нулевой С запрещающий) сигнал на выходе элемента 13 задержки счета.

Емкость вспомогательного счетчика 11 выбрана такой, чтобы время полного заполнения его импульсами тактового генератора {при сохранени той же частоты что и в течение первого такта интегрирования ) было равно времени разряда емкости интегратора 5 на величину напряжения, принтое за основание логарифмирования. До окончания заполнения вспомогательного счетчика на выходе элемента 13 задержки счета поддерживается сигнал, запрещающий прохождение импульсов генератора 10 через трехвходовой элемент И 9 на вход счетчика 8. Частота следования импульсов генератора 10 при этом остается неизменной . .

После прохождения импульсов с выхода переполнения вспомогательного счетчика на выходе элемента 13 задержки счета устанавливается сигнал, разрешающий прохождение импульсов генератора 10 через трехвходовой элемент И 9. Одновременно сигналами с выходов вспомогательного счетчика 11 через блок 14 управления частотой начинает изменяться период следования импульсов генератора 10 изменяемой частоты в соответствии с показательной функцией.

При этом, если сигналом на выходе + преобразователя задан режим формирования положительного значения логарифма, длительность периода тактовых импульсов увеличивается С по отношению к значению,установленному в первом такте интег- рирования}, а счетчик устанавливается (по входу Рд) в режим суммирования. В случае установки по вхо0ду + режима формирования отрицательного значения логарифма после переполнения счетчика 8 с помощью fixor дов установки кода в него записывается число, соответствующее максимальному- ( для выбранного диапазона

5 логарифмирования) значению логарифма, длительность периода тактового генератора 10 увеличивается так же, как и при формировании положительного значения логарифма. При этом

0 счетчик 8 устанавливается ( по входу PQ) в режим вычитания. Цифровой эквивалент изменяется от нуля до максимального значения для режима формирования положительного значения

5 логарифма и от максимального значения до нуля для режима формирования отрицательного значения логарифма соответственно изменению входного напряжения от величины выбранного

0 основания логарифмирования до максимального значения.

Таким образом, подачей соответствукядих сигналов по входам управления режимом работы преобразователя обес5печивается перевод его из линейного режима преобразования в логарифмический и обратно.

Применение в аналого-цифровом преобразователе двойного интегри0рования трехвходового элемента И, генератора изменяемой частоты, реверсивного и вспомогательного счетчика, блока управления, элемента задержки счета, блока управления

5 частотой позволило расширить его функциональные возможности, т.е. обеспечить линейный и логарифмический режимы преобразования при сохранении .таких достоинств его, как надежность и точность.

0

Формула изобретения

Аналого-цифровой преобразователь войного интегрирования, содержащий два ключа, первые входы которых соединены соответственно с шинами входного сигнала и эталонного напряжения, вторые входы - соответственно с выходами первого и второго триггеров, а выходы - с входом интегратора, выход которого соединен с первым входом блока сравнения, второй вход которого соединен с шиной опорного напряжения, первый выход - с

первьм входом третьего триггера, второй выход - с вторым входом третьего триггера и первым входом второго триггера, второй вход которого соединен, с первым входом первого триггера, второй вход которого соединен с ишной Запуск, отличающийся тем, целью расширения функциональных возможностей, в него введены трехвходовой элемент И, генератор переменной частоты, блок управления частотой, элемент задержки счета, вспомогательный счетчик, блок управления счетом, реверсивный счетчик, первый вход которого соединен с шиной Запуск, второй вход - с выходом трехвходового элемента И, третий вход - с первым входом блока управления частотой и шиной установки знака преобразования, а выход переполнения - с первым входом элемента задержки счета, вторым входом второго триггера и первым входом блока управления сч:етом, второй вход которого-соединен с первыми входами второго триггера, вспомогательного счетчика и вторым вхоЗапуск

дом блока управления частотой, третий вход - с выходом генератора переменной частоты и первым входом трехвходового элемента И, четвертый вход - С вторым входом элемента задержки счета и шиной установки режима, а выход - с вторым входом вспомогательного счетчика, первые выходы которого соединены с третьими входами блока управления частотой, а второй выход - с третьим входом элемента задержки счета, выход которого соединен с вторым вхо. дом трехвходового элемента И, трети вход которого соединен с выходом третьего триггера, при этом выходы блока управления частотой соединены с входами генератора переменной частоты. .

Источники информации, принятые во внимание при экспертизе

1. Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия-, 1970, с. 325, рис. 7-66 (прототип ).

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012131C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для измерения отношения двух напряжений | 1981 |

|

SU1026068A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1977 |

|

SU739736A1 |

| Устройство для измерения координат центра тяжести изображения объекта | 1988 |

|

SU1660208A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| Измеритель среднеквадратического значения напряжения одиночного импульса случайной формы и длительности | 1987 |

|

SU1429054A1 |

| Цифровой фазометр | 1985 |

|

SU1308935A1 |

| Устройство для определения отношения и логарифма отношения двух частот | 1980 |

|

SU901932A1 |

Авторы

Даты

1983-02-28—Публикация

1981-06-10—Подача