1

Изобретение относится к вычислительной технике и может быть использовано для построения пересчетных схем с дробным коэффициентом пересчета.

Пересчетные схемы позволят реализовать коэффициенты пересчета К, являщиеся целыми числами. Во многих практических задачах, однако, возникает необходимость в таком преобразовании частот следования импульсов, которое приводит к дробному коэффициенту пересчета. Выполнить такое преобразование с помощью известных пересче-гаых схем не представляется возможным.

Цель изобретения - расширение области применения пересчетных схем за счет возможности реализации всех возможных коэффициентов пересчета, а не только тех, которые выражаются целыми числами.

Предлагаемое устройство позволяет реализовать любой дробный коэффициент нересчета с ошибкой положения выходных импульсов во времени по отношению к импульсам требуемой выходной последовательпости, не превосходящей половины периода входной частоты.

Для этого предлагается с помощью пересчетной схемы, дискретных и логических схем из входной последовательности импульсов на выход устройства пропускать только те, которые наиболее близко отстоят от импульсов требуемой выходной последовательности.

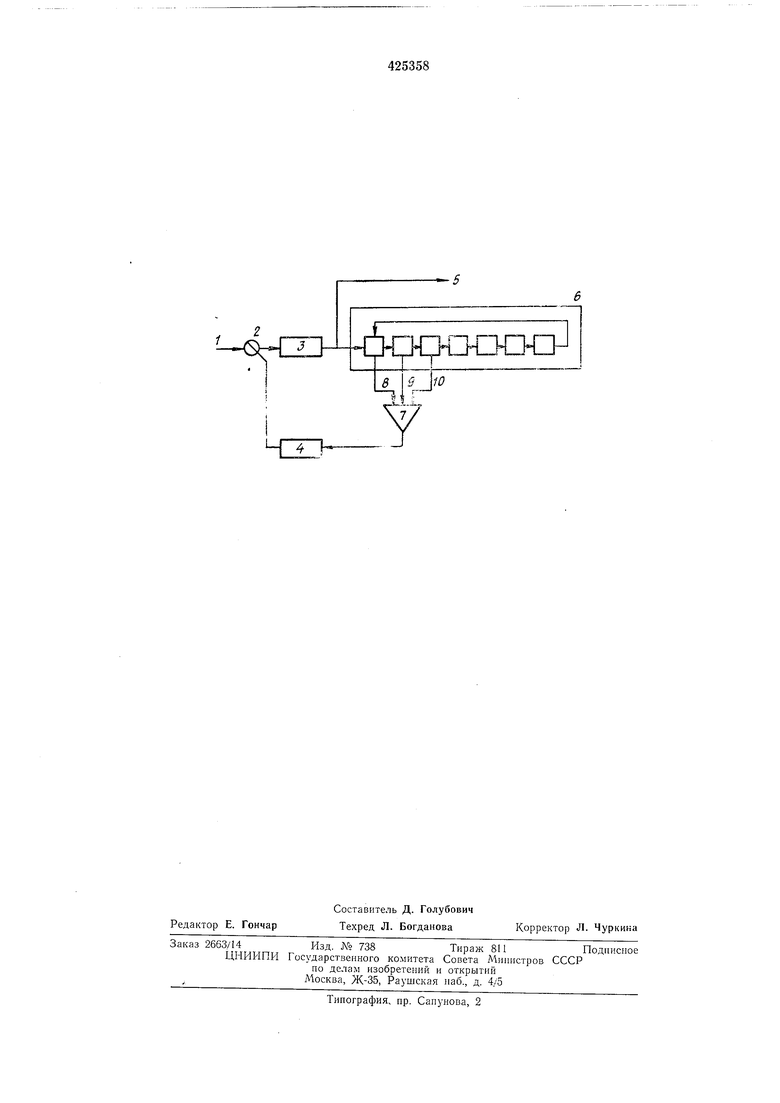

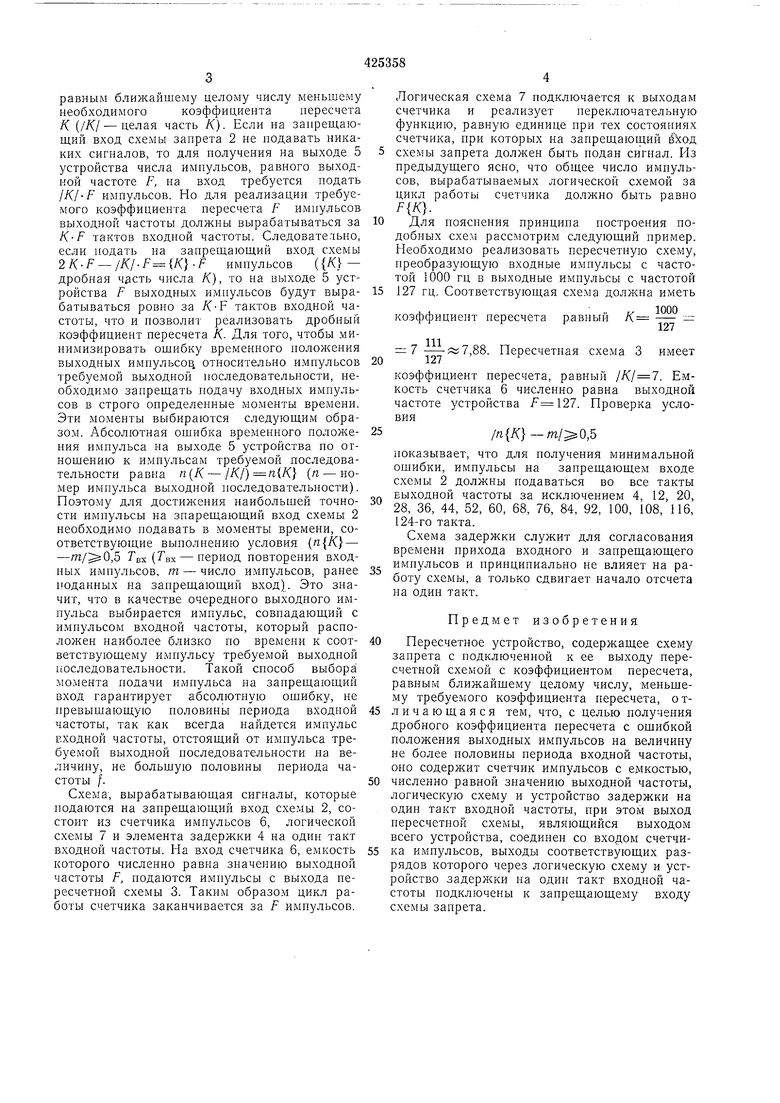

На чертеже приведен пример реализации пересчетной схелгы для ,88.

Предлагаемая пересчетная схема имее-i: 1 -вход импульсов 1000 гц; 2 - схему запрета; 3 - пересчетную схему с 4 - задерукку на 1 такт входно частоты; 5 - выход импульсов 127 гц; 6 - счетчнк импульсов до 127; 7 - схе.ма 8 - прямой выход первого разряда счетчика; 9 - прямой выход второго счетчика; 10 - инвертированный выход третьего разряда счетчика.

Псресчетпая схема с дробным коэффициентом пересчета образована схемой запрета 2, подключенной ко входу пересчетной схемы с коэффициентом нересчета (К), равным ближайп1ему целолгу числу, мсньн1ему требуемого 1;оэффицнента нересчета /( (//С/ - целая часть Л ), выход пересчетпой схемы 3 подается на счетчик импульсов 6 и одновременно елужит выходом всего устройства, определенные разряды 8, 9, 10 счетчика импульсов 6 через логическую схему 7 и схему задержки 4 подключены к запрещающему входу схемы запрета 2. Оеповггой вход схемы запрета 2 является входом устройства.

Работа устройства происходит следующим образом.

Импульсы входной частоты / подаются на вход 1 и через схему запрета 2 на пересчетную схему 3 с коэффициентом нересчета (К},

равным ближайшему целому числу меньшему необходимого коэффициента цересчета /С (//С/ -целая часть /С). Если на занрещающий вход схемы запрета 2 не нодавать никаких сигналов, то для получения на выходе 5 устройства числа импульсов, равного выходной частоте F, на вход требуется подать IKI-F импульсов. Но для реализации требуемого коэффициента пересчета F импульсов выходной частоты должны вырабатываться за K-F тактов входной частоты. Следовательно, если подать на запрещающий вход схемы 2/.f- //С/.f {/(}.f импульсов ({К.}- дробная чдсть числа /С), то на выходе 5 устройства F выходных имнульсов будут вырабатываться ровно за /CF тактов входной частоты, что и позволит реализовать дробный коэффициент цересчета /С. Для того, чтобы минимизировать ошибку временного положения выходных имнульсоц относительно импульсов требуемой выходной последовательности, необходимо запрещать подачу входных импульсов в строго определенные моменты времени. Эти моменты выбираются следующим образом. Абсолютная ошибка временного положения импульса на выходе 5 устройства по отношению к импульсам требуемой последовательности равна п()п{К} (я - номер импульса выходной последовательности). Поэтому для достижения наибольшей точности импульсы на зпарещающий вход схемы 2 необходимо нодавать в моменты времени, соответствующие выполнению условия («{/С} - ,5 ГЕХ (вх - период повторения входных имнульсов, т - число импульсов, ранее поданных на занрещающий вход). Это значит, что в качестве очередного выходного импульса выбирается импульс, совпадающий с импульсом входной частоты, который расположен наиболее близко по времени к соответствующему импульсу требуемой выходной последовательности. Такой снособ выбора момента нодачи имнульса на запрещающий вход гарантирует абсолютную ошибку, не нревышающую ноловины периода входной частоты, так как всегда найдется импульс входной частоты, отстоящий от импульса требуемой выходной носледовательности на величину, не большую ноловины периода частоты {.

Схема, вырабатывающая сигналы, которые подаются на запрещающий вход схемы 2, состоит из счетчика импульсов 6, логической схемы 7 и элемента задерлши 4 на один такт входной частоты. На вход счетчика 6, емкость которого численно равна значению выходной частоты F, нодаются имнульсы с выхода пересчетной схемы 3. Таким образом цикл работы счетчика заканчивается за F импульсов.

Логическая схема 7 подключается к выходам счетчика и реализует нереключательную функцию, равную единице нри тех состояниях счетчика, при которых на запрещающий йход 5 схемы запрета должен быть подан сигнал. Из предыдущего ясно, что общее число импульсов, вырабатываемых логической схемой за цикл работы счетчика должно быть равно f{K}.

0 Для пояснения принципа ностроения подобных схем рассмотрим следующий нример. Необходимо реализовать пересчетную схему, преобразующую входные импульсы с частотой 1000 ГЦ в выходные импульсы с частотой

5 127 ГЦ. Соответствующая схема должна иметь

J л, г 1000 коэффициент пересчета равнын л -:

л. I

- 7 «7,88. Пересчетная схема 3 имеет

коэффициент цересчета, равный . Емкость счетчика 6 численно равна выходной частоте устройства . Проверка условия

5/я {/С}-/п,/ 0,5

показывает, что для получения минимальной ошибки, импульсы на запрещающем входе схемы 2 должны подаваться во все такты

„ выходной частоты за исключением 4, 12, 20, 28, 36, 44, 52, 60, 68, 76, 84, 92, 100, 108, 116, 124-го такта.

Схема задержки служит для согласования времени прихода входного и запрещающего

импульсов и принципиально не влияет на работу схемы, а только сдвигает начало отсчета на один такт.

Предмет изобретения

0 Пересчетное устройство, содержащее схему занрета с подключенной к ее выходу пересчетной схемой с коэффициентом пересчета, равным ближайщему целому числу, меньшему требуемого коэффициента пересчета, от5 л и чающаяся тем, что, с целью получения дробного коэффициента цересчета с ошибкой положения выходных импульсов на величину не более ноловины периода входной частоты, оно содержит счетчик импульсов с емкостью,

0 численно равной значению выходной частоты, логическую схему и устройство задержки на один такт входной частоты, при этом выход пересчетной схемы, являющийся выходом всего устройства, соединен со входом счетчика импульсов, выходы соответствующих разрядов которого через логическую схему и устройство задерл ки на один такт входной частоты подключены к запрещающему входу схемы запрета.

О

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ИЛ\ПУЛЬСОВ | 1971 |

|

SU305575A1 |

| ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU275518A1 |

| Измеритель временных интервалов | 1987 |

|

SU1597859A2 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ символов, НАПЕЧАТАННЫХ МАГНИТНОЙ КРАСКОЙ СТИЛИЗОВАННЫМ ШТРИХОВЫМШРИФТОМ | 1970 |

|

SU271923A1 |

| Многоканальный преобразователь частоты в код | 1975 |

|

SU598237A1 |

| Многоканальный преобразователь частоты в код | 1978 |

|

SU712953A1 |

| Устройство стабилизации средней частоты шумовых выбросов над пороговым уровнем | 1974 |

|

SU484648A1 |

| Делитель частоты следования импульсов | 1976 |

|

SU656216A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОЙ ОЦЕНКИ СОСТОЯНИЯ | 1972 |

|

SU326104A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341165A1 |

Даты

1974-04-25—Публикация

1972-01-03—Подача