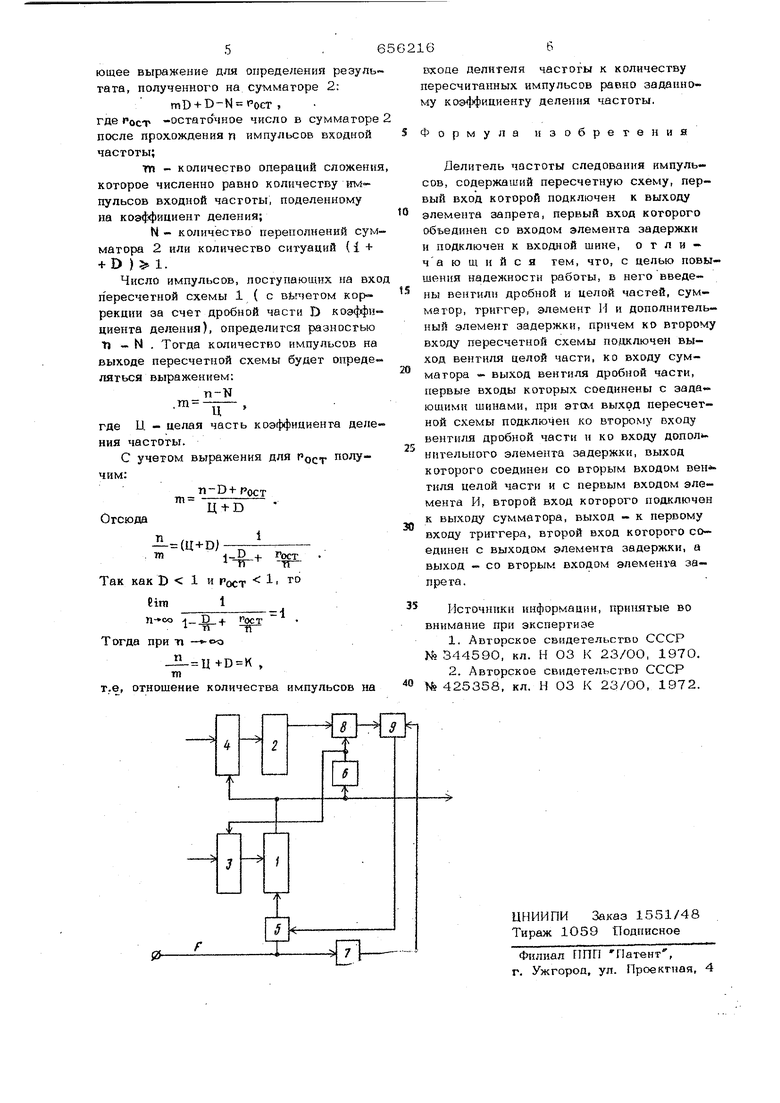

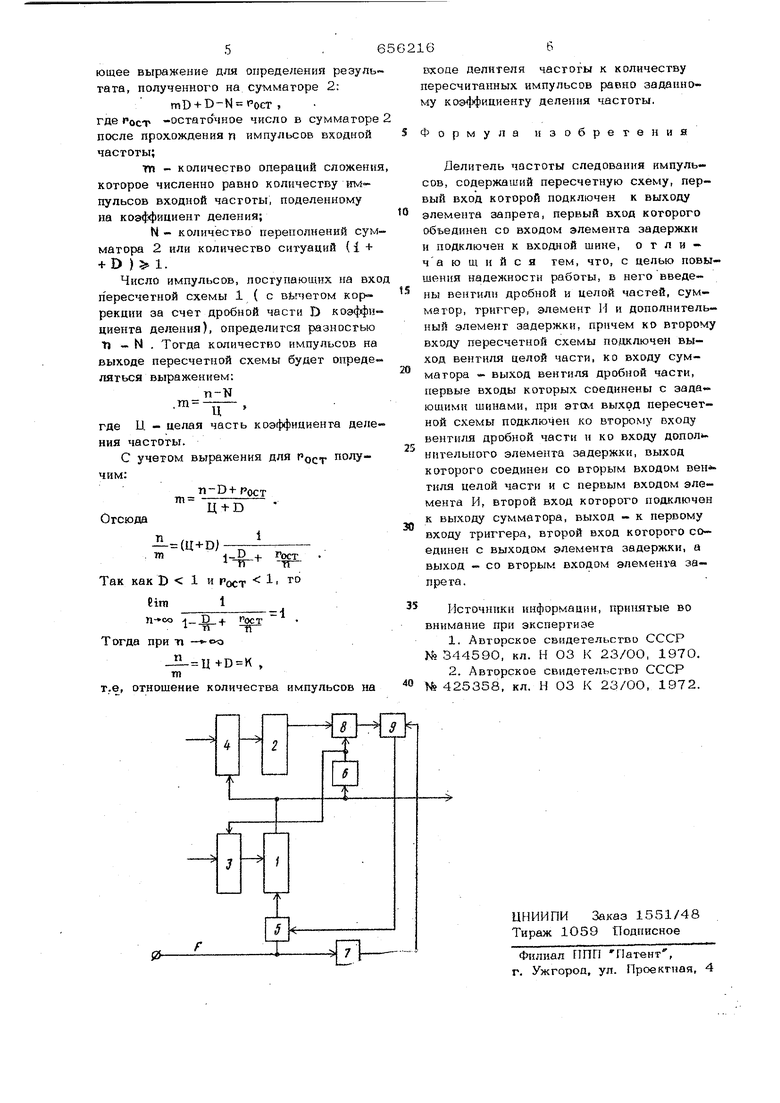

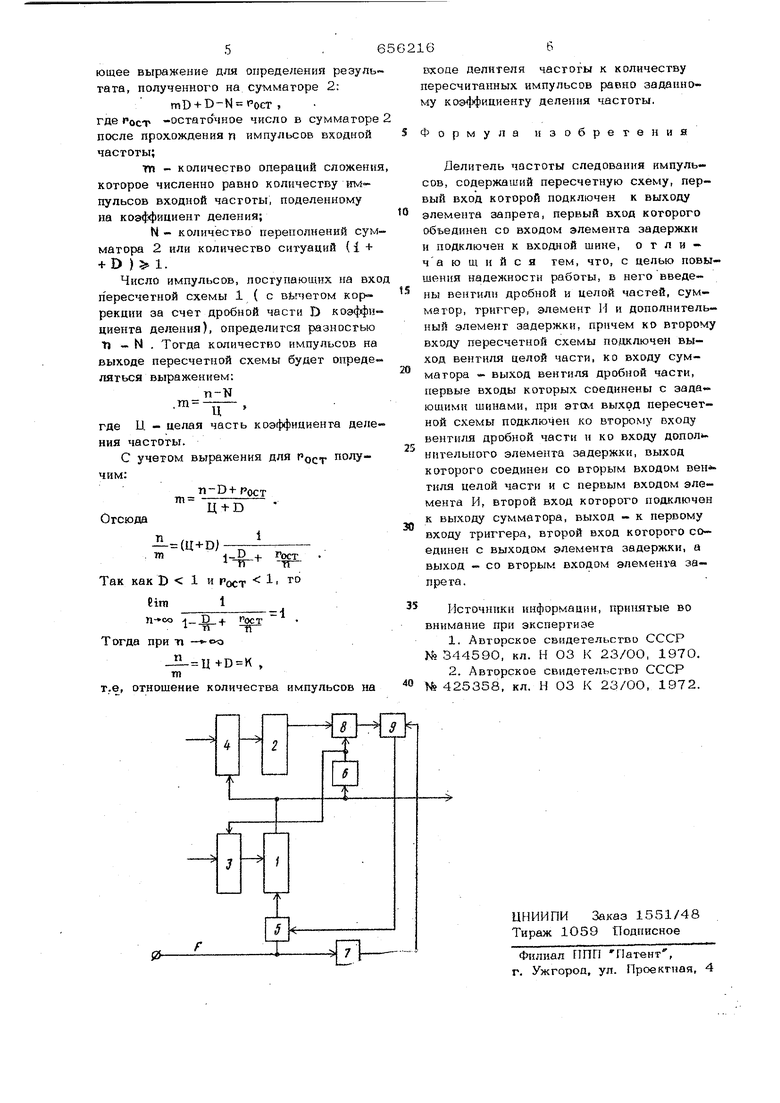

(54) ДЕЛИТЕЛЬ ЧАСТОТЫ СЛЕДОВАНИЯ ИМПУЛЬСОВ 3 чен выход вентиля целой части, к входу сумматора выход вентиля дробной части, первые входы которых соединены с задающими шинами. Выход пересчетной схемы подключен ко второму входу вентиля дробной части и входу дополнительного элеменг-а задержки, выход которого соединен со вторым входом вентиля целой части и с первым входом элемента И. Второй вход элемента И подключен к выходу сумматора, выход - к первому входу триггера, второй вход которого со единен с выходом элемента задержки, а выход со вторым входом элемента запрета. На чертеже представлена структурная схема делителя частоты следования им,пульсов. Делитель частоты следования импуль сов содержит пересчетную схему 1, сум матор 2 {накапливающий), вентили 3, 4 целой и дробной частей дробного коэффициента деления, элемент запрета 5, элементы задержки 6 и 7, элемент И 8, триггер 9. Элемент запрета 5 выполняет логичес кую функцию И и предназначен для коррекции частоты, поделенной на целую часть коэффициента деления с учетом его дробной части. Коррекция производится путем запрета на прохождение одиночного импульса входной частоты на вход пересчетной схемы 1. Пересчетная схема 1 предназначена для деления частоты следования входных импульсов на целую часть коэффициента деления. Элемент задержки 6 служит для задержки импульсов поделенной частоты на время суммирования в сумматоре 2. Вентили 3, 4 предназначены для подклю чения входных шин к пересчетной схеме 1 и сумматору 2 соответственно в целях записи на эти схемы целой и дробной частей коэффициента деления частоты. Сумматор 2 производит умножение дробной части коэффициента деления частоты последовательно на 1, 2, З,... путем выпoJшeния операции сложения. Элемент И 8 предназначен для опроса результата переполнения сумматора 2, триггер 9 - для хранения результата пере пол11ения сумматора 2 и управления элементом запрета 5. Элемент задержки 7 выполняет задержку импульсов входной частоты, по которым возвращается в исходное состояние триггер 9, на время 16 действия импульса на входе элемента запрета 5. Делитель частоты работает следующим образом. В исходном состоянии элемент запре та 5 открыт и импульсы входной частоты F подаются на пересчетную схему 1. Элементом запрета 5 управляет триггер 9. В пересчетной схеме 1 производится деление частоты на целую часть коэффициента деления частоты, который поступает на схему 1 через вентиль 3 по входным шинам из задающего устройства. Через вентиль 4 по импульсу с выхода схемы 1 на сумматор 2 по входным шинам с задающего устройства подается код дробной части коэффициента деления. На сумматоре 2 по каждому импульсу с выкода пересчетной схемы 1 производится сложение дробной части коэффициента деления с содержимым сумматора 2: D-tD - 2D; 2D-VD ЗТ);...-ID-vD (-r4l)D;.- niD-vD -(mt-f ID,- .После выполнения каждой операции сложенияiD + D {i + l)D с помощью элемента И 8 и элемента эвт. держки 6 анализируется результат (i + 1, (i + 1)D 1, полученный на сумматоре 2. Запоминание результата анализа производится с помощью триггера 9 на время действия следующего импульса входной частоты. Если (1 + l)U5s 1, то следующий импульс входной частоты не должен поступать на пересчетную схему 1. Для этого с триггера 9 подается запрещающий потенциал на элемент запрета 5, после чего триггер 9 возвращается в исходное состояние через элемент задержки 7 этим же импульсом. Для проведения последующих операций сложения на сумматоре 2 запоминается результат (i + l)D-l. Если (i + 1)D 1, т.е. переполнение сумматора 2 отсутствует, следующий импульс входной частоты поступает элемент запрета 5 на схему 1. В этом случае триггер 9 вырабатывает разрешающий потенциал, поступающий на элемент запрета 5. Данные операции производятся до тех пор, пока на сумматоре 2 не будет получен результат (1 + l)D 1. Таким образом, после пересчета количества импульсов входной частоты, численно равного п , можно записать следу

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты | 1976 |

|

SU683026A2 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1003352A1 |

| Делитель частоты | 1980 |

|

SU940314A1 |

| Пересчетное устройство | 1979 |

|

SU849468A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU725238A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

| Делитель частоты следования импульсов | 1988 |

|

SU1598174A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1037420A1 |

| Делитель частоты следования импульсов | 1985 |

|

SU1272501A1 |

Авторы

Даты

1979-04-05—Публикация

1976-10-04—Подача