Изобретение относится .к электронно-измерительной технике, шредназначе-но для пересчета импульсов с индикацией состоялий устройства и ,может |быть испОЛьзоеаио, в частности, IB эле1Ктро1Н|НОС1чет|Ных частотомерах.

Известны ра-зличные пересчетйые устройстгва inoiBbiim eiHHOiro быстр.одбЙ|СТ|Вия. Все он.и характеризуются общим Признаком - повышение -частоты .пересчета AocTHiraeTCH путем MiHoroiKpaTHOiro деления частоты дво-ичньгми янейками, не охваченными обратными связями, с последующим восстановлением коэффициента деления на 10.

iB таких у|стройст1вах невозможно обеспечить индикацию в режиме -непрерывного сэдта. Это вызвано тем, что лишь при налич ии }1М пулЬ|Са переноса, 1ПОСту пающе.го по окончании й-ремеии счета на дешифратор, устройство фунюционирует как десятичное пересчетное. Режи1М ж-е непрерывного счета характерен отсутствием импульсо1В «переноса, так как этот .режим .реализуется без 1воздейст1вия устройств автоматики (схем переноса), т. е. при отсутствии каких-либо времен счета, и соответствует, например, подаче на вход устройства бесконечной во времени произвольной последовательности импульсов.

чивающие .нор.мальное функционирование устройства.

И, наконец, реализация десяти Ч1НО Го пересчетного устройства (невозможна при ,

т. е. деление входной частоты может осуществляться не более, чем тремя последовательно соединеннЫ|Ми дво-ичными ячейками.

Цель изобретения - увеличение коэффициента деления входиого делителя и обеспечение индикации состояний устройства в режиме непрерывного |Счета.

Это достигается тем, что один из выходо:в делителя с козффициенто1М деления 2 соединен с входами делителя с коэффициентом деления 5 и схемы «Запрет, запрещающий вход которой подключен « соответствующим ячейка-м делителя с коэффициентом деления 5, а выход -к одному из входов схемы «ИЛИ, соединенной другими входалт с остальными выходами делителя с коэффнциенTOiM деления 2«, а выходом - с входом делителя с коэффициентом деления 2. Выход делителя с коэффициентом деления 2, а также ВЫХОД дешифратора, IK которому подключены

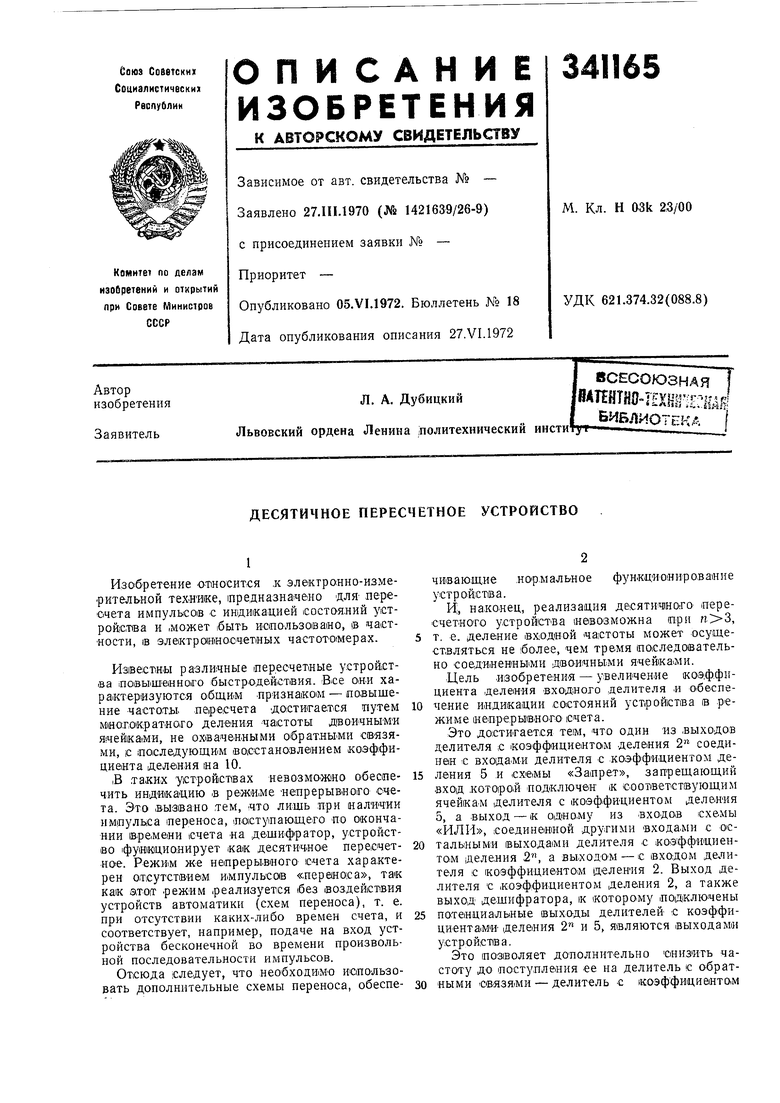

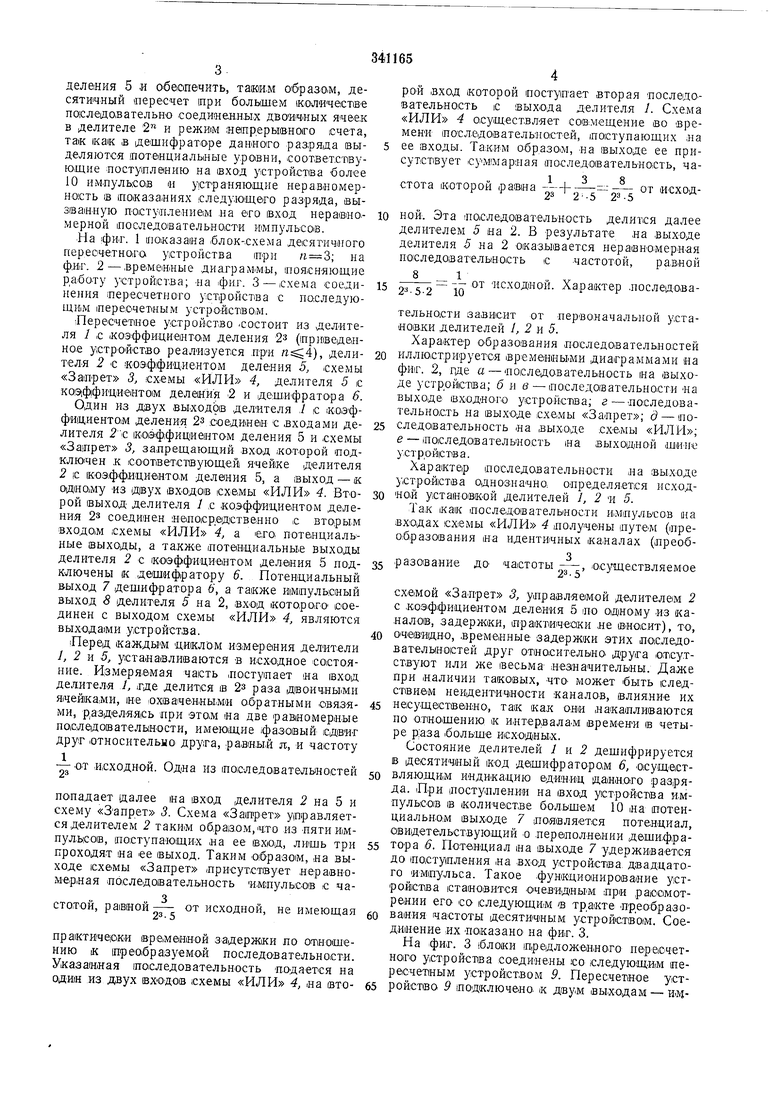

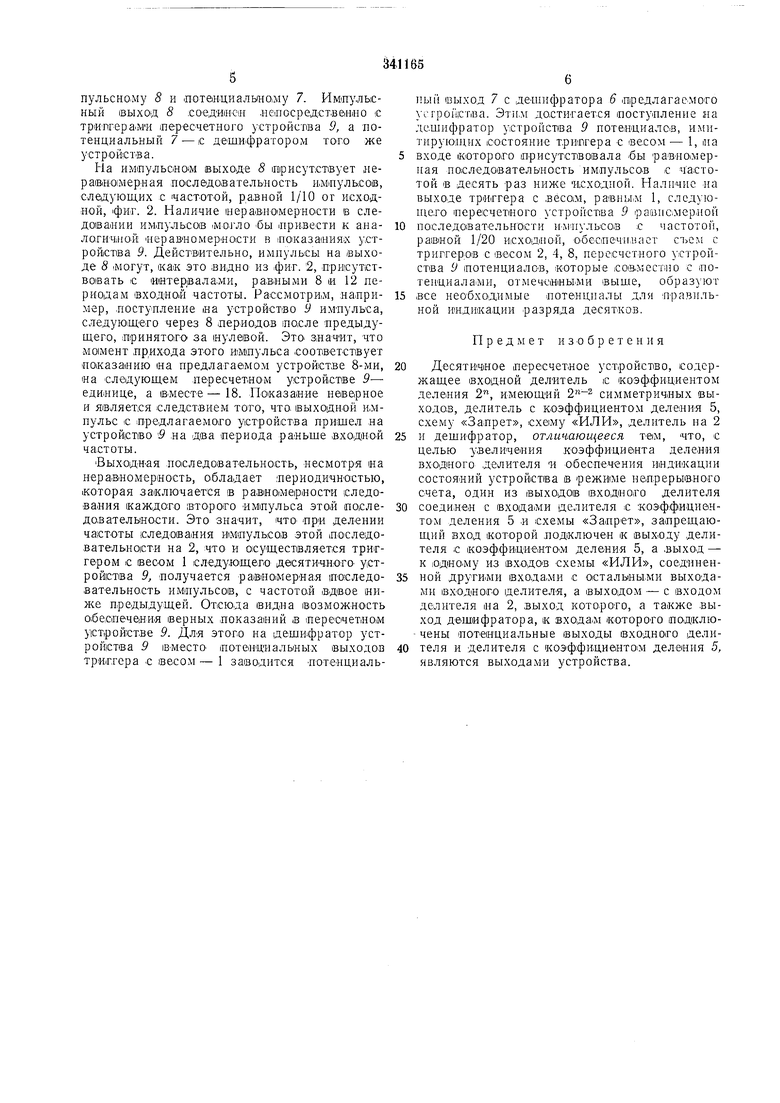

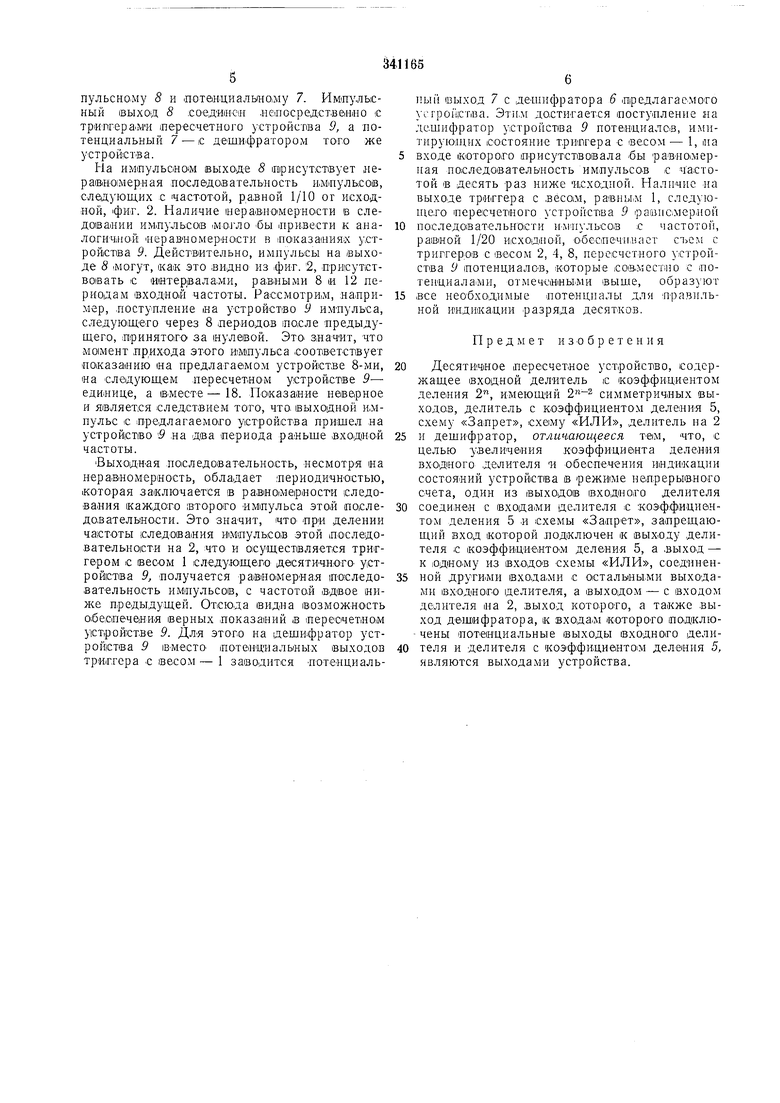

потенциальные выходы делителей с коэффициентами деления 2 и 5, являются выходами устройст1ва. деления 5 и Обеопечить, таким образом, десятичный оересчет 1при большем количестШе посл едовательнО соединенных двоИЧНых ячеек в делителе 2 и режим яетрерывного счета, так как в дешифраторе данного разряда выделяются шотанциальные уровни, соответствующие поступлению на вход устройства более 10 и.млульсоа и устраняющие неравномерность IB иоказаииях следующего разряда, вызваиную ПОСтуаглениам .на его вход неравно;мерной ооследовательности импульсов. На 1фИГ. 1 1по.каза1на блок-схема десягичиого переочетнога устройства ери на фйг. 2-зреметные диаграммы, поясняющие работу устройства; «а фиг. 3 - схема соедине 1ня шересчетного устро-йства с последуюЩИ|М 1переочет1ным устрО:йствО|М. Пересчетиое устройство -состоит из делителя 1 с коэффициентом деления 2з (|нриведе,нно,е yiCTpowcTBO реали1зуется лри ), делителя 2 € коэффициентом деления 5, схемы «Затрет 3, схемы «ИЛИ 4, делителя 5 с ко Э1ффиЦ|ие1Нто1М деления 2 и дешифратора 6. Один из двух вы-ходов делителя 1 с коэффициентом леления 2з соединен с входами делителя 2с коэффициентом деления 5 и схемы «Затрет 3, залрещающий вход /которой подключен к соответствующей ячейке делителя 2 С коэффициентом деления 5, а (ВЫход - к одному из двух входов схемы «ИЛИ 4. Второй выход делителя / с коэффициентом деления 23 со-единен непосредственно с вторым входом схемы «ИЛИ 4, а eroi поте,нциаль ные выходы, а также потенциальные выходы делителя 2 с коэффициентом делания 5 нодключены к дешифратору 6. Потенциальный выход 7 дешифратора 6, а также импульсный выход 8 делителя 5 на 2, вход которого соединен с выходом схемы «ИЛИ 4, являются выходами устройства. |Перед каждым циклом измерения делители 1, 2 н 5, устанавливаются в исходное состояние. Измеряемая часть (Поступает на вход делителя 1, аде делится в 2з раза двоичными ячейками, не охваченными обратными связями, разделяясь при этом на две равномериые пасле|Довательности, имеющие фазовый сдвиг друг относительно друга, равный я, и частоту 1 г -от ИСХОДНОЙ. Одна из лоследователыностеи попадает далее на вход делителя 2 на 5 н схему «Запрет 3. Схема «Запрет урравляется делителем 2 таким обрааом,что из лятиимпулысов, поступающих на ее вход, лишь три проходят на ее выход. Таким о бразом, на выходе схемы «Запрет /присутствует неравномерная 1последовательность им)пуль;с.ов с ча3стотои, равной от исходной, не имеющая рой вход которой постуоает вторая последовательность с выхода делителя А Схема «ИЛИ 4 осуществляет со1В1М.ещение во времени последовательностей, поступающих ,иа ее входы. Таким о:бразо1М, на выходе ее присутствует суМ1мар;ная |последовательно1сть, ча1,3 8 стота которой равна исход О . О ной. Эта последовательность делится далее делителем 5 на 2. В результате на выходе делителя 5 на 2 оказывается неравно мер-н-ая иоследовательность с частотой, равной 81„V -;- - ОТ ИСХОДНОЙ. Характер .последова О 1Wi) тельности зависит от первоначальной установки делителей 1, 2 н 5. Характер образования последовательностей иллюстрируется времениы.ми диаграммами на фиг. 2, где а - последовательность на выходе устройства; б и в - ооследовательности на выходе входного устройства; г-последовательность на выходе схемы «За/прет ; д - последовательность на .выходе схемы е - последовательность на выхо1д.ной .шине устройства. Характер последовательности на (выходе у.стр0:й|ства однозначно: определяется исходНОЙ установкой делителей 1, 2 и 5. Так как последовательности нмпульсов на вхо.дах схемы «ИЛИ 4 получены путем (преобразования на идентичных каналах (преобразованне до ча1стоты -, осуществляемое схе|Мой «Запрет 3, у.правляемой делителем 2 с коэффициентом деления 5 по одному из каналов, задержки, практичеоки не вносит), то, очевидно, временные задержки этих последовательностей друг относительно друга .отсутствуют или же весьма незначительны. Даже при .наличии таковых, что- может быть следствием неидентичности каналов, влияние их несущественно, так как они .накапливаются по отнощению к интервалам времени в четыре р;аза .болыше исходных. Состояние делителей 1 н 2 дешифрируется в десятичный код дешифраторо.м 6, осуществляющи.м индикацию единиц данного разряда. При поступлении на шход у1стройст1ва нмпульсо1в в количестве большем 10 на потенциальном выходе 7 по.является потенциал, свидетельствующий о переполнении дешифратора 6. Потенциал на выходе 7 удерживается до поступления .на вход устройства, двадцатого имиульса. Такое функционирова/ние устройст1ва стано/вится очевидны-м при рас.смотрении его со следующим /в тракте пр,еобразования частоты десятичным устройством. Соединение их локазаио на фиг. 3.

пульснаму 8 и (Потан.циальиО|Му 7. Им пульсный 1ВЫХОД 8 .сОедИНсн .напосредст.вбнио с трипгера Ми тересчетного устройства 9, а потенциальный 7 - с дешифратором того же устройства.

На имшульоноМ выходе 8 трисутствует лера1Вйа1мерная :Последо,вательНость нмшульсов, сле|Дую1цих с частотой, равной 1/10 ог исходной, 1фИ|Г. 2. Наличие 1нерав.ио 1ерности в следовании импульсов бы (Привести к аналогичной неравномерности в локазаииях устрой(СТ1ва 9. Действительно, импульсы на выходе 8 Аюгут, как это видно из .фиг. 2, присутствовать с иетедвала.ми, равными 8 и 12 периодам входной частоты. РассмотрИ|М, далример, лоступление «а устройство 9 импульса, следующего через 8 периодов шосле предыдущего, принятого за нулевой. ЭтО значит, что мо1мент прихода этого вмпульса соответствует показанию на предлагаемом устройстве 8-ми, «а следующем пересчетном устройстве 9- единице, а в-месте-18. Показание неверное и является следствием того, чтО: выходной ил1пульс 1C предлагаемого устройства пришел на устройство 5 на два периода раньше входной частоты.

Выход:Н-ая последовательность, несмотря на неравномерность, обладает .периодичностью, .которая заключается в равно|Мерносри следования каждого второго «млульса этой последователыности. Это значит, что при делении частоты следования И1мстульсов этой лоследовательно сти на 2, что и осуществляется триггером ic весом 1 следующего десятичного yiCTройства 9, получается равно1мерна.я тоследовательность имнульсов, с частотой ВДвое ниж& преДыдущей. Отсюда видна Возможность Oi6ecine4eiHHfl верных показаний в лересчетно;М устройстве 9. ДлЯ этого на дешифратор устройства 9 iBMecTo лотенциальных выходов триггера с весом - 1 заводится Нотенциальпый выход 7 с дешифратора 6 Л редлагаСМого ycrpoiliCTiBa. Этил достигается поступление на дешифратор устройства 9 потенциалов, имитирующих СОстояние тритгера с весом- 1, на

входе которого присутствовала бы раВИО|Мерная последовательность импульсов с частотой в десять раз ииже исходной. Наличие на выходе трнггера с весам, равныд 1, следующего пересчетного устройства 9 |ра1вномерной

последовательности ИМнульсов с частотой, равной 1/20 исходной, ОбеСлеЧивает съем с триггеров с iBecoM 2, 4, 8, пересчетного устройства 9 потенциалов, которые сов местяш с потенЦиалаМи, отмеченными выше, образуют

все необходимые потеНцлалы для Правильной индикации разряда десятков.

Предмет и з О б р е т е н и я

Десятичное пересчетное устройство, содержащее входной делитель с коэффициентом деления 2, имеющий 2 симметричных выходов, делитель с коэффициентом деления 5, схему «Запрет, cxeiMy «ИЛИ, делитель на 2

и дешифратор, отличающееся там, что, с целью увеличения коэффициента деления входного делителя -и Обеспечения индикации состояний устройства в режиме непрерывного счета, один из выходов входного делителя

соединен с входами делителя с коЭффициантом деления 5 И схемы «Запрет, запрещающий ВХО.Д которой подключен к выходу делителя с коэффицИентОМ деления 5, а .выхОД - к |ОД1НОМу из входов схемы «ИЛИ, соединенной друтнми входа.ми с остальными выходами входного делителя, а выходом - с входом делителя на 2, выхОД которого, а также выход дешифратора, к входад которого подключены потенциальные выходы входного делителя и делителя с коэффициенто деления 5, являются выходами устройства.

(-

-1 N

L.J

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU241127A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341166A1 |

| ВИБЛИОТЕКД J | 1971 |

|

SU299030A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU233308A1 |

| Цифровое устройство измерения времени | 1977 |

|

SU672606A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1980 |

|

SU900460A1 |

| Устройство измерения времени с цифровой индикацией | 1975 |

|

SU526850A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНО-ШЕСТИДЕСЯТИРИЧНЫЙ КОД | 1967 |

|

SU190054A1 |

| ЭЛЕКТРОННОСЧЕТНЫЙ ЧАСТОТОМЕР | 1972 |

|

SU340979A1 |

1штшт111ШЖ1тжи1Жшттш111 Ж1 ™1Ж Т Ш1

g p p-py--j--pj-j-y-j--y-j--|--py

g .,.-.. p-f-n 1 f-I j------|--p ---p

r ТТ ТГТТГТТТПТТТТПТТЛТ

e

Даты

1972-01-01—Публикация