в

а

о о ел

CJ

о

снег на экране ВКУ 9, 20, 21 и ЦВКУ 10. Видеопроцессор 7 позволяет более детально просматривать явркостные участки изображения в позитивном и негативном виде, а также просматривать графические изображения в различных режимах. Блок 18 формирования курсора позволяет на экране ВКУ формировать рамку с оперативным раздельным изменением ее сторон или курсор (крестик или какой-либо символ), которые

могут перемещаться по всему полю изображения. Управление функционированием блока 18 формирования курсора возможно либо от ЭВМ, либо от манипулятора Мышь 19. Оперативное формирование рамки или курсора на экране ВКУ упрощает процесс программирования, а следовательно, сокращает время обработки изображений. 5 з.п. ф-лы, 8 ил., 3 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Станция локальной сети | 1987 |

|

SU1478221A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1352477A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для обработки и отображения видеоинформации | 1988 |

|

SU1748284A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| Устройство для селекции изображений объектов | 1988 |

|

SU1583949A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для отображения многоугольников на экране растрового графического видеоконтрольного блока | 1987 |

|

SU1534454A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

Изобретение относится к вычислительной технике и может быть использовано для ввода цветных и черно-белых полутоновых изображений в ЭВМ и отображения данных. Цель изобретения - расширение области применения за счет ввода в ЭВМ цветных полутоновых изображений и отображения цветной графической информации, повышение точности отображения за счет снижения помех при обмене с ЭВМ и повышение производительности обработки изображений. Блок 16 фильтров совместно с блоком 17 амплитудной коррекции позволяют снизить неоднородность белого цвета внешнего освещения объекта исследования при вводе его изображения в блоки 12 - 14 памяти по меткам, формируемым на черно-белых видеоконтрольных устройствах (ВКУ) 9, 20, 21. Блок 15 памяти используется для вывода графической информации, поступающей из ЭВМ, на цветное видеоконтрольное устройство (ЦВКУ) 10. Конструкция блоков 12 - 15 позволяет производить обмен информацией между ЭВМ и системой без помех типа "снег" на экране ВКУ 9, 20, 21 и ЦВКУ 10. Видеопроцессор 7 позволяет более детально просматривать яркостные участки изображения в позитивном и негативном виде, а также просматривать графические изображения в различных режимах. Блок 18 формирования курсора позволяет на экране ВКУ формировать рамку с оперативным раздельным изменением ее сторон или курсор (крестик или какой-либо символ), которые могут перемещаться по всему полю изображения. Управление функционированием блока 18 формирования курсора возможно либо от ЭВМ, либо от манипулятора "мышь" 19. Оперативное формирование рамки или курсора на экране ВКУ упрощает процесс программирования, а следовательно, сокращает время обработки изображений. 5 з.п.ф-лы, 8 ил., 3 табл.

Изобретение относится к вычислительной технике и может быть использовано для ввода цветных и черно-белых полутоновых изображений в ЭВМ и отображения данных.

Целью изобретения является расширение области применения за счет ввода в ЭВМ цветных полутоновых изображений и отображения цветной графической информации, повышение точности отображения за счет снижения помех при обмене с ЭВМ и повышение производительности обработки изображений,

На фиг.1 приведена структурная схема системы; на фиг.2-8 - функциональные схемы блока памяти, блока амплитудной коррекции, блока формирования курсора, манипулятора Мышь, видеопроцессора, блока общей синхронизации и блока управления памятью соответственно.

Система (фиг.1) содержит интерфейсный блок 1, блок 2 регистров, формирователь 3 адреса, блок А общей синхронизации, блок 5 аналого-цифрового преобразования, телекамеру 6 черно-белую, видеопроцессор 7, блок 8 цифроаналогового преобразования, черно-белое видеоконтрольное устройство (ВКУ) 9, цветное видеоконтрольное устройство (ЦВКУ) 10, блок 11 управления памятью, блоки 12-15 памяти, блок 16 фильтров, блок 17 амплитудной коррекции, блок 18 формирования курсора, манипулятор Мышь 19, черно-белые ВКУ 20 и 21, группы входов 22 и выходов 23 связи с ЭВМ, группы информационных входов 24 и выходов 25 и группы управляюще-тактирующих входов 26 и выходов 27 интерфейсного блока 1, группу адресных выходов 28 блока 2, синхронизирующий вход 29 и группу синхронизирующих выходов 30 блока 5. выход 31 первого полного телевизионного сигнала (ПТС), группу 32 механических управляющих выходов блока 16, выход 33 ПТС телекамеры 6, выход 34 скорректированного ТПС блока 17, группу 35 адресных входов

блока 17, первую группу 36 адресных выходов формирователя 3, первую группу 37 син- хронзирующих выходов, первую 38 и вторую 39 группы управляющих выходов и

вторую группу 40 синхронизирующих выходов блока 11, вторую группу 41 адресных выходов формирователя 3, вторую 42 и . третью 43 группы информационных выходов и первую группу 44 управляющих выходов блока 2, первую группу 45 синхронизирующих выходов блока 4, выход 46 сигнала включения телеввода и вторую группу 47 управляющих выходов блока 2, выход 48 линии передачи курсора и вход 49

выбора режима блока 18, вторую 50, третью 51, четвертую 52 и пятую 53 группы информационных входов блока 2, первую 54, вторую 55, третью 56 и четвертую 57 группы информационных выходов и первую 58, вторую 59 и третью 60 группы информационных выходов блока 7, вторую группу 61 синхронизирующих выходов и выход 62 строба телеввода блока 4, выход 63 тактирующего сигнала блока 11, четвертую 64 и

пятую 65 группы информационных выходов блока 2, группу 66 информационных выходов блока 5, группу 67 управляющих выходов и группу 68 информационных выходов блока 17, группу 69 информационно-сйнхронизирующих выходов блока 8, группу 70 синхронизирующих выходов манипулятора Мышь 19, выход 71 второго ПТС и в ыход 72 третьего ПТС блока 8.

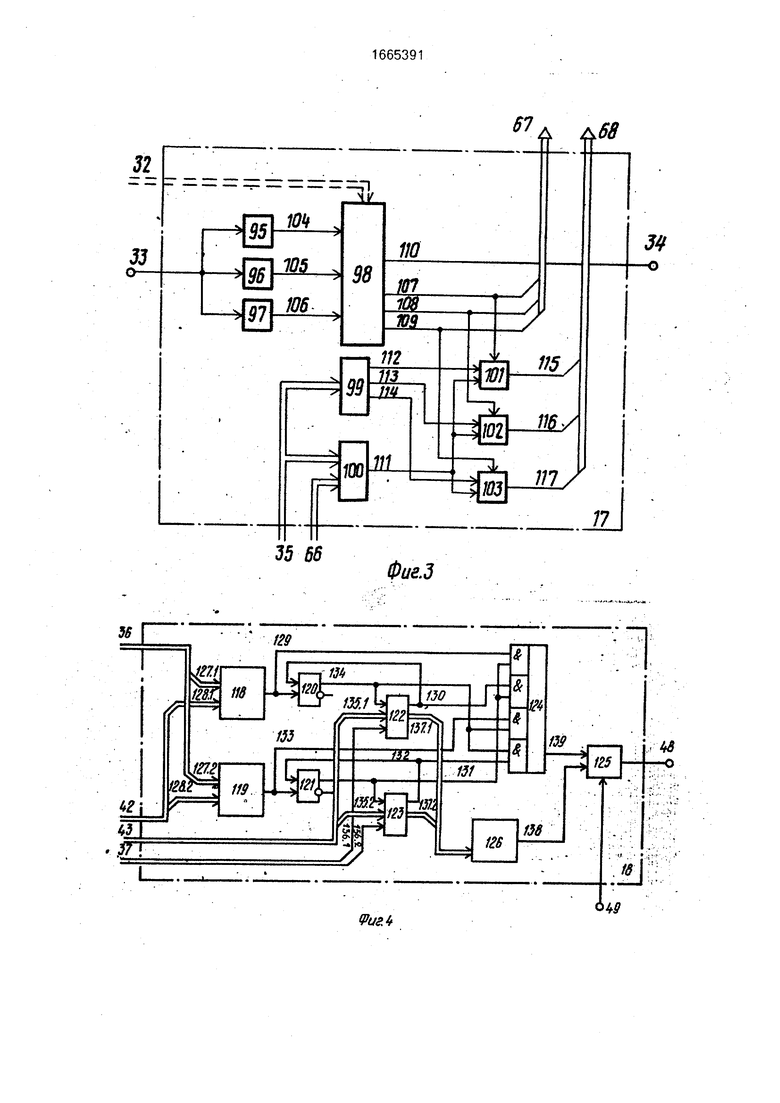

Каждый из четырех блоков 12-15 памяти (фиг.2) содержит первую 73 и вторую 74 группы входных двухразрядных регистров сдвига, первый 75 и второй 76 узлы видеопамяти, первую 77 и вторую 78 группы выходных двухразрядных регистров, первую

79 и вторую 80 группы селекторов-мультиплексоров, группу 81 информационных входов и группу 82 информационных выходов первого узла 75, группу 83 информационных выходов первой группы 77 выходных.реги5 строе, группу 84 информационных входов и

группу 85 информационных выходов второго узла 76, группу 86 информационных выходов второй группы 78 выходных регистров, группу 87 управляющих входов первой группы 79 селекторов-мультиплексоров, группу 88 управляющих входов второй группы 80 селекторов- мультиплексоров , группу 89 управляющих входов первого узла 75, группу 90 управляющих входов второго узла 76, синхронизирующий вход 91 первой группы 73 входных регистров, синхронизирующий вход 92 второй группы 74 входных регистров, синхронизирующий вход 93 первой группы 77 выходных регистров и синхронизирующий вход 94 второй группы 78 выходных регистров.

Блок 16 фильтров содержит красный, синий и зеленый светофильтры и механизм перестановки светофильтров перед объективом телекамеры 6.

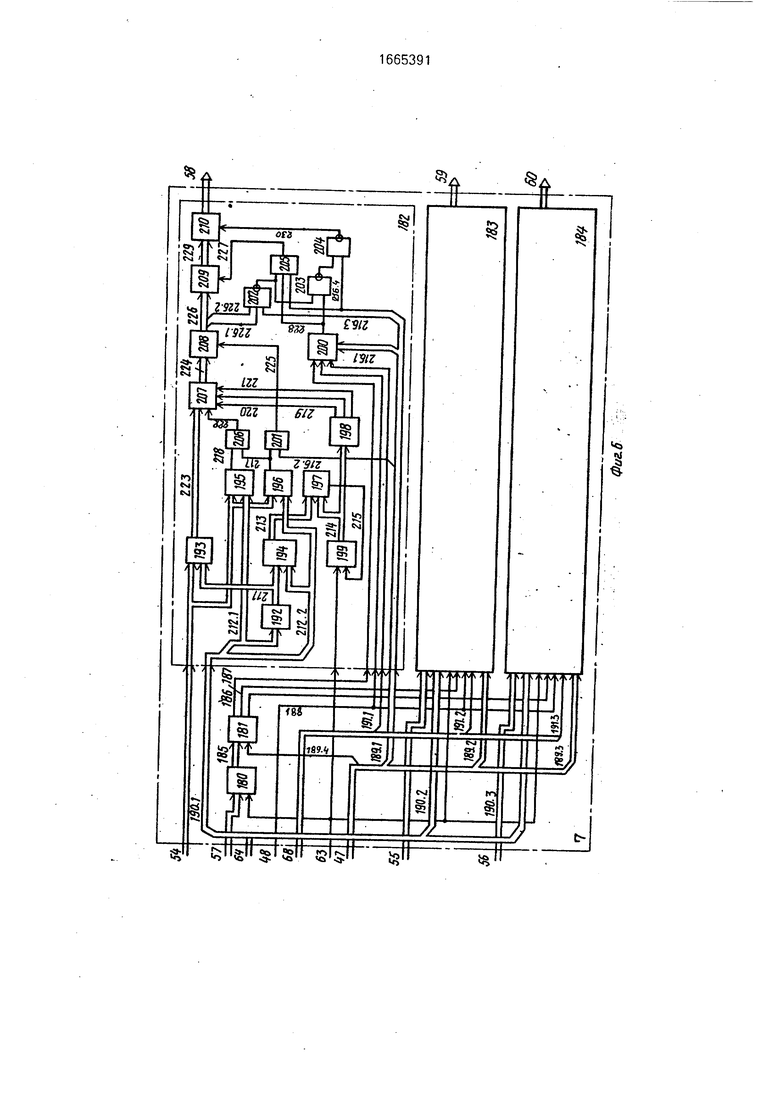

Блок 17 амплитудной коррекции (фиг.З) содержит первый 95, второй 96 и третий 97 усилители ПТС, переключатель-преобразователь 98. узел 99 памяти хранения меток, схему 100 сравнения, первый 101, второй 102 и третий 103 элементы ИЛИ со строби- рующими входами, первый 104, второй 105 и третий 106 информационные входы, первый 107, второй 108 и третий 109 управляющие выходы и информационный выход 110 переключателя-преобразователя 98, выход 111 схемы 100 сравнения, первый 112, второй 113 и третий 114 выходы узла 99 памяти хранения Меток и выходы 115, 116, 117 соответственно первого 101, второго 102 и третьего 103 элементов ИЛИ со стробирую- щими входами.

Блок 18 формирования курсора (фиг.4) содержит первую 118 и вторую 119 схемы сравнения, первый 120 и второй 121 триггеры, первый 122 и второй 123 двоичные счетчики, коммутатор 124, мультиплексор 125, узел 126 памяти хранения символа, первую

входов узла 126 памяти, первый 138 и второй 139 входы мультиплексора 125.

Манипулятор Мышь 19 (фиг.5) содержит шар 140, первое 141 и второе 142 при- 5 жимные к шару колеса с одним, двумя или более отверстиями 143, первый 144 и второй 145 источники света, первый 146, второй 147, третий 148 и четвертый 149 фотоэлементы, первый 150,второй 151, третий 152 и 10 четвертый 153 усилители-формирователи, первый 154 и второй 155 анализаторы-формирователи, первый 156 и второй 157 входы первого анализатора-формирователя 154, первый 158 и второй 159 входы второго ана- 15 лизатора-формирователя 155, первый 160 и второй 161 выходы первого анализатора- формирователя 154, первый 162 и второй 163 выходы второго анализатора-формирователя 155.

0 Каждый из двух анализаторов-формирователей 154 и 155 мунипулятора Мышь 19 (фиг.5) содержит первый 164, второй 165, третий 166, четвертый 167, пятый 168 и шестой 169 элементы НЕ, первый 170 и второй 5 171 резисторы, первый 172. и второй 173 конденсаторы, первый 174, второй 175, третий 176 и четвертый 177 элементы И, первый 178 и второй 179 коммутаторы.

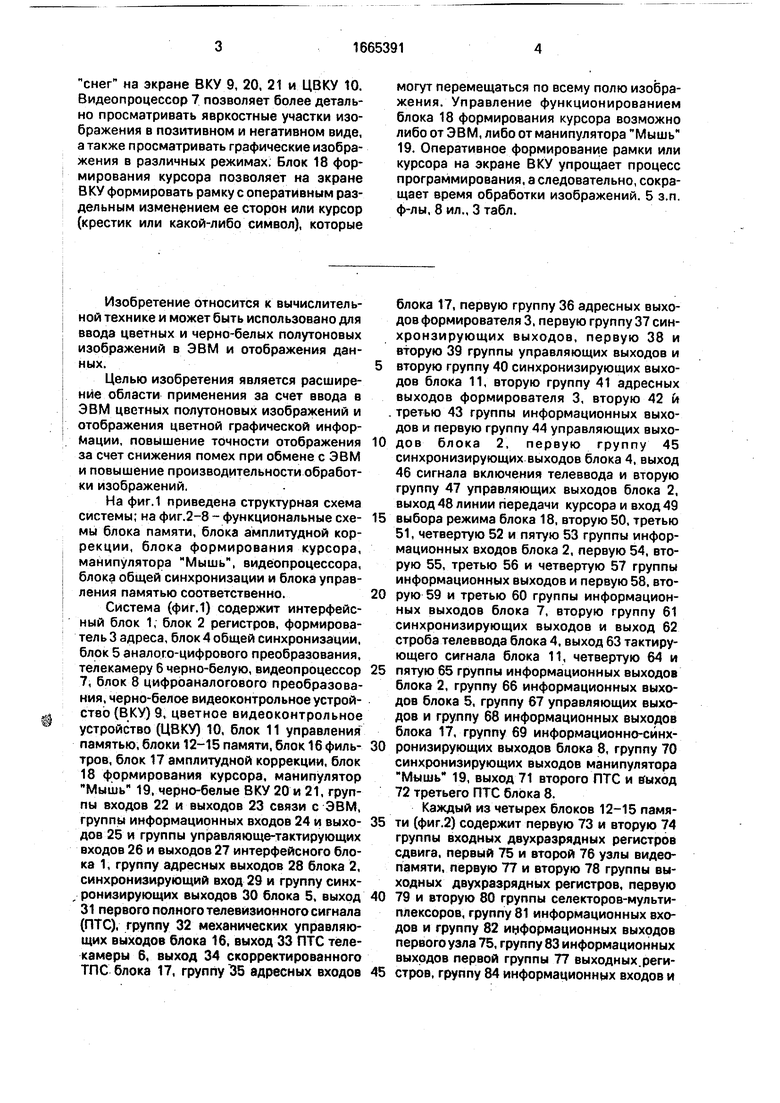

Видеопроцессор 7 (фиг.6) содержит се- 0 лектор-мультиплексор 180, преобразователь 181 цвета, первый 182, второй 183 и третий 184 арифметическо-логические узлы (АЛУ), группу 185 информационных выходов селектора-мультиплексора 180, первый 186, 5 второй 187 и третий 188 выходы преобразователя 181, первую 189.1 и вторую 189.2, третью 189.3 и четвертую 189.4 части группы 47 управляющих входов видеопроцессора 7, первую 190.1, вторую 190.2 и третью 190.3- 0 части группы 64 информационных входов видеопроцессора 7, первый 191.1, второй 191.2 и третий 191.3 информационные входы, составляющие группу 68 информационных входов видеопроцессра 7. 5 Каждый из трех узлов 182-184 видеопроцессора 7 (фиг.6) содержит формирователь 192 дополнительного кода, первый 193 и второй 194 сумматоры, первый 195 и второй 196 узлы сравнения, схему 197 сравне- 0 ния, шифратор 198, двоичный счетчик 199, коммутатор 200, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 201. первый 202. второй 203 и третий 204 элементы И-НЕ, первый 205 и второй 206 элементы И, селектор-мультиплексор 5 207, управляемый инвертор 208, группу 209 элементов ИЛИ, группу 210 элементов И, группу 211 информационных выходов фор- мировагеля 192, вторую группу 212.1 информационных входов узла 195, вторую группу 212.2 информационных входов узла 196,

группу 213 информационных выходов второго сумматора 194, группу 214 информационных выходов счетчика 199, выход 215 схемы 197, группу 216,1 управляющих входов коммутатора 200, первый вход 216.2 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 201, первый вход 216.3 первого элемента И-НЕ 202, первый вход 216.4 первого элемента И 205, вход 217 второго узла 196 сравнения, выход 218 первого узла 195 сравнения, первый 219, второй 220 и третий 221 выходы шифратора 198, выход 222 второго элемента И 206, группу 223 информационных выходов первого сумматора 193, группу 224 информационных выходов селектора-мультиплексора 207, выход 225 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 201, первый 226.1 и второй 226.2 выходы старших разрядов группы 226 информационных выходов управляемого инвертора 208, выход 227 первого элемента И 205, выход 228 коммутатора 200. группу 229 выходов труп-, пы 209 элементов ИЛИ, выход 230 третьего элемента И-НЕ 204,

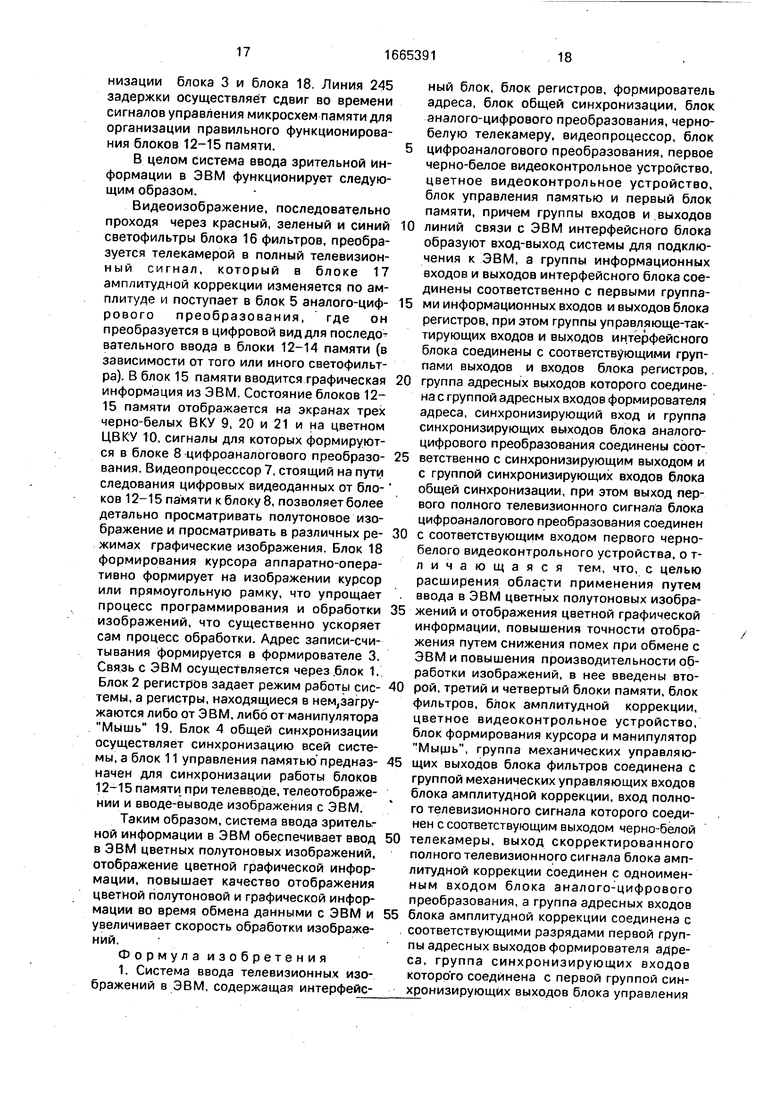

Блок 4 общей синхронизации (фиг.7) содержит задающий генератор 231, формиро- ватель 232 синхросигналов, коммутатор 233, формирователь 234 стробе телеввода, элемент И 235, выход 236 тактовой частоты задающего генератора 231, первый 237, второй 238, третий 239.1 и четвертый 239.2 входы коммутатора 233 и группу 240 выходов коммутатора 233.

Блок 11 управления памятью (фиг.8) содержит генератор-распределитель 241, формирователь 242 синхронизирующих сигналов, первый 243 и второй 244 формирователи управляющих сигналов, линию 245 задержки, группу 246 входов тактирующих сигналов формирователя 242, группу 247 входов тактирующих сигналов формирователя 243, группу 248 входов тактирующих сигналов формирователя 244, первую 249.1, вторую 249.2, третью 249.3 и четвертую 249.4 части группы 39 управляющих входов блока 11.

Система функционирует следующим образом.

Интерфейсный блок 1 предназначен для осуществления подключения системы (фиг.1) к шине конкретной ЭВМ, при этом этот блок содержит, например, шинные формирователи, адресный селектор, регистры защелки и дешифратор управляющих -сигналов ЭВМ. Состав группы 22 входов и группы 23 выходов блока 1 определяется шиной конкретной ЭВМ.

Блок 2 регистров предназначен для взаимодействия системы ввода зрительной информации с ЭВМ и содержит в своем

составе ряд программно доступных регистров: регистры адреса элемента изображе- ния PrX, PrY, регистры адреса местонахождения курсора PrXK.PrYK, регистры размеров сторон курсора-рамки PrXPK, PrYPK, регистр данных PrD, регистры верхнего и нижнего порогов уровней яркости участка просматриваемого яркостного поддиапазона для красного

0 РгНГШ, РгВПР, зеленого РгНПС, РгВГКЗ и синего РгНПВ, РгВПВ основных, составляющих изображение, цветов и регистр состояния и управления РгС, причем регистры PrXK. PrYK, PrXPK, PrYPK, РгНГШ, РгНГШ,

5 PrBflR, PrHFlG, PrBOG, РгНПВ и РгВПВ могут менять свое состояние при помощи манипулятора 19 и выполнены, например, на основе двоичных реверсивных счетчиков с параллельным вводом данных.

0 Формирователь 3 адреса предназначен для формирован-ия адреса считывания и адреса записи при телевводе изображений, хранимых в первом 12, втором 3. третьем 14 и четвертом 15 блоках памяти и для мульти5 плексирования сформированного адреса группы 36 адресных выходов формирователя 3 или адреса, поступившего по группе 28 адресных выходов блока 2 из регистров РгХ, PrY блока 2. Формирование адреса считывз0 ния в формирователе 3 происходит по сигналам, приходящим по группе 37 синхронизирующих входов на основе, например, двоичных синхронных счетчиков, а мультиплексирование адреса происходит по

5 сигналам, приходящим по группе 38 управляющих входов формирователя 3, посредством, например, селекторов-мультиплексоров 4 на Г. так как на группу 41 адресных входов блоков 12-15 памяти следует подавать попе0 ременно младшую и старшую половины сформированного адреса или адреса на ЭВМ через РгХ, PrY в связи с тем, что блоки 12-15 памяти выполнены на базе соответствующих микросхем памяти. При этом адрес из

5 ЭВМ поступает на блоки 12-15 памяти во время обмена данными между системой и ЭВМ со скоростью обмена данными, определяемой ЭВМ. Поэтому для того, чтобы на отображенном изображении при просмотре

0 не наблюдалась зашумленность в виде помех типа дождь или снег во время обмена данными между системой и ЭВМ, каждый из блоков 12-15 памяти имеет специальную конструкцию, приведенную на фиг.2.

5 Каждый из блоков 12-15 памяти функционирует следующим образом (фиг.2). При телевводе данные мз блока 5 через группу 66 информационных входов поступают на входы последовательного ввода данных первой 73 и второй 74 групп входных регистрое сдвига, а при записи данных ЭВМ данные регистра PrD блока 2 через группу 65 информационных входов поступают на входы последовательного ввода данных первой 73 и второй 74 групп входных регистров сдвига, причем при телевводе данные вводятся последовательно по два байта то в первую 73, то во вторую 74 группы входных регистров сдвига и также по два байта записываются то в первый 75, то во второй 76 узлы видеопамяти, а при поступлении данных от ЭВМ каждый поступающий байт данных через входы последовательного ввода данных вводится в первую 73 и во вторую 74 группы входных регистров сдвига, но запись этого байта будет произведена только в ту ячейку узлов 75 и 76, в которую будет направлен сигнал разрешения записи. Считывание из первого 75 и второго 76 узлов происходит по два байта одновременного то из одного, то из другого узла и также по два байта одновременно записываются то в первую 77, то во вторую 78 группы выходных регистров, а первая 79 и вторая 80 груп- пыселекторов-мультиплексоров

пропускают на свои выходы то один, то второй, то третий, то четвертый байты, записанные и продолжающие записываться в первой 77 и второй 78 группах выходных регистров. Причем, если в какой-либо момент времени произойдет считывание по адресу ЭВМ (РгХ, PrY), то считанные два байта, один из которых является требуемым, запишутся либо в первую 77, либо во вторую 78 группы выходных регистров, после чего происходит следующее: требуемый байт, считанный по адресу ЭВМ, через группу 80 селекторов-мультиплексоров поступает в блок 2, в регистр PrD, и далее в ЭВМ. а группа 79 селекторов-мультиплексоров вместо двух байтов, считанных по адресу ЭВМ, . пропустит на свои выходы сначала последний байт из двух байтов, считанных до тех двух байтов, которые были считаны по адресу ЭВМ, а потом - первый байт из двух байтов, считанных после тех двух байтов, которые были считаны по адресу ЭВМ, т.е: произойдет раздвоение двух соседних элементов изображения, что является практически незаметным для восприятия - тем самым достигается цель повышения качества отображения изображений во время обмена данными системы с ЭВМ. Точно так же происходит раздвоение соседних элементов изображения и во время записи байтов данных, поступающих из ЭВМ. По первой 87 группы 39 входов приходят сигналы управления переключением группы 79 селекторов-мультиплексоров и сигнал их запирания для отключения отображения.

По второй части 88 группы 39 входов приходят сигналы управления переключением группы 80 селекторов-мультиплексоров и сигнал включения их высокого выходного 5 импеданса в третье состояние, если группы 80 селекторов-мультиплексоров блоков 12- 15 памяти соединены в блоке 2 по схеме МОНТАЖНОЕ ИЛИ. По третьей части 89 группы 39 входов приходят сигналы управ- 10 ления работой микросхем памяти первого узла 75, а по четвертой части 90 группы 39 входов - сигналы управления работой микросхем памяти второго узла 76, при этом сигналы управления третьей 89 и четвертой 5 90 частей группы 39 входов одинаковы, но сдвинуты во времени по отношению друг к другу на время вывода двух элементов изображения на экран ВКУ. Сигнал входа 62 переводит первую 73 и вторую 74 группы 0 входных регистров сдвига в режим последовательного или параллельного ввода, а на первый 91, второй 92, третий 93 и четвертый 94 входы группы 40 синхронизирующих входов приходят сигналы тактирования вво- 5 да данных в группы 73 и 74 входных регистров и в группы 77 и 78 выходных регистров, при этом сигналы тактирования ввода дан- ныхсдвинуты во времени аналогично сдвигу сигналов управления первого 75 и второго 0 76 узлов видеопамяти.

Для осуществления правильного ввода цветных изображений и для оперативного проведения настройки системы для пра- вильного ввода цветных изображений в нее 5 введены блок 16 фильтров и блок 17 амплитудной коррекции. Рассмотрим функционирование этих блоков во взаимодействии друг с другом и с другими блоками системы. Блок 16 фильтров устанавливается непос- 0 редственно перед объективом телекамеры 6 и в непосредственной близости от усилителей 95-97 и переключателя-преобразователя 98 блока 17 амплитудной коррекции (фиг.З). Переключатель-преобразователь 98 5 состоит, например, из трех двойных кнопочных переключателей, которые переключаются, например, под действием давления на них светофильтров блока 16 после установки их перед обьективом телекамеры, что и 0 является механической связью между блоками 16 и 17. Первые части этих двойных кнопочных переключателей переключают выходы 104-106 усилителей 95-97 на выход 34 скорректированного ПТС, а вторые части 5 этих кнопок коммутируют логическую единицу или ноль для включения-выключения элементов ИЛИ 101-103состробирующими входами, т.е. при установке перед обьективом телекамеры 6 того или иного светофильтра блока 16 подключается к выходу 34

блока 17 тот или иной выход 104-106 усилителей 95-97 блока 17 и включается тот или другой элемент ИЛИ 101-103 блока 17. Таким образом, переключатель-преобразователь 98 переключает аналоговые сигналы и преобразовывает механическое переключение светофильтров в электрические сигналы логических О или 1. Рассмотрим теперь более подробно принцип функционирования блоков 16 и417 при вводе цветных полутоновых изображений. Известно, что белый свет (цвет) состоит из определенного соотношения красного, зеленого и синего цветов, а именно в системе ЗЕКАМ принято, что белый цвет состоит из 30% красного, 59% зеленого и 11 % синего цветов. Поэтому при вводе эталонного белого изображения в усилителях 95-97 блока 17 устанавливаются такие коэффициенты усиления, чтобы выдержать перечисленные пропорции. Для осуществления эффективного и удобного контроля при установке коэффициентов усиления узел 99 памяти хранит три метки, оторые по адресу элементов строк изображения, поступающему по группе 35 входов, отображаются в виде, например, вертикальных полос шириной в восемь элементов, причем каждая из трех меток полос занимает на экране ВКУ строго определенное место, соответствующее количественному соотношению трех составляющих цветов белого эталонного изображения. Из группы 66 информационных выходов блока 5 видеоинформация цветных изображений, составляющих эталонное белое изображение, поступает в схему 100, где она сравнивается с линейно изменяющимся адресом элементов строк изображения, т.е. происходит ее количественная оценка. При совпадении адреса и видеоданных на выходе 111 схемы 100 появляются сигналы, которые так же, как метки, отображаются на экране ВКУ в виде вертикальных полос, которые при изменении крэффициентов усиления усилителей 95- 97 будут перемещаться в горизонтальном направлении. Если каждую такую полосу количественной оценки видеоданных совместить, изменяя коэффициенты усиления усилителей 95-97, каждую со своей полосой - меткой при вводе эталонного белого изображения, то это будет означать, что система подготовлена для ввода цветных полутоновых изображений. Для определенности будем считать, что усилители 95-97 предназначены для амплитудной коррекции соотве тственно красного, зеленого и синего составляющих цветов цветного изображения, выходы 112-114 узла 99 памяти являются выходами меток количественного состава красного, зеленого и синего составляющих цветов эталонного белого изображения, а элементы ИЛИ 101-103 пропускают соответвественно каждый свою метку и сигналы количественной оценки видеоданных в зависимости от положения светофильтров в блоке 16.

Блок 5 предназначен для осуществления привязки к постоянному уровню полного телевизионного сигнала ПТС, селекции

0 кадрового синхроимпульса и строчного синхроимпульса КСИ и ССИ из ПТС и для аналого-цифрового преобразования.

Блок 18 формирования курсора (фиг.4) функционирует следующим образом. На

5 первую группу 127.1 входов схемы 118 поступает текущий адрес элементов строк изображения, а на первую группу 127.2 входов схемы 119 поступает текущий адрес строк изображения. На вторую группу 128.1 вхо0 дов схемы 118 поступает адрес курсора по оси X от РгХК блока 2, а на вторую группу 128.2 входов схемы 119 поступает адрес курсора по оси Y от PrYK блока 2. Схемы 118 и 119 при совпадении адреса курсора с теку5 щим адресом считывания отображаемого изображения формируют на своих выходах 129 и 133 импульсы совпадения, которые, поступая на входы установки триггеров 120 и 121, переводят их в единичное состоя0 ние. На группу 135.1 информационных выходов счетчика 122 поступают данные о размере рамки по оси X из регистра РгХРК блока 2, а на группу 135.2 информационных входов счетчика 123 поступают данные о

5 размере рамки по оси Y из регистра PrYPK блока 2. На синхронизирующий вход 136.1 счетчика 122 приходят тактовые импульсы формирования текущего адреса элементов строк изображения отображения, а на син0 хронизирующий вход 136.2 счетчика 123 приходят тактовые импульсы формирования текущего адреса строк изображения отображения, при этом указанные тактовые импульсы до переключения триггеров 120 и

5 121 в единичное состояние производят ввод в счетчики 122 и 123 входных данных о раз- , мере сторон рамки по осям X и Y, а после переключения триггеров 120 и 121 в единичное состояние указанные тактовые импуль0 сы производят счет в счетчиках 120 и 121 до величины, определяемой группами 135.1 и 135.2 информационных входов счетчиков 120и 121, после чего на их выходах 130 и 132 формируются импульсы окончания счета,

5 которые переводят триггеры 120 и 121 в нулевое состояние по своему заднему фронту. Импульсы совпадения с выхода 129 схемы 118 пропускаются коммутатором 124 по сигналам выхода 131 триггера 121, образуя при этом левую сторону рамки. Импульсы

выхода 130 окончания счета счетчика 122 пропускаются коммутатором 124 по сигналам с выхода 131 триггера 121, образуя при этом правую сторону рамки. Импульс с выхода 133 узла 119 пропускается коммутато- ром 124 по сигналу с выхода 134 триггера 120, образуя при этом верхнюю сторону рамки. Импульс с выхода 132 окончания счета счетчика 123 пропускается коммутатором 124 по сигналу с выхода 134 триггера 121, образуя при этом нижнюю сторону рамки.

Таким образом, на выходе 139 коммутатора 124 сформировалась последовательность сигналов, образующих на экране ВКУ прямоугольную рамку с заданным разме- ром ее вертикальных и горизонтальных сторон. Эта последовательность сигналов, проходя через мультиплексор 125$ по сигналу выбора режима входа 49 блока 18 поступает на выход 48 линии передачи курсора блока 18. Если необходимо вывести на экран ВКУ какой-либо символ из памяти 126 хранения символа, то на информационные группы входов 135.1 и 135.2 счетчиков 122 и 123 следует передать данные о размере зо- ны хранения символа в памяти 126, при этом группы 137.1 и 137.2 информационных выходов счетчиков 122 и 123 являются адресом считывания символа из памяти 126. Символ памяти 126 через выход 138 в виде последовательности сигналов, его формирующих, также поступает на выход 48 линии передачи курсора при переключении сигнала выбора режима входа 49 блока 18.

Манипулятор 19 (фиг.5) функционирует следующим образом. Первое 141 и второе 142 колеса при вращении шара 140 открывают или закрывают свет от первого 144 и sjoporo 145 источников света одновременно перед обоими первым 146 и вторым 147 и перед обоими третьим 148 и четвертым, 149 фотоэлементами. Фототоки фотоэлементов 146-149 усиливаются усилителями- формирователями 150-153 и в виде импульсов длиной, определяемо й скоро- стью вращения прижимных к шару колес, поступают на входы 156-159 анализаторов- формирователей 154 и 155. Анализатор- формирователь 154 (155) определяет направление движения прижимного к шару колеса 141 (142) и за один проход одного из отверстий 143 колеса 141 (142) между обоими фотоэлементами 146 и 147 (148 и 149) и источником света 144 (145) формирует четыре коротких импульса на первом 160 (162) или втором 161 (163) синхронизирующем выходе. Длительности коротких импульсов на выходах анализаторов-формирователей 154 и 155 определяются входящими в них интегрирующими RC-цепочками.

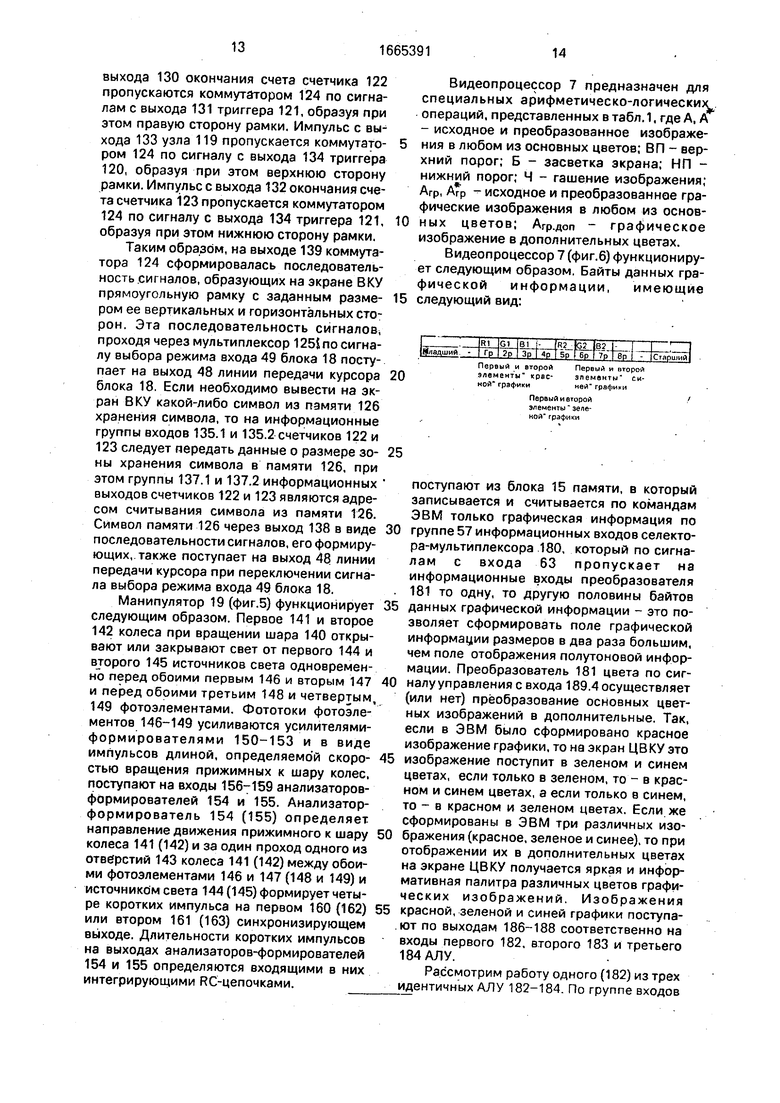

Видеопроцессор 7 предназначен для специальных арифметическо-логических операций, представленных в табл.1, где А, А - исходное и преобразованное изображения в любом из основных цветов; ВП - верхний порог; Б - засветка экрана; НП - нижний порог; Ч - гашение изображения; АГр, - исходное и преобразованное графические изображения в любом из основных цветов; Агр.доп - графическое изображение в дополнительных цветах.

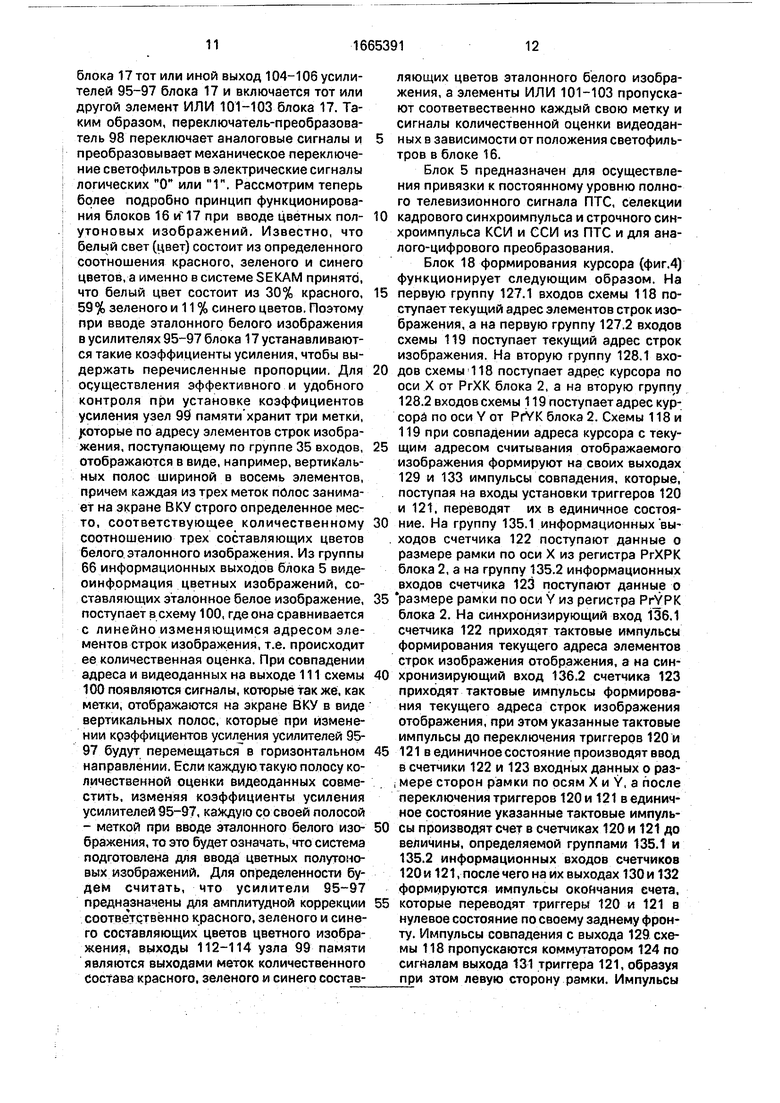

Видеопроцессор 7 (фиг.6) функционирует следующим образом. Байты данных графической информации, имеющие следующий вид:

Первый и второйПервый и второй

элементы крас- элементы си- ной графикиней графики

Первый и второй элементы зеленой графики

поступают из блока 15 памяти, в который записывается и считывается по командам ЭВМ только графическая информация по группе 57 информационных входов селектора-мультиплексора 180, который по сигналам с входа 63 пропускает на информационные входы преобразователя 181 то одну, то другую половины байтов данных графической информации - это позволяет сформировать поле графической информации размеров в два раза большим, чем поле отображения полутоновой информации. Преобразователь 181 цвета по сигналу управления с входа 189.4 осуществляет (или нет) преобразование основных цветных изображений в дополнительные. Так, если в ЭВМ было сформировано красное изображение графики, то на экран ЦВКУ это изображение поступит в зеленом и синем цветах, если только в зеленом, то - в красном и синем цветах, а если только в синем, то - в красном и зеленом цветах. Если же сформированы в ЭВМ три различных изображения (красное, зеленое и синее), то при отображении их в дополнительных цветах на экране ЦВКУ получается яркая и информативная палитра различных цветов графических изображений. Изображения красной, зеленой и синей графики поступают по выходам 186-188 соответственно на входы первого 182, второго 183 и третьего 184 АЛ У.

Рассмотрим работу одного (182) из трех идентичных АЛ У 182-184. По группе входов

Селектор-мультиплексор 207 произво- дит селекцию даннных группы 223 информационных входов в соответствии с табл.3. Таким образом, требуемый участок яр- костного диапазона изображения растягивается на весь яркостный диапазон от 0 до 255 уровней яркости, что позволяет очень детально его просматривать на экране АКУ, На выходе 218 узла 195 появляется логическая единица, если значения очередного байта информации больше нижнего порога, а на выходе 217 узла 196 появляется логическая единица, если значение очередного байта информации меньше или равно верхнему порогу заданного участка яркостного диапазона изображения. Таким образом, выход 222 элемента И 206 находится в состоянии логической единицы, если очередной байт информации попадает в заданный яркостный поддиапазон, и разрешает прохождение данных через селектор- мультиплексор 207, но запрещает прохождение данных, если очередной байт информации не попадает в заданный яр- костный поддиапазон и на выходе элемента И 206 появляется логический ноль. При этом, если значения очередного байта информации меньше нижнего порога, то управляемый инвертор 208 пропускает через себя данные без инвертирования (в режиме - позитивного отображения изображений) и с инвертированием (в режиме негативного отображения изображений). Режимом работы управляемого инвертора 208 управляет элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 201, на один вход 216.2 которого приходит сигнал

позитивно-негативного просмотра изображений, а на другой вход 217 которого поступает сигнал с выхода узла 196 сравнения. Коммутатор 200 пропускает по сигналам управления группы 216.1 на вход 228 одновременно или раздельно данные графического изображения, данные курсора и данные о коррекции соответствующего усилителя блока 17. Если эти данные проходят через элемент И 205 на группу 209 элементов ИЛИ, то это является режимом засветки, если же эти данные проходят через элемент И-НЕ 204 на группу элементов И 210, то это является режимом гашения, а если эти данные проходят через элемент И 205 либо через И-НЕ 204 при управлении от двух старших разрядов 226.1 и 226.2 группы информационных выходов управляемого инвертора 208, то это является режимом Хамелеон (см. табл,1). Управляющие входы 216.3 и 216.4 осуществляют выбор требуемого режима при отображении графической информации,

Блок 4 общей синхронизации, осуществляющий синхронизацию всей системы, функционирует следующим образом. Заданный генератор 231 формирует на выходе

236тактовую частоту 13 МГц Формирователь 232 синхросигналов формирует телевизионные кадровые и строчные сигналы синхронизации на выходе 61 и на первом

237и втором 238 выходах. Формирователь 234 строба телеввода по сигналу 46 включения телеввода и по сигналам 239.2 кадровой синхронизации телекамеры формирует строб телеввода длительностью в один кадр на выходе 62. Этот строб телеввода открывает элемент И 235, который пропускает тактовую частоту с выхода 236 на выход 29 для синхронизации блока 5 аналого-цифрового преобразователя и пропускает на выход 240 коммутатора 233, выполненного, например, в виде селектора-мультиплексора 2 на Г, кадровые и строчные синхросигналы телекамеры, поступающие по входам 239.1 и 239.2.

Блок 11 управления памятью функционирует следующим образом. Генератор-распределитель 241 формирует последовательность сигналов для управления формирователя 242, формирующего группу 40 сигналов для тактирования регистров блоков памяти, для управления формирователя 243, формирующего сигналы 38 мультиплексирования адреса и сигналы 249.1 и 249.2 для мультиплексирования считанных данных из блоков памяти для управления формирователя 244, формирующего сигналы управления микросхемами памяти блоков 12-15 и для формирования группы 37 сигналов синхронизации блока 3 и блока 18. Линия 245 задержки осуществляет сдвиг во времени сигналов управления микросхем памяти для организации правильного функционирования блоков 12-15 памяти.

В целом система ввода зрительной информации в ЭВМ функционирует следующим образом.

Видеоизображение, последовательно проходя через красный, зеленый и синий светофильтры блока 16 фильтров, преобразуется телекамерой в полный телевизионный сигнал, который в блоке 17 амплитудной коррекции изменяется по амплитуде и поступает в блок 5 аналого-цифрового преобразования, где он преобразуется в цифровой вид для последовательного ввода в блоки 12-14 памяти (в зависимости от того или иного светофильтра). В блок 15 памяти вводится графическая информация из ЭВМ. Состояние блоков 12- 15 памяти отображается на экранах трех черно-белых ВКУ 9, 20 и 21 и на цветном ЦВКУ 10, сигналы для которых формируются в блоке 8 цифроаналогового преобразования. Видеопроцесссор 7, стоящий на пути следования цифровых видеоданных от блоков 12-15 памяти к блоку 8, позволяет более детально просматривать полутоновое изображение и просматривать в различных режимах графические изображения. Блок 18 формирования курсора апларатно-опера- тивно формирует на изображении курсор или прямоугольную рамку, что упрощает процесс программирования и обработки изображений, что существенно ускоряет сам процесс обработки. Адрес записи-считывания формируется в формирователе 3. Связь с ЭВМ осуществляется через .блок 1. Блок 2 регистров задает режим работы системы, а регистры, находящиеся в нем,загру- жаются либо от ЭВМ, либо от манипулятора Мышь 19. Блок 4 общей синхронизации осуществляет синхронизацию всей системы, а блок 11 управления памятью предназначен для синхронизации работы блоков 12-15 памяти при телевводе, телеотображении и вводе-выводе изображения с ЭВМ.

Таким образом, система ввода зрительной информации в ЭВМ обеспечивает ввод в ЭВМ цветных полутоновых изображений, отображение цветной графической информации, повышает качество отображения цветной полутоновой и графической информации во время обмена данными с ЭВМ и увеличивает скорость обработки изображений.

Формула изобретения

0 линий связи с ЭВМ интерфейсного блока образуют вход-выход системы для подключения к ЭВМ, а группы информационных входов и выходов интерфейсного блока соединены соответственно с первыми группа5 ми информационных входов и выходов блока регистров, при этом группы управляюще-так- тирующих входов и выходов интерфейсного блока соединены с соответствующими группами выходов и входов блока регистров,

0 группа адресных выходов которого соединена с группой адресных входов формирователя адреса, синхронизирующий вход и группа синхронизирующих выходов блока аналого- цифрового преобразования соединены соот5 ветственно с синхронизирующим выходом и с группой синхронизирующих входов блока общей синхронизации, при этом выход первого полного телевизионного сигнала блока цифроаналогового преобразования соединен

0 с соответствующим входом первого черно- белого видеоконтрольного устройства, о т- личающаяся тем, что, с целью расширения области применения путем ввода в ЭВМ цветных полутоновых изобра5 жений и отображения цветной графической информации, повышения точности отображения путем снижения помех при обмене с ЭВМ и повышения производительности обработки изображений, в нее введены вто0 рой, третий и четвертый блоки памяти, блок фильтров, блок амплитудной коррекции, цветное видеоконтрольное устройство, блок формирования курсора и манипулятор Мышь, группа механических управляю5 щих выходов блока фильтров соединена с группой механических управляющих входов блока амплитудной коррекции, вход полного телевизионного сигнала которого соединен с соответствующим выходом черно-белой

0 телекамеры, выход скорректированного полного телевизионного сигнала блока амплитудной коррекции соединен с одноименным входом блока аналого-цифрового преобразования, а группа адресных входов

5 блока амплитудной коррекции соединена с соответствующими разрядами первой группы адресных выходов формирователя адреса, группа синхронизирующих входов которого соединена с первой группой синхронизирующих выходов блока управления

памятью и с группой синхронизирующих выходов блока формирования курсора, группа адресных входов которого соединена с первой группой адресных выходов формирователя адреса, группа управляющих входов которого соединена с первой группой управляющих выходов блока управления памятью, вторая группа управляющих и вторая группа синхронизирующих выходов которого соединена соответственно с группой управляющих и с группой синхронизирующих входов с первого по четвертый блоков памяти, группы адресных входов которых поразрядно объединены и соединены с второй группой адресных выходов формирователя адреса, при этом первая и вторая группы информационных входов блока формирования курсора соединены соответственно с второй и третьей группами информационных выходов блока регистров, первая группа управляющих выходов которого соединена с первой группой управляющих входов блока управления памятью, группа синхронизирующих входов которого соединена с первой группой синхронизирующих выходов блока общей синхронизации, вход сигнала включения телеввода которого соединен с соответствующим выходом блока регистров, вторая группа управляющих выходов которого соединена с группой управляющих входов видеопроцессора, вход линии передачи курсора которого соединен с соответствующим выходом блока формирования курсора, вход выбора режима которого Соединен с соответствующим выходом блока регистров, вторая, третья, четвертая и пятая группы информационных входов которого соединены с первыми группами информационных выходов соответственно первого, второго, третьего и четвертого блоков памяти, вторые группы информационных выходов которых соединены соответственно с первой, второй, третьей и четвертой группами информационных входов видеопроцессора, с первой по третью группы информационных выходов которого соединены соответственно с первой по третью группами информационных входов блока цифроаналогового преобразования, группа синхронизирующих входов которого соединена с второй группой синхронизирующих выходов блока общей синхронизации, выход строба телеввода которого соединен с соответствующими входами с первого по , четвертый блоков памяти и с соответствующим входом блока управления памятью, выход тактирующего сигнала которого соединен с соответствующим входом видеопроцессора, пятая группа информационных входов которого соединена с четвертой

группой информационных выходов блока

регистров, пятая группа информационных

выходов которого соединена с пятыми груп. пами информационных входов с первого по

четвертый блоков памяти, при этом вторые группы информационных входов с первого по третий блоков памяти поразрядно объединены и соединены с группой информационных выходов блока аналого-цифрового

0 преобразования и группой информационных входов блока амплитудной коррекции, группа управляющих выходов которого соединена с второй группой управляющих входов блока управления памятью, при этом

5 группа информационных выходов блока амплитудной коррекции соединена с шестой группой информационных входов видеопроцессора, а группа информационно-синхронизирующих выходов блока

0 цифроаналогового преобразования соединена с соответствующей группой входов цветного видеоконтрольного устройства , группа синхронизирующих выходов манипулятора Мышь соединена с группой син5 хронизирующих входов блока регистров.

0 второй узлы видеопамяти, первую и вторую группы выходных двухразрядных регистров и первую и вторую группы селекторов-мультиплексоров, причем группы входов последовательного ввода данных первой и второй

5 групп входных регистров сдвига поразрядно объединены и являются второй группой информационных входов блока памяти, группы входов параллельного ввода данных первой и второй групп входных регистров

0 сдвига поразрядно объединены и являются первой группой информационных входов блока памяти, вход строба телеввода которого соединен с входом выбора режима входных регистров сдвига первой и второй

5 групп, группа информационных выходов первой группы входных регистров сдвига соединена с группой информационных входов первого узла видеопамяти, группа информационных выходов которой соединена

0 с первыми группами информационных входов селекторов-мультиплексоров первой и второй групп, группа информационных выходов входных регистров сдвига второй группы соединена с группой информа.цион5 ных входов второго узла видеопамяти, группа информационных выходов которого соединена с группрй информационных входов выходных регистров второй группы, группа информационных выходов которых соединена с вторыми группами информационных входов селекторов-мультиплексоров первой и второй групп, группы информационных выходов которых являются соответственно первой и второй группами информационных выходов блока памяти, группа управляющих входов которого соединена с группами управляющих входов селекторов-мультиплексоров первой и второй групп и первого и второго узлов видеопамяти, группы адресных входов первого и второго узлов видеопамяти поразрядно объединены и являются группой адресных входов блока памяти, синхронизирующие входы группы которого соединены с синхронизирующими входами первых и вторых групп входных и выходных регистров.

первого, второго и третьего элементов ИЛИ со стробирующими входами являются группой информационных выходов блока амплитудной коррекции.

тем, что блок формирования курсора содержит первую и вторую схемы сравнения, первый и второй триггеры, первый и второй двоичные счетчики, коммутатор, мульти10 плексор и узел памяти хранения символа,причем первые группы информационных входов первой и второй схем сравнения являются соответственно первой и второй частями группы адресных входов блока

5 формирования курсора, первая и вторая части первой группы информационных входов которого соединены соответственно с вторыми группами информационных входов первой и второй схем сравнения, выход пер0 вой схемы сравнения подключен к первому информационному входу коммутатора и к входу установки первого триггера, вход синхронизации которого подключен к выходу сигнала окончания счета первого счетчи5 ка и к второму информационному входу коммутатора, первый и второй управляющие входы коммутатора подключены к выходу второго триггера и к входу выбора режима второго счетчика, выход сигнала

0 окончания счета которого подключен к третьему информационному входу коммутатора и к входу синхронизации второго триггера, вход установки которого подключен к выходу второй схемы сравнения и к четвер5 тому информационному входу коммутатора, третий и четвертый управляющие входы которого подключены к выходу первого триггера и к входу выбора режима первого счетчика, информационные группы входов

0 первого и второго счетчиков являются соответственно первой и второй частью второй группы информационных входов блока формирования курсора, группа синхронизирующих, входов которого состоит из

5 синхронизирующего входа первого счетчика и синхронизирующего входа второго счетчика, а группы информационных выходов первого и второго счетчиков соединены соответственно с первой и второй частями

0 группы адресных входов узла памяти хранения символа, выход которого подключен к первому информационному входу мультиплексора, второй информационный вход которого подключен к выходу коммутатора,

5 управляющий вход и информационный выход мультиплексора являются соответственно входом выбора режима и выходом линии передачи курсора блока формирования курсора.

. 5. Система по п. 1,отличающаяся тем, что видеопроцессор содержит селектор-мультиплексор, преобразователь цвета, первый, второй и третий арифметическо-ло- гические узлы, причем первые группы информационных входов первого, второго и третьего арифметико-логических узлов являются соответственно первой, второй и третьей группами информационных входов видеопроцессора, четвертая группа информационных входов которого является группойинформационныхвходовселектора-мультиплексора, группа информационных выходов которого соединена с группой информационных входов преобразователя цвета, при этом первые информационные входы первого, второго и третьего арифметико-логических узлов соединены соответственно с первым, вторым и третьим информационными выходами преобразователя цвета, а группы управляющих входов первого, второго и третьего арифметико-логических узлов и управля ющий вход преобразователя цвета являются соответственно первой, второй, третьей и четвертой частями группы управляющих входов видеопроцессора, вход линии передачи курсора которого соединен с вторыми -информационными входами с первого по третий арифметико-логических узлов, вторые группы информационных входо в которых являются соответственно первой, второй и третьей частями пятой группы информационных входов видеопроцессора, вход тактирующего сигнала которого соединен с синхронизирующими входами с первого по третий арифметико-логических узлов и с управляющим входом селектора-мультиплексора, третьи информационные входы первого, второго и третьего арифметико-логических узлов являются шестой группой информационных входов видеопроцессора, первая, вторая, и третья группы информационных выходов которого соединены с группами информационных выходов соответственно первого, второго и третьего арифметико-логических узлов, каждый из которых содержит формирователь дополнительного кода, первый и второй сумматоры, первый и второй узлы сравнения, схему сравнения, шифратор, двоичный счетчик, коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. первый, второй и третий элементы И-НЕ, первый и второй элементы И, селектор-мультиплек- - сор, управляемый инвертор, группу элементов ИЛИ и группу элементов И, причем в каждом арифметико-логическом узле первая группа информационных входов соединена с первыми группа.ми информационных входов первого и второго узлов сравнения и

первого сумматора, вторая группа информационных входов которого соединена с первой группой информационных входов второго сумматора и группой информационных выходов формирователя дополнительного кода, группа информационных входов которого соединена с второй группой информационных входов первого узла сравнения и с первой частью второй группы

0 информационных входов арифметико-логического узла, вторая часть второй группы информационных входов которого соединена с вторыми группами информационных входов второго узла сравнения и второго

5 сумматора, группа информационных выходов которого соединена с первой группой информационных входов схемы сравнения, вторая группа информационных входов которой соединена с группой информацион0 ных входов шифратора и группой информационных выходов двоичного счетчика, управляющий вход которого соединен с выходом схемы сравнения, синхронизирующий вход счетчика является синхронизи5 рующим входом арифметико-логического узла, первый, второй и третий информационные входы которого подключены к соответствующим информационным входам коммутатора, группа управляющих входов

0 которого является первой частью группы-управляющих входов арифметико-логического узла, при этом первые входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первого элемента И- НЕ и первого элемента И являются

5 соответственно второй, третьей и четвертой частями группы управляющих входов арифметико-логического узла, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом второго узла сравнения и первым

0 входом второго элемента И, второй вход которого соединен с выходом первого узла сравнения, первый, второй и третий выходы шифратора соединены соответственно с первым, вторым и третьим управляющими

5 входами селектора-мультиплексора, стро- бирующий вход которого подключен к выходу второго элемента И, группа информационных выходов первого сумматора соединена с группой информационных

0 входов селектора-мультиплексора, группа информационных выходов которого соединена с группой информационных входов управляющего инвертора, управляющий вход которого подключен к выходу-элемента ИС5 КЛЮЧАЮЩЕЕ ИЛИ, группа информационных выходов управляющего инвертора соединена с группой первых входов элементов ИЛИ группы, группа вторых входов которых подключена к выходу первого элемента И, второй вход которого соединен

с выходом первого элемента И-НЕ и с первым входом второго элемента И-НЕ, второй вход которого соединен с первым входом первого элемента И, третий вход которого соединен с выходом коммутатора и с первым входом третьего элемента И-НЕ, второй вход которого подключен к выходу второго элемента И-НЕ, при этом второй и третий входы первого элемента И-НЕ соединены соответственно с первым и вторым старшими разрядами группы информационных выходов управляемого инвертора, груп- па выходов элементов .ИЛИ группы

ГВ, при ВП А 255 А, при НП A s ВП Ч, при ОсА НП

А

А

А

Л 1C

A tp

А - НПОпределение постояннной

составляющей от требуемого участка яркостного диапазона

«

&Инвертирование изображения

А-г-рОтображение графических

изображений в режиме гашения

Агр, если 192 А «225 Отображение графических

А .о, если 04 А 1 92 « рахенш на фоне по- 1лутонового изображения

в режиме Хамелеон

Aip jjm,.Отображение графических

изображений в дополнительных цветах

I

соединена с группой первых входов элемей- та И группы, вторая группа входов которых подключена к выходу третьего элемента И- НЕ, при этом выходы элементов И группы являются группой информационных выходов арифметико-логического узла.

б. Система по п.1,отличающаяся тем, что в нее дополнительно введены вторые и третьи видеоконтрольные устройства, входы полного телевизионного сигнала которых соединены с выходами второго и третьего одноименных сигналов блока циф- роаналогового преобразования.

Таблица 1

Вьделение требуемого участка яркостного диапазона изображения

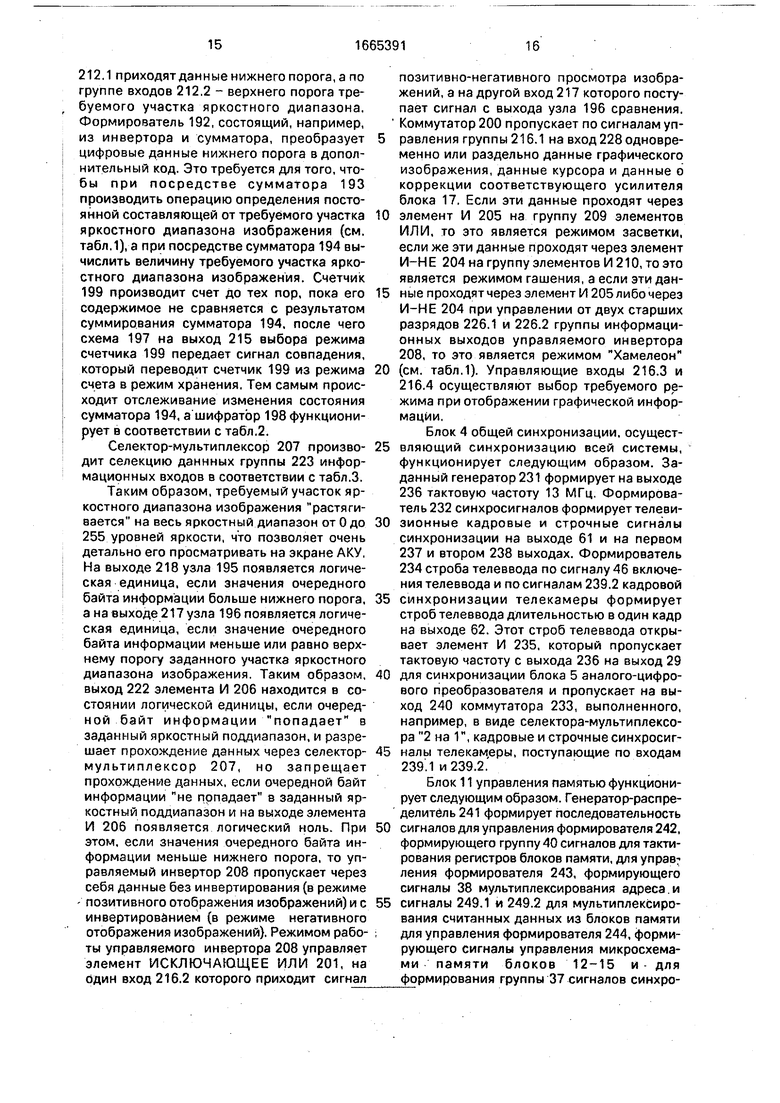

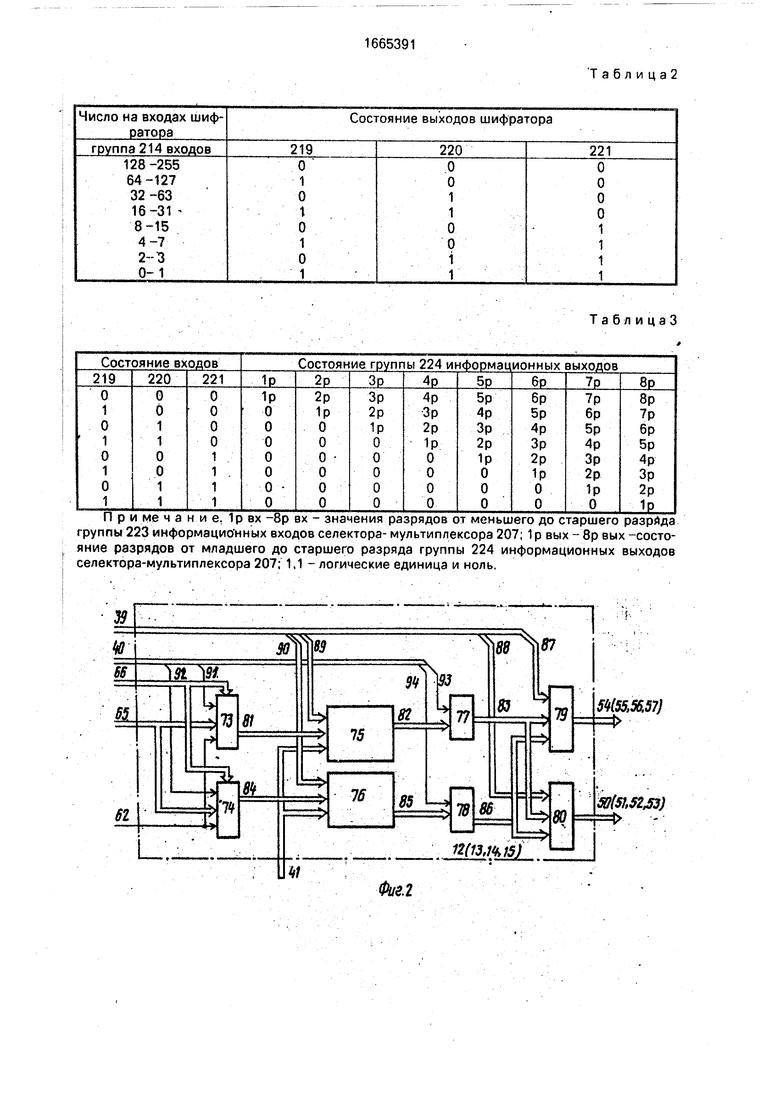

Примечание. 1рвх -8р вх - значения разрядов от меньшего до старшего разряда группы 223 информационных входов селектора- мультиплексора 207, 1р вых - 8р вых -состояние разрядов от младшего до старшего разряда группы 224 информационных выходов селектора-мультиплексора 207; 1,1 - логические единица и ноль.

Таблица2

ТаблицаЗ

М(55,56,57)

Ј

Lb$

№Я,Я,53) Ј Мф

99 SЈ

-о ЈЈ

1бе9991

Фиг. 6

39

1 гпф

| Патент США № 4536848, кл | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Романов Ю.Н | |||

| и др | |||

| Модуль ввода зрительной информации в микроЭВМ | |||

| - Механизация и автоматизация управления | |||

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

Авторы

Даты

1991-07-23—Публикация

1989-06-26—Подача