1

Изобретение относится к импульсной технике, в частности к дискретно-аналоговым преобразователям с контролем, и может быть иримеиено в устройствах автоматики и вычислительной техники.

Известны преобразователи кода во временной интервал, содержащие последовательно соединенные счетчик, схему совпадения, генератор тактовых импульсов, схему сравнения, подключенную входами к регистру хранения преобразуемых кодов и счетчику.

Однако известные устройства имеют низкую оперативность контроля вследствие привязки периода к концу цикла и непостоянства длительности периода контроля (от нуля до длительности цикла). В многоканальных нреобразователях информации ЦВМ подобный контроль более затруднен, так как их оборудование еще более загружено выполнением основных функций.

С целью обеспечения полного оиеративиого контроля в предлагаемое ycTpoiicTBO введены элементы совпадения, инвертор и элемент задержки, триггеры режима контроля и индикации отказов, причем выход первого элемента совпадения, управляющий вход которого нодключен к первому выходу триггера режима контроля, соединен со входом регистра хранения преобразуемых кодов и через второй элемент совпадения - со входом триггера индикации отказов, первый вход триггера режима контроля подключен к цепи сигнала «начало цикла и через элемент задержки - к выходу третьего элемента совпадения, уиравляющий вход которого подключен ко второму выходу триггера режима контроля, второй вход последнего соединен с цепью команды «ввод кода, выход схемы сравнения соединен со входом третьего эле.мента совпадения и

через инвертор - с управляющим входом второго элемента совпадения.

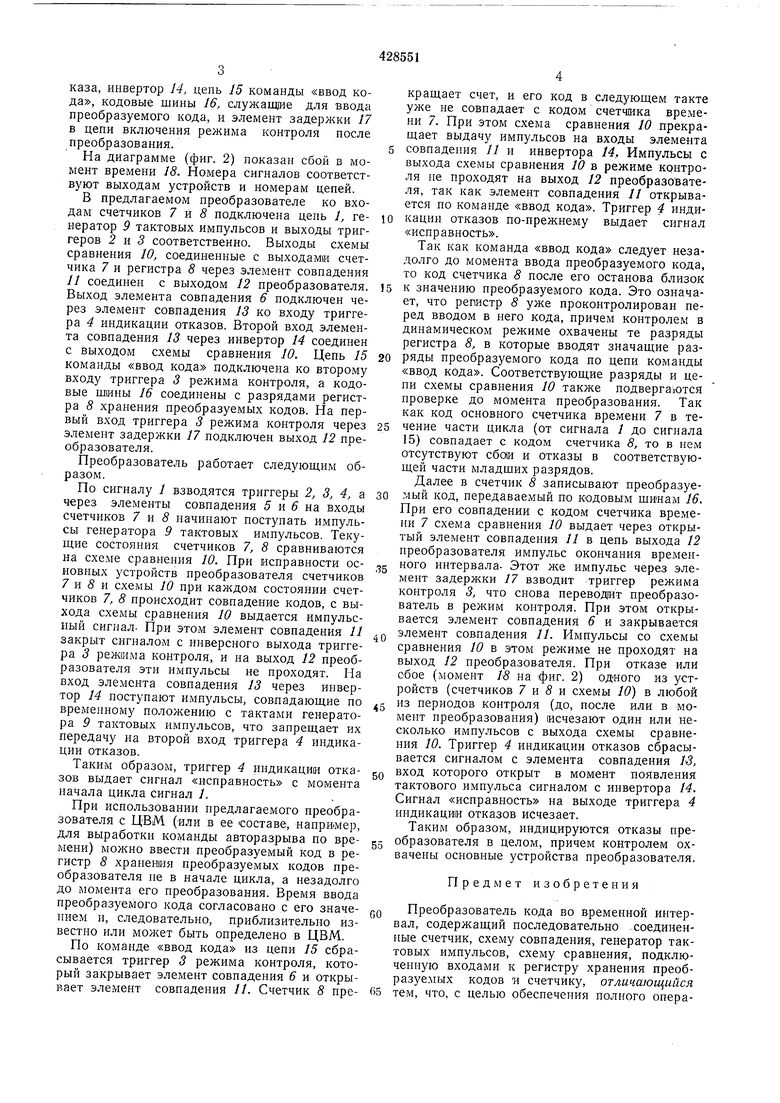

На фиг. 1 показана блок-схема предлагаемого нреобразователя кода во временной интервал; на фиг. 2 - временная диаграмма его

работы.

Предлагаемый преобразователь содержит цепь / сигнала «начало цикла нреобразователя, управляющий триггер 2 счетчика времени, триггер 3 режима контроля, служащий

ДТя управления режимом нреобразователя, триггер 4 индикации отказов, элемент совпадения 5, элемент совпадения 6, служащий для передачи импульсов в режиме контроля, счетчик времени 7, регистр 5 хранения преобразуемых кодов, вынолне1Н Ый в виде счетчика, генератор 9 тактовых импульсов, схему сравнения 10, элемент совпадения 11, служащий для управления выходо. преобразователя, выход 12 преобразователя, элемент совнадеНИН 13, служащий для выработки сигнала отказа, инвертор 14, цепь 15 команды «ввод кода, кодовые шины 16, служащие для ввода преобразуемого кода, и элемент задержки 17 в цепи включения режима контроля после преобразования.

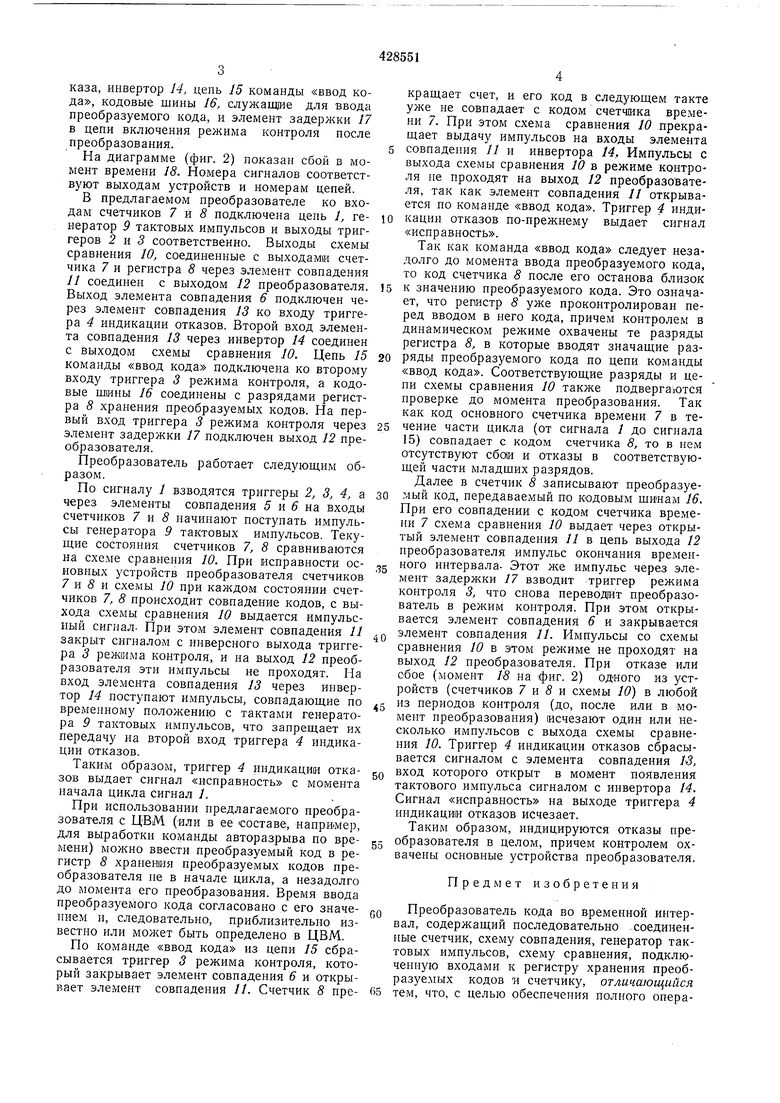

На диаграмме (фиг. 2) показан сбой в момент Бремени 18. Номера сигналов соответствуют выходам устройств и номерам цепей.

В предлагаемом преобразователе ко входам счетчиков 7 и 5 подключена цепь /, генератор 9 тактовых импульсов и выходы триггеров 2 н 3 соответственно. Выходы схемы сравнения 10, соединенные с выходами счетчика 7 и регистра 8 через элемент совпадения Л соединен с выходом 12 преобразователя. Выход элемента совпадения 6 подключен через элемент совпадения 13 ко входу триггера 4 индикации отказов. Второй вход элемента совпадения 13 через инвертор 14 соединен с выходом схемы сравнения 10. Цепь 15 команды «ввод кода подключена ко второму входу триггера 3 режима контроля, а кодовые шины 16 соединены с разрядами регистра 8 хранения преобразуемых кодов. На первый вход триггера 3 режима контроля через элемент задержки 17 подключен выход 12 преобразователя.

Преобразователь работает следующим образом.

По сигналу / взводятся триггеры 2, 3, 4, а через элементы совпадения 5 и 5 на входы счетчиков 7 н 8 начинают поступать импульсы генератора 9 тактовых импульсов. Текущие состояния счетчиков 7, 8 сравниваются на схеме сравнения 10. При исправности основных устройств преобразователя счетчиков 7 и 5 и схемы 10 при каждом состоянии счетчиков 7, 8 происходит совпадение кодов, с выхода схемы сравнения 10 выдается импульсный сигнал- При этом элемент совпадения 11 закрыт сигналом с инверсного выхода триггера 3 режима контроля, и на выход 12 преобразователя эти импульсы не проходят. На вход элемента совпадения 13 через инвертор 14 поступают импульсы, совпадающие по временному положению с тактами генератора 9 тактовых импульсов, что запрещает их передачу на второй вход триггера 4 индикации отказов.

Таким образом, триггер 4 индикации отказов выдает сигнал «исправность с момента начала цикла сигнал /.

При использовании предлагаемого преобразователя с ЦВМ (или в ее составе, например, для выработки команды авторазрыва но времени) можно ввести преобразуемый код в регистр 8 хранения преобразуемых кодов преобразователя не в начале цикла, а незадолго до момента его преобразования. Время ввода преобразуемого кода согласовано с его значением и, следовательно, приблизительно известно нли может быть определено в ЦВМ.

По команде «ввод кода из цепи 15 сбрасывается триггер 3 режима контроля, который закрывает элемент совпадения 6 и открывает элемент совнадения //. Счетчик 8 прекращает счет, и его код в следующем такте уже не совпадает с кодом счетчика времени 7. При этом схема сравнения 10 прекращает выдачу импульсов на входы элемента совпадения // и инвертора М, Импульсы с выхода схемы сравнения 10 в режиме контроля не проходят на выход 12 преобразователя, так как элемент совпадения // открывается но команде «ввод кода. Триггер 4 индикации отказов по-прежнему выдает сигнал «исправность.

Так как команда «ввод кода следует незадолго до момента ввода преобразуемого кода, то код счетчика 8 после его останова близок

к значению преобразуемого кода. Это означает, что репистр 8 уже проконтролирован перед вводом в него кода, нричем контролем в динамическом режиме охвачены те разряды регистра 8, в которые вводят значащие разряды нреобразуемого кода по цепи команды «ввод кода. Соответствующие разряды и цепи схемы сравнения 10 также подвергаются проверке до момента преобразования. Так как код основного счетчика времени 7 в течение части цикла (от сигнала / до сигнала 15) совпадает с кодом счетчика 8, то в нем отсутствуют сбои и отказы в соответствующей части младших разрядов. Далее в счетчик 8 записывают преобразуемый код, передаваемый по кодовым шииам 16. При его совнадении с кодом счетчика времени 7 схема сравнения 10 выдает через открытый элемент совнадения 11 в цепь выхода 12 преобразователя импульс окончания временного интервала. Этот лее импульс через элемент задержки 17 взводит триггер режима контроля 3, что снова перевод1ит преобразователь в режим контроля. При этом открывается элемент совпадения 6 и закрывается

элемент совпадения 11. Импульсы со схемы сравнения 10 в этом режиме не проходят на выход 12 преобразователя. При отказе или сбое (момент 18 на фиг. 2) одного из устройств (счетчиков 7 и 5 и схемы 10) в любой

нз периодов контроля (до, после или в момент преобразования) исчезают один или несколько импульсов с выхода схемы сравнения 10. Триггер 4 индикации отказов сбрасывается сигналом с элемента совпадения ,

вход которого открыт в момент появления

тактового импульса сигналом с инвертора 14.

Сигнал «исправность на выходе триггера 4

индикации отказов исчезает.

Таким образом, индицируются отказы преобразователя в целом, причем контролем охвачены основные устройства преобразователя.

Предмет изобретения

Преобразователь кода во временной интервал, содержащий последовательно соединенные счетчик, схему совпадения, генератор тактовых импульсов, схему сравнения, подключенную входами к регистру хранения преобразуемых кодов и счетчику, отличающийся

тем, что, с целью обеспечения полного оперативного контроля, в него введены элементы совпадения, инвертор и элемент задержки, триггеры контроля и индикации отказов, причем выход первого элемента совпадения, управляющий вход которого подключен к первому выходу триггера режима контроля, соединен со входом регистра хранения преобразуемых кодов и через второй элемент совпадения - со входом триггера индикации отказов, первый вход триггера режима контроля подключен к цепи сигнала «начало цикла и через элемент задержки -- к выходу третьего элемента совпадения, управляющий вход которого подключен ко второму выходу

триггера режима контроля, второй вход последнего соединен с цепью команды «ввод кода, выход схемы сравнения соединен со входом третьего элемента совпадения и через инвертор - с управляющим входом второго

элемента совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода во временной интервал | 1978 |

|

SU720719A1 |

| Устройство для отладки цифровых систем | 1985 |

|

SU1254492A1 |

| ИМИТАТОР ИР-60-500 ДЛЯ ОТЛАДКИ КОРАБЕЛЬНЫХ ЦИФРОВЫХ УПРАВЛЯЮЩИХ СИСТЕМ | 1998 |

|

RU2138846C1 |

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| Устройство для диагностирования логических схем | 1988 |

|

SU1684757A1 |

| Устройство для определения содержания связующего в стеклопластиках | 1984 |

|

SU1265538A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО ГАММА-ПРОФИЛО ГРАФА | 1970 |

|

SU270858A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Устройство для измерения параметров частотных датчиков | 1989 |

|

SU1705757A1 |

12

/J7IIIIIIIIIIII1IIIIIIIIIIII IIIIHIIIIIIIIIIIIIU НИИ 6 Illllllllllllllllllllllll Illllllllllllllini МИШИН

15

I

18

иг г

Даты

1974-05-15—Публикация

1972-01-03—Подача