СЭ ОС 4

1

сд

Изобретение относится к контрольно-измерительной технике и может быт использовано для диагностирования логических кшкросхем и цифровых уст- ройств, построенные на их основе.

Цель изобретения - повышение достоверности контроля за счет возможности контроля переходных процессов объекта контроля в заданном проме- жутке времени.

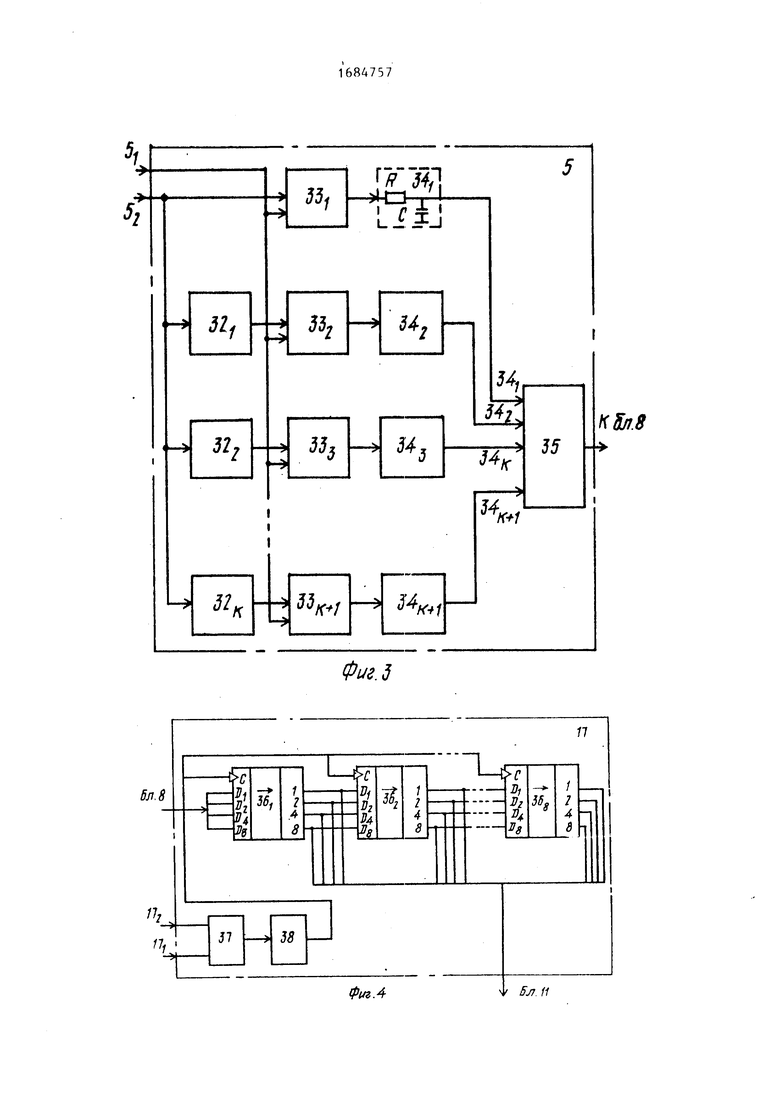

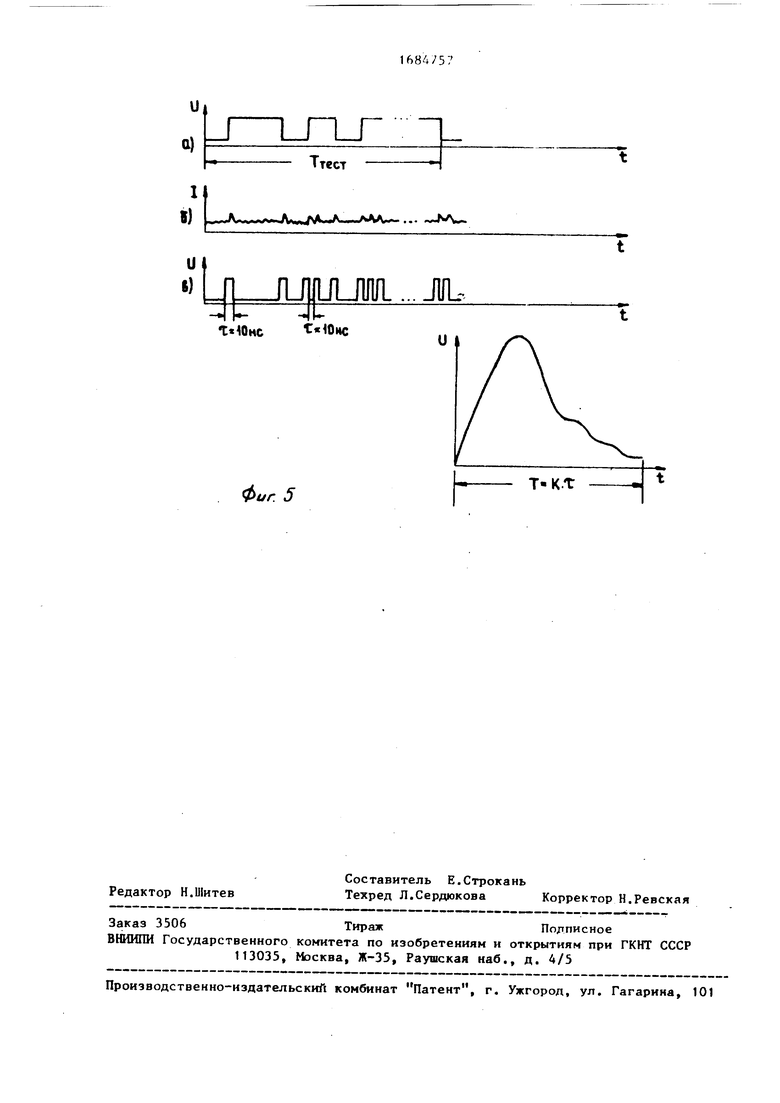

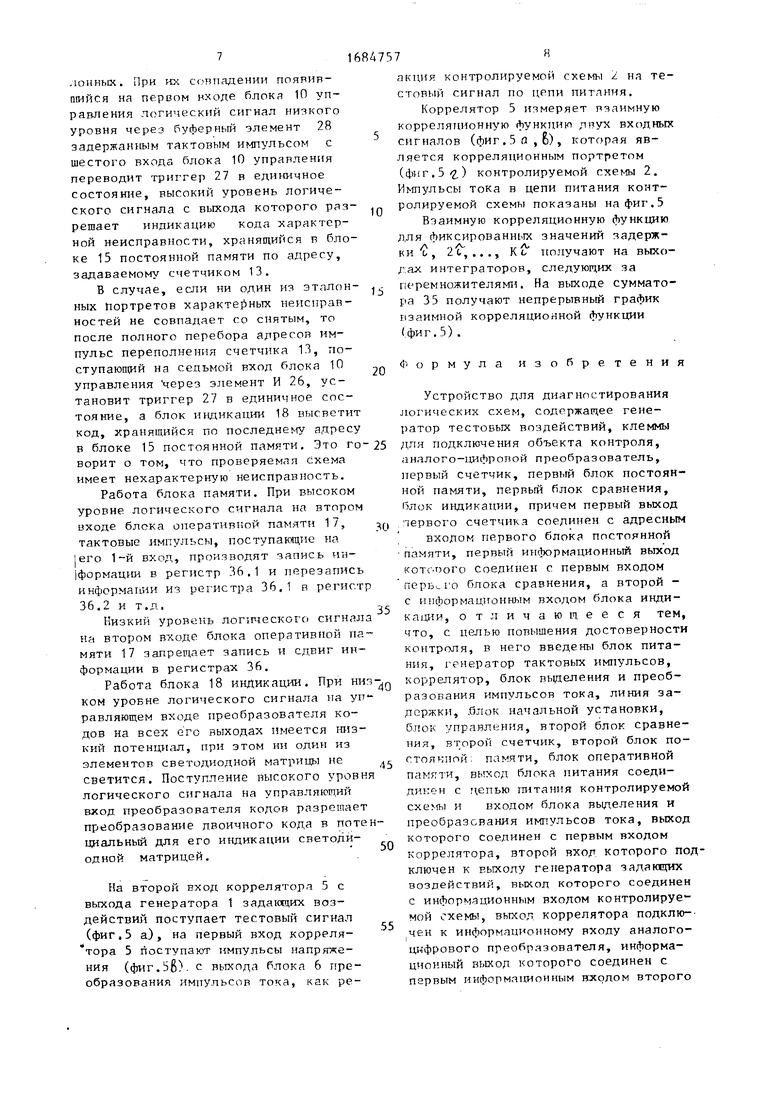

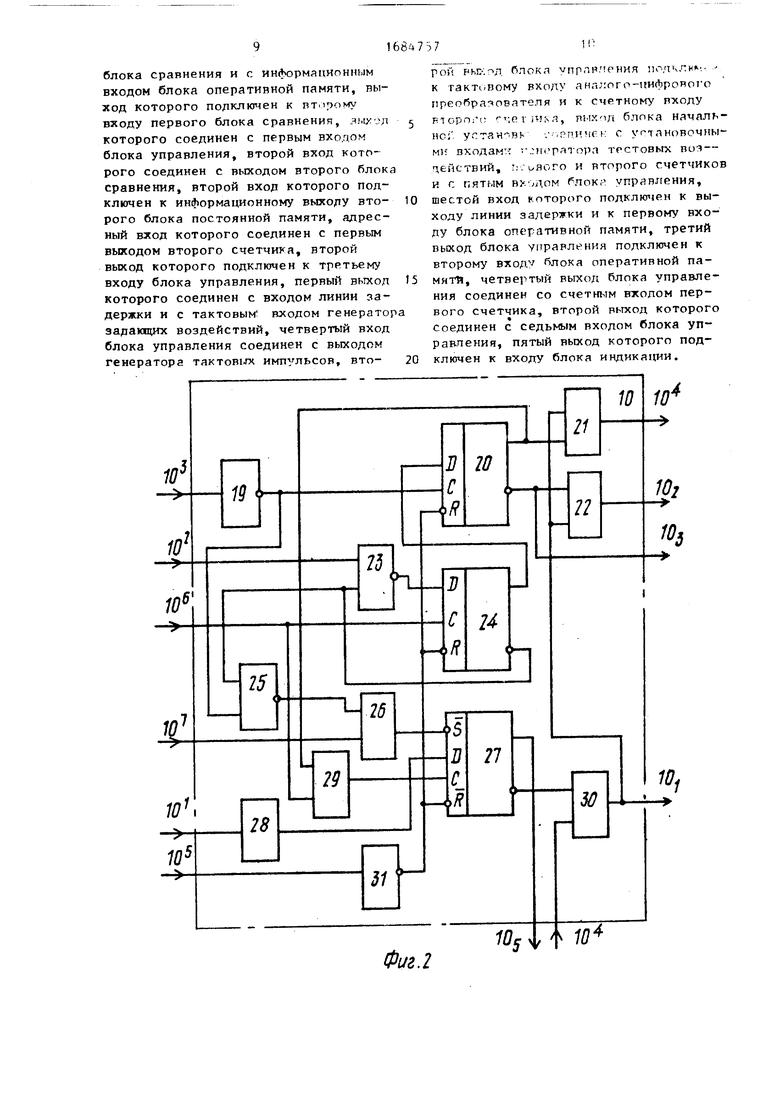

На фиг. 1 приведена блок-схема устройства для диагностирования логических схем; на фиг. 2 - принципиальная схема блока управленияJ на фиг. 3 - блок-схрма коррелятора на фиг. 4 - принципиальная схема блока оперативной памяти , на фиг. 5 - временные диаграммы работы устройства.

Устройство (фиг.1) содержит ге- нератор 1 тестовых воздействий, контролируемую схему 2, блок питания 3, генератор 4 тактовых импульсов, коррелятор 5, блок 6 выделения и преобразования импульсов тока, линию за- держки (ЛЗ) 7, аналого-цифровой преобразователь (АЦП) 8, блок 9 начальной установки, блок 10 управления, первый 11 и второй 12 блоки сравнения, первый 13 и второй 14 счет- чики, первый 15 и второй 16 блоки постоянной памяти, блок 17 оперативной памяти, блок 18 индикации с соответствующими связями.

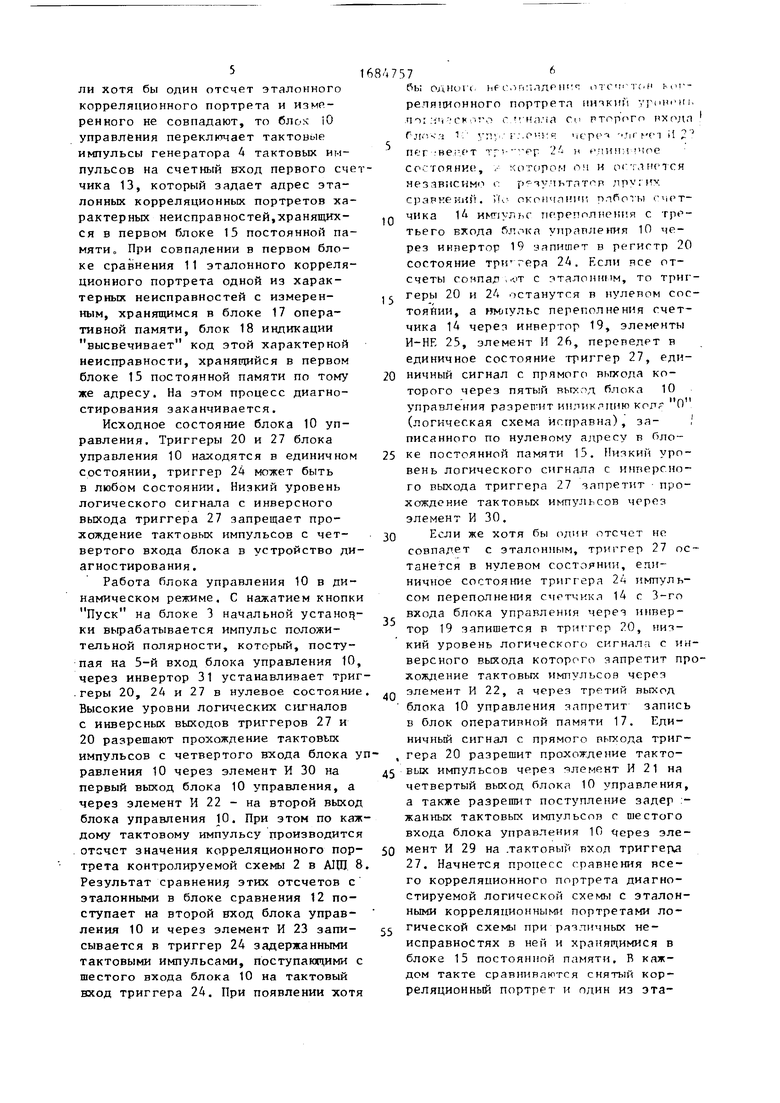

Устройство согласно фиг.2 со- держит первый инвертор 19, триггер 20 установки режима работы устройства, первый элемент И 21, второй элемент И 22, первый элемент И-НЕ 23 D-триггер 24, второй элемент И-НЕ . 25, третий элемент И 26, триггер 27 включения блока индикации, буферный элемент 28, четвертый элемент И 29, пятый элемент И 30, второй инвертор 31 с соответствующими связями.

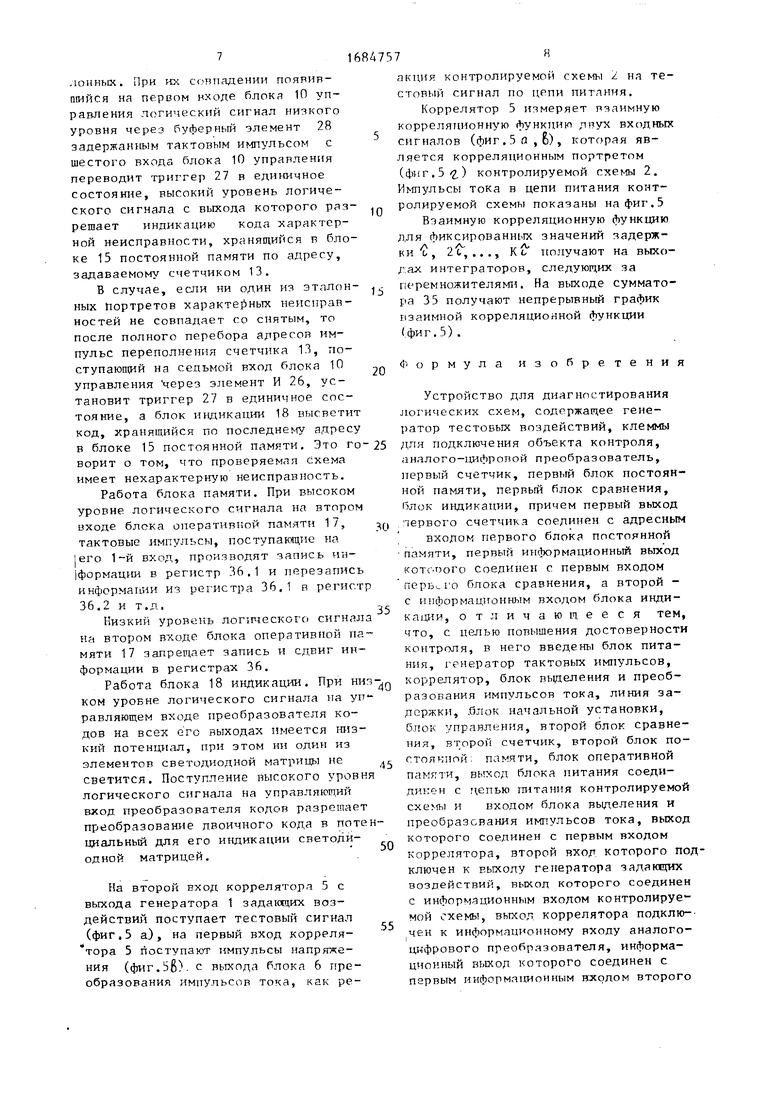

Устройство согласно фиг.З содержит К дискретных линий задержки (32.1, 32.2-32.К), перемножители (33.1, 33.2...33.К + 1), интеграторы (34.1, 34.2...34.К-Н), сумматор 35, с соответствующими связями..

Дискретность задержки Л с выбирается из условия u t , где

(jFf

FT - тактовая частота.

Интеграторы выполнены на RC-це-

почках.

Устройство согласно фиг. 4

содержит восемь регистров 36.1,

36.2...36.8, элемент И 37, буферный элемент 38, с соответствующими связями .

Блок индикации 18 включает в себя формирователь кодов, светодиодную матрицу и элементы согласования, с соответствующими связями.

Устройство работает следующим образом.

Тестовый сигнал с выхода генератора 1 тестовых воздействий поступает на информационный вход контролируемой схемы 2, в цепи питания которой появляются импульсы тока, как реакция на входной тестовый сигнал. Эти импульсы выделяются, усиливаются преобразуются в импульсы напряжения блоком 6 выделения и преобразования импульсов тока и поступают на первый вход коррелятора 5, на второй вход которого поступает тестовый сигнал с выхода генератора 1 тестовых воздействий. Генерирование тестового сигнала с заданными характеристиками осуществляется с помощью сдвигового регистра с обратными связями, позволяющего получать периодическую псевдослучайную последовательность, у которой автокорреляционная функция близка к Ј -функции. Коррелятор 5 измеряет взаимную корреляционную функ;щю между сигналами на его первом и втором входах, которая является корреляционным портретом контролируемой схемы 2. АЦП 8 преобразует сигнал на выходе коррелятора (корреляционный портрет) в цифровую форму, которая запоминается в блоке 17 оперативной памяти. Во втором блоке сравнения 12 отсчеты корреляционного портрета контролируемой схемы сравниваются с отсчетами эталонного корреляционного пор- трета, которые хранятся во втором блоке 16 постоянной памяти в цифровой форме. Второй счетчик 14 в соответствии с поступающими на его счетный вход тактовыми импульсами задает адреса, по которым хранятся отсчеты эталонного корреляционного портрета во втором блоке 16 постоянной памяти В случае, если все отсчеты эталонного корреляционного портрета и измеренного корреляционного портрета контролируемой схемы совпадают, то в блоке 18 индикации горит цифра О. На этом диагностирование заканчивается. Еели хотя бы один отсчет эталонного корреляционного портрета и изморенного не совпадают, то блок 10 управления переключает тактовые импульсы генератора 4 тактовых импульсов на счетный вход первого счетчика 13, который задает адрес эталонных корреляционных портретов характерных неисправностей,хранящихся в первом блоке 15 постоянной памяти „ При совпадении в первом блоке сравнения 11 эталонного корреляционного портрета одной из характерных неисправностей с измеренным, хранящимся в блоке 17 оперативной памяти, блок 18 индикации высвечивает код этой характерной неисправности, хранящийся в первом блоке 15 постоянной памяти по тому же адресу. На этом процесс диагностирования заканчивается.

Исходное состояние блока 10 управления. Триггеры 20 и 27 блока управления 10 находятся в единичном состоянии, триггер 24 может быть в любом состоянии. Низкий уровень логического сигнала с инверсного выхода триггера 27 запрещает прохождение тактовых импульсов с четвертого входа блока в устройство диагностирования .

Работа блока управления 10 в динамическом режиме. С нажатием кнопки Пуск на блоке 3 начальной установ,- ки вырабатывается импульс положительной полярности, который, поступая на 5-й вход блока управления 10, через инвертор 31 устанавливает триггеры 20, 24 и 27 в нулевое состояние Высокие уровни логических сигналов с инверсных выходов триггеров 27 и 20 разрешают прохождение тактовых импульсов с четвертого входа блока уравления 10 через элемент И 30 на первый выход блока 10 управления, а через элемент И 22 - на второй выход блока управления 10. При этом по каждому тактовому импульсу производится отсчет значения корреляционного портрета контролируемой схемы 2 в А1Щ 8 Результат сравнения этих отсчетов с эталонными в блоке сравнения 12 поступает на второй вход блока управления 10 и через элемент И 23 записывается в триггер 24 задержанными тактовыми импульсами, поступающими с шестого входа блока 10 на тактовый вход триггера 24. При появлении хотя

684757 бы

10

20

25

30

35

40

45

50

55

г к

mr

Гличч -TV

ntr -BerfT т; со. тоянке, , независимо i сравнений. П

OJI,HUI hf c.-jtviaAPHi f m о ч1 ir.M юг- репяционного портрета низкий угпшмм, спа си второго входа

, ЧСРГЗ - К ГСП {

-РГ 2 - н 1 чое

О ГОЛОМ ОЧ И О Г ЛНС10Я

Р зучьтлТ р ;ipv;i v окончании тРоты чст- чнка 14 импульс переполнения с третьего входа блока управления 10 через инвертор 19 запишет в регистр 20 состояние трнтгера 24. Если все отсчеты сонпад ..от с тталонннм, то триг- с геры 20 и 24 останутся в нулевом состоянии, а нмлульс переполнения счет- чика 14 через инвертор 19, элементы И-НЕ 25, элемент И 26, переведет в единичное состояние триггер 27, единичный сигнал с прямого выхода которого через пятый выход блока Ю управления разреп-ит индикацию код О (логическая схема исправна), за- , писанного по нулевому адресу в блоке постоянной памяти 15. Низкий уровень логического сигнала с инверсного выхода триггера 27 запретит прохождение тактовых импульсов через элемент И 30.

Если же хотя бы один отсчет не совпадет с эталонным, триггер 27 останется в нулевом состоянии, единичное состояние триггера 24 импульсом переполнения счетчика 14 с 3-го входа блока управления через инвертор 19 запишется в триггер 0, низкий уровень логического сигнала с инверсного выхода которого запретит прохождение тактовых импульсов через элемент И 22, а через третий выход блока 10 управления запретит запись в блок оперативной памяти 17. Единичный сигнал с прямого выхода триггера 20 разрешит прохождение тактовых импульсов через -элемент И 21 на четвертый выход блока 10 управления, а также разрешит поступление задер - жанных тактовых импульсов с шестого входа блока управления 10 через элемент И 29 на .тактовый вход триггера 27. Начнется процесс сравнения всего корреляционного портрета диагностируемой логической схемы с эталонными корреляционными портретами логической схемы при различных неисправностях в ней и хранящимися в блоке 15 постоянной памяти. В каждом такте сравниваются снятый корреляционный портрет и один из эта

лонных. При их совпадении появившийся на первом входе блока 10 управления логический сигнал низкого уровня через буферный элемент 28 задержанным тактовым импульсом с шестого входа блока 10 управления переводит триггер 27 в единичное состояние, высокий уровень логического сигнала с выхода которого разрешает индикацию кода характерной неисправности, хранящийся п блоке 15 постоянной памяти по адресу, задаваемому счетчиком 13.

В случае, если ни один из эталонных портретов характерных неисправностей не совпадает го снятым, то после полного перебора адресов импульс переполнения счетчика 13, поступающий на седьмой вход блока Ю управления через элемент И 26, установит триггер 27 в единичное состояние, а блок индикации 18 высветит код, хранящийся по последнему адресу в блоке 15 постоянной памяти. Это го ворит о том, что проверяемая схема имеет нехарактерную неисправность.

Работа блока памяти. При высоком уровне логического сигнала на втором входе блока оперативной памяти 17, тактовые импульсы, поступающие на |его 1-й вход, производят запись информации в регистр 36.1 и перезапись информации из регистра 36.1 в регист

36.2 и т.л,

3

Низкий уровень логического сигнала на втором входе блока оперативной памяти 17 запрещает запись и сдвиг информации в регистрах 36.

Работа блока 18 индикации. При нит ком уровне логического сигнала на управляющем входе преобразователя кодов на всех его выходах имеется низкий потенциал, при этом ни один из элементов светодиодной матрицы не светится. Поступление высокого уровня логического сигнала на управляющий вход преобразователя кодов разрешает преобразование двоичного кода в потенциальный для его индикации светодиодной матрицей.

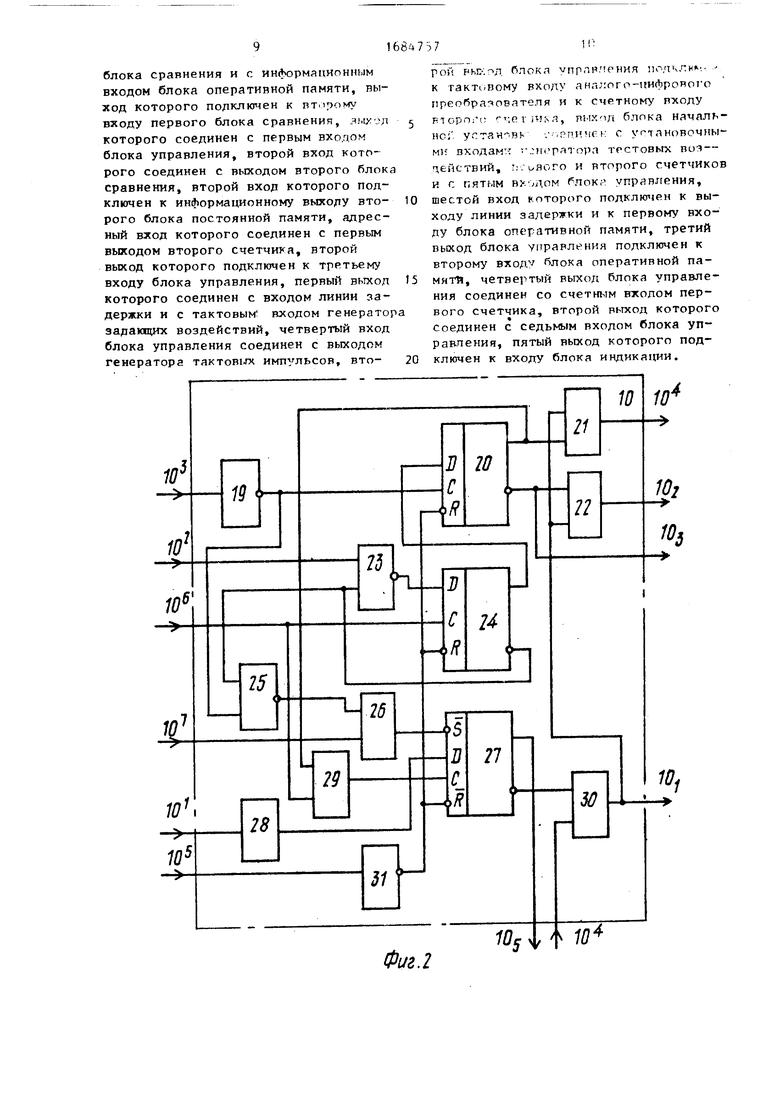

На второй вход коррелятора 5 с выхода генератора 1 задающих воздействий поступает тестовый сигнал (фиг.5 а), на первый вход коррелятора 5 поступают импульсы напряжения (фиг.58) с выхода блока 6 преобразования импульсов тока, как ре5

0

i

5

0

0

5

д 0

акция контролируемой схемы z на тестовый сигнал по цепи питания.

Коррелятор 5 измеряет взаимную корреляционную функцию япух входных сигналов (фиг.5fl,Б), которая является корреляционным портретом (фиг..) контролируемой схемы 2. Импульсы тока в цепи питания контролируемой схемы показаны на фиг.5

Взаимную корреляционную функцию лля фиксированных значений задержки /, 2 с,..., К L. получают на выходах интеграторов, следующих за перемножителями. На выходе сумматора 35 получают непрерывный график взаимной корреляционной функции (фиг.5).

Формула изобретения

Устройство для диагностирования логических схем, содержащее генератор тестовых воздействий, клеммы для подключения объекта контроля, .аналого-цифровой преобразователь, первый счетчик, первый блок постоянной памяти, первый блок сравнения, блок индикации, причем первый выход первого счетчика соединен с адресным

входом первого блока постоянной памяти, первый информационный выход кот гзого соединен с первым входом бпока сравнения, а второй - с информационным входом блока индикации, отличающееся тем, что, с целью повышения достоверности контроля, в него введены блок питания, генератор тактовых импульсов, коррелятор, блок выделения и преобразования импульсов тока, линия задержки, .блок начальной установки, бнок /правления, второй блок сравнения, второй счетчик, второй блок постоянной памяти, блок оперативной памяти, выход блока питания соеди- дикен с цепью питания контролируемой схемы и входом блока выделения и преобразования импульсов тока, выход которого соединен с первым входом коррелятора, второй вход которого подключен к выходу генератора задающих воздействий, выход которого соединен с информационным входом контролируемой схемы, выхогп коррелятора подключен к информационному входу аналого- цифрового преобразователя, информационный выход которого соединен с первым информационным вводом второго

блока сравнения и с информационным входом блока оперативной памяти, выход которого подключен к второму входу первого блока сравнения, дм/од которого соединен с первым входом блока управления, второй вход которого соединен с выходом второго блок сравнения, второй вход которого подключен к информационному выходу вто- рого блока постоянной памяти, адресный вход которого соединен с первым выходом второго счетчика, второй выход которого подключен к третьему входу блока управления, первый выход которого соединен с входом линии задержки и с тактовым1 входом генератор задающих воздействий, четвертый вход блока управления соединен с выходом генератора тактовых импульсов, вто-

РОИ PhE-.-VI бЛОКа vnp,lHrtPHHH ПГДЧЛН J

к тактовому входу аналого-цифрового преобразователя и к счетному входу Fiopn.-r -.eiiMsn, m.iX Vi блока началь- HOI угтач-.вк . -РПИЧГЬ с установочными входам -: орл тестовых вот - действий, : яого и второго счетчиков и с пятым вэ-одом блок; vnpaBJieHHH, шестой вход которого подключен к выходу линии задержки и к первому входу блока оперативной памяти, третий выход блока управления подключен к второму входлг блока оперативной памяти, четвертый выход блока управления соединен со счетным входом первого счетчика, второй выход которого соединен с седьмым входом блока управления, пятый выход которого подключен к входу блока индикации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ контроля логических устройств | 1989 |

|

SU1709256A1 |

| Устройство диагностирования электронной аппаратуры | 1990 |

|

SU1837244A1 |

| Устройство для непрерывного диагностирования линейных динамических систем | 1988 |

|

SU1624454A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1345199A2 |

| Устройство для контроля логических блоков | 1984 |

|

SU1223234A1 |

| Способ контроля технического состояния цифровых блоков | 1988 |

|

SU1552138A1 |

| Устройство для контроля линейных динамических объектов | 1990 |

|

SU1795422A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для контроля адресных цепей боков памяти | 1985 |

|

SU1274007A1 |

Фиг.З

а)

U

Ттест

JUIIUUimi... JL,

1

I«WHC 1«Юис

Фиг 5

| Контроль устройств на интегральных схемах/Под ред.Б.П.Креден- цера, Киев.: Т986, с.87-88, рис.22(б) | |||

| Устройство для контроля логических схем | 1985 |

|

SU1297060A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-10-15—Публикация

1988-12-22—Подача