1327107

Устройство содержит счетчик 1 адреса, блок 2 памяти, блок 5 управления, генератор 6 импульсов, два элемента И 14 и 15, дешифратор 3 команд, дешифратор 12 контактов 5 блок 9 индикации, блок 7 синхронизации, счетчик , 8 тестовых наборов, программируемый формирователь 4 серий и myльcoв5 элемент 10 сложения по модулю дна, переключатель 1 и программируемые узлы 13,-13.п согласования по числу II контактов объекта контролЯо Уст 1

Изобретение относится к вычислительной цифровой технике и может быт использовано для контроля функциони рования логических блоков ЭВМ,

Целью изобретения является расширение области применения за счет расширения класса контролируемь Х блоков ..

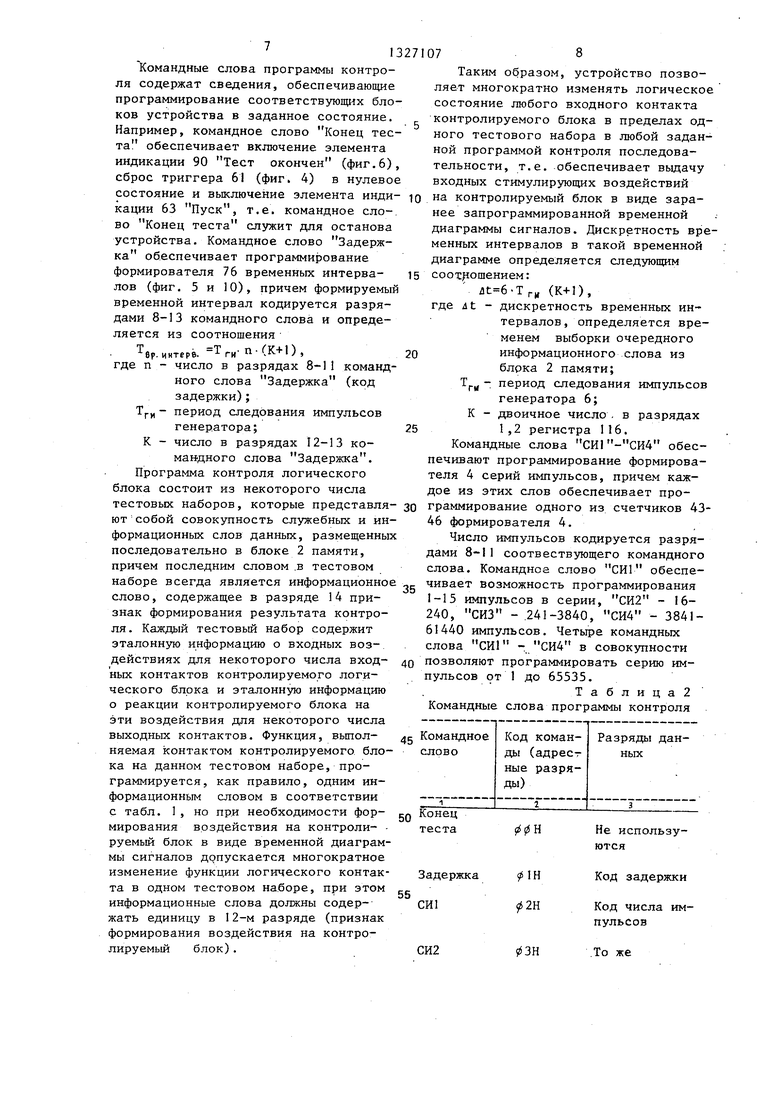

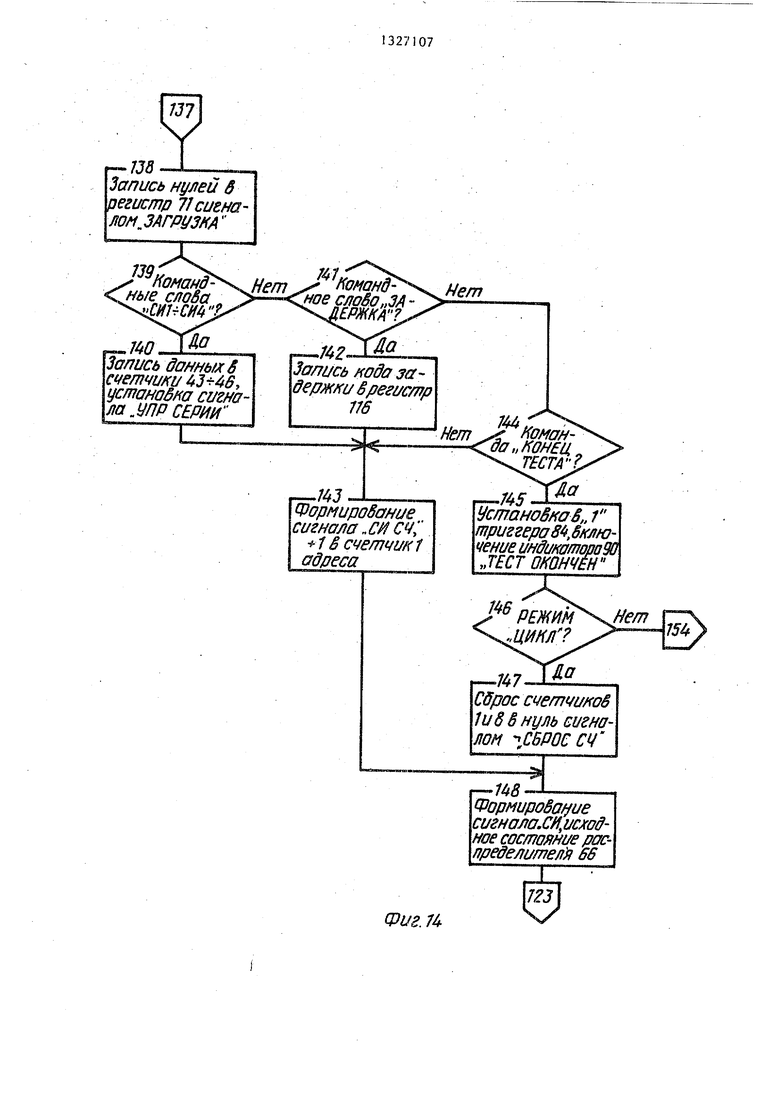

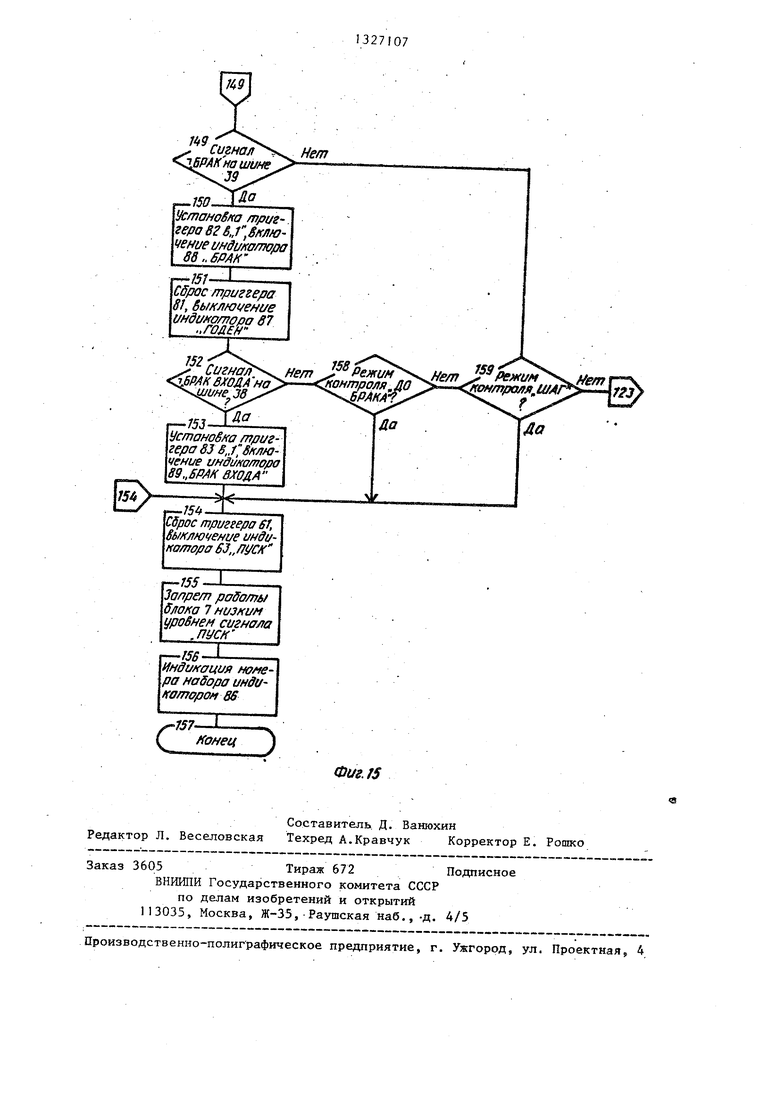

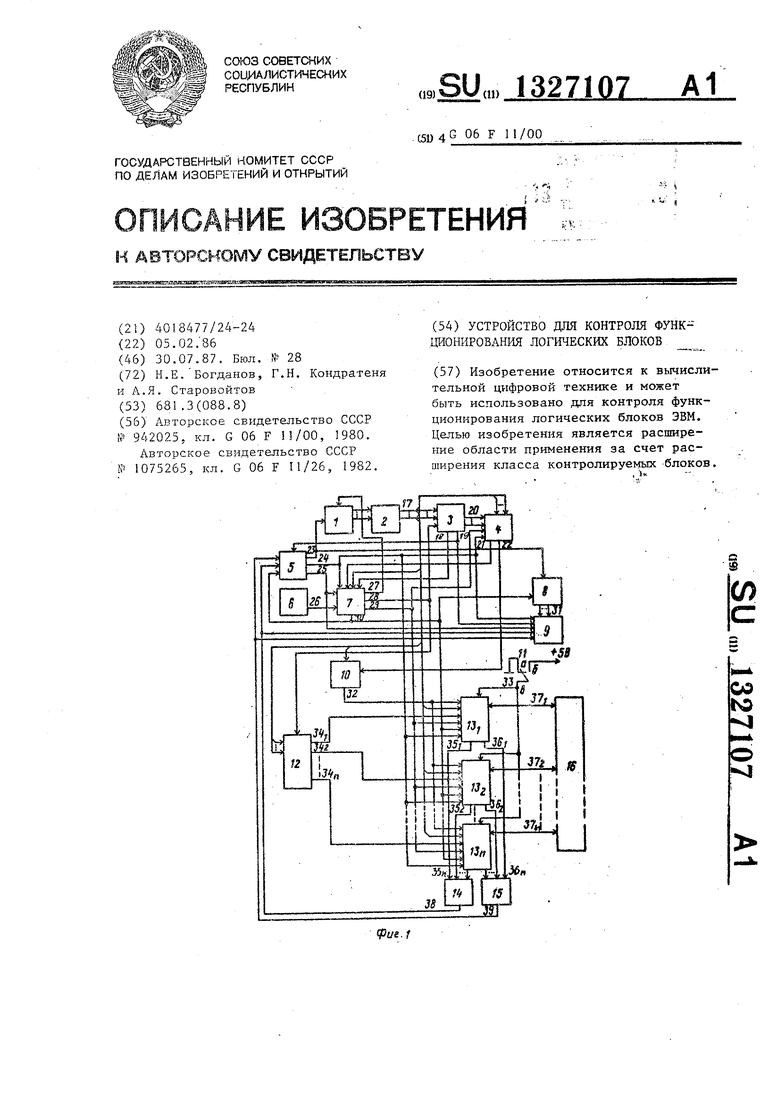

На фиг, 1 представлена структурная схема устройства д,пя контроля функционирования логических блоков; на фиг,.-2 - схема дешифратора команд на фиг. 3 - схема програ1 №1ируемого формирователя импульсов серии; на фиг, 4 - схема блока управления; на фиг,5 - схема блока синхронизации; на фиг, б - схема бло.ка индикации; на фиг.7 - схема дешифратора контактов; на фиг, 8 - схема программируе- ,мого узла согласования; на фиг, 9 - схема распределителя г-гмпульсов блока синхронизации; на фиг, Ш - схема программируемого формирователя временных интервалов; на фиг, 1 - временные диаграммы сигналов распределителя импульсов и программируемого формирователя временных интервалов блока синхронизации; на фиг, 12-i5 - схема алгоритма устройства для контроля функционирования логических блоков.

Устройство для контроля функционирования логических блоков (фиг. I) содержит счетчик 1 адреса, блок 2 па мяти, дешифратор 3 команд, программируемый формирователь 4 серий импульсов, блок 5 управления, генератор 6 импульсов, блок 7 синхронизации, счетчик 8 тестовых наборов, блок 9

ройство для контроля функционирования логических блоков обеспечивает вйдачу .нормированных серий импульсов на заданные контакты объекта контроля, койтроль задержек в нем, формирование тестовых воздействий в соответствии с временными диаграммами сигналов, контроль двухуровневой ло-. гики (ТТЛ-ЭСЛ), контроль двунаправленных интерфейсных приемопередатчи- ков, шаговый и циклический контроль. 4 3, п. ф-лы, 15 ил , 2 табл,

индикации, элемент О сложения по модулю дв-а, переключатель 11, дешифратор 12 контактов, программируемые узлы 13,,, 13f, согласования по числу контактов объекта контроля, два элемента И 14 и 15, контролируемый блок.16,

На фиг, I также обозначены выходная шина 17 блока памяти, второй 18 и первый 19 выходы дешифратора 3 команд, группа 20 выходов дешифратора 3 команд, первый 21 и второй 22 выходы программируемого формирователя серий импульсов, первьй, третий 23- 25 выходы бло.ка управления, выход 26 генератора импульсов, первый - четвертый 27-30 выходы блока синхронизации, группа 31 выходов счетчика тестовых наборов, выход 32 элемента по модулю два, выход 33 пе- ректаочающего контакта переключатачя, выходы 34,|-34| дешифратора, контактов по числу контактов объекта контроля, g выходы . Брак входного контакта программируемых узлов согласования, выходы 36,|-36 Брак контакта программируемых узлов согласования, входы-вьрсоды 37,-37 программируемых узлов согласования, выход 38 первого элемента И, выход 39 второго элемента И,.

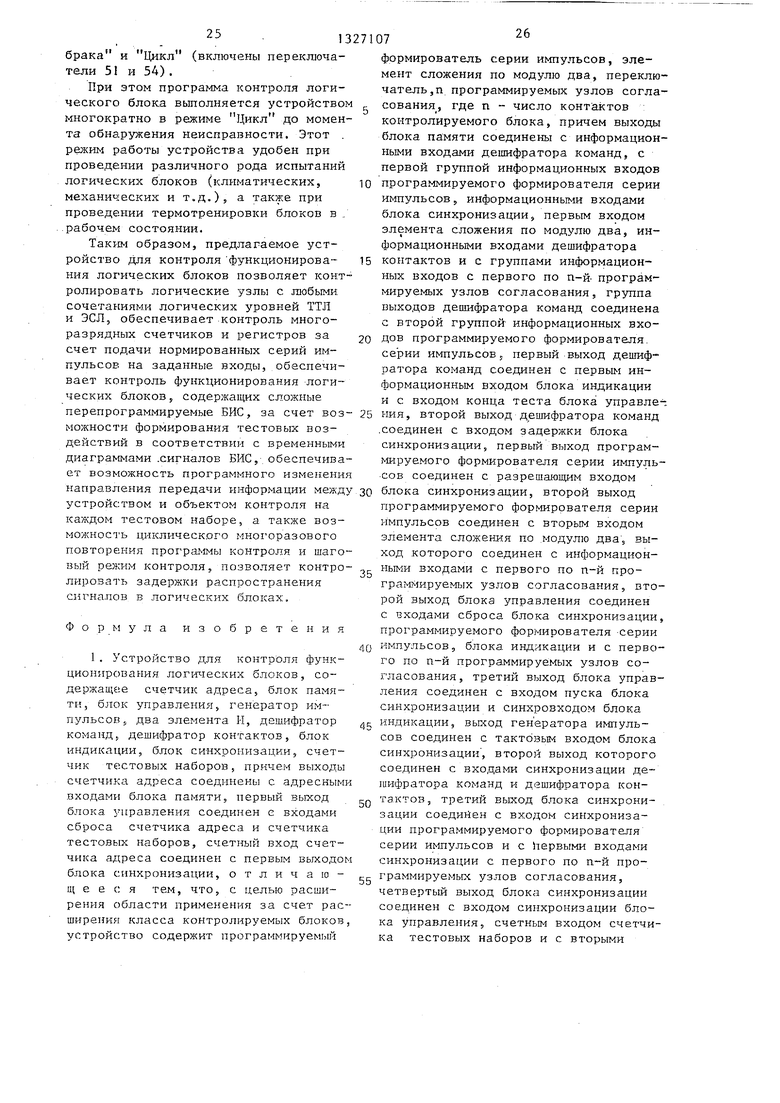

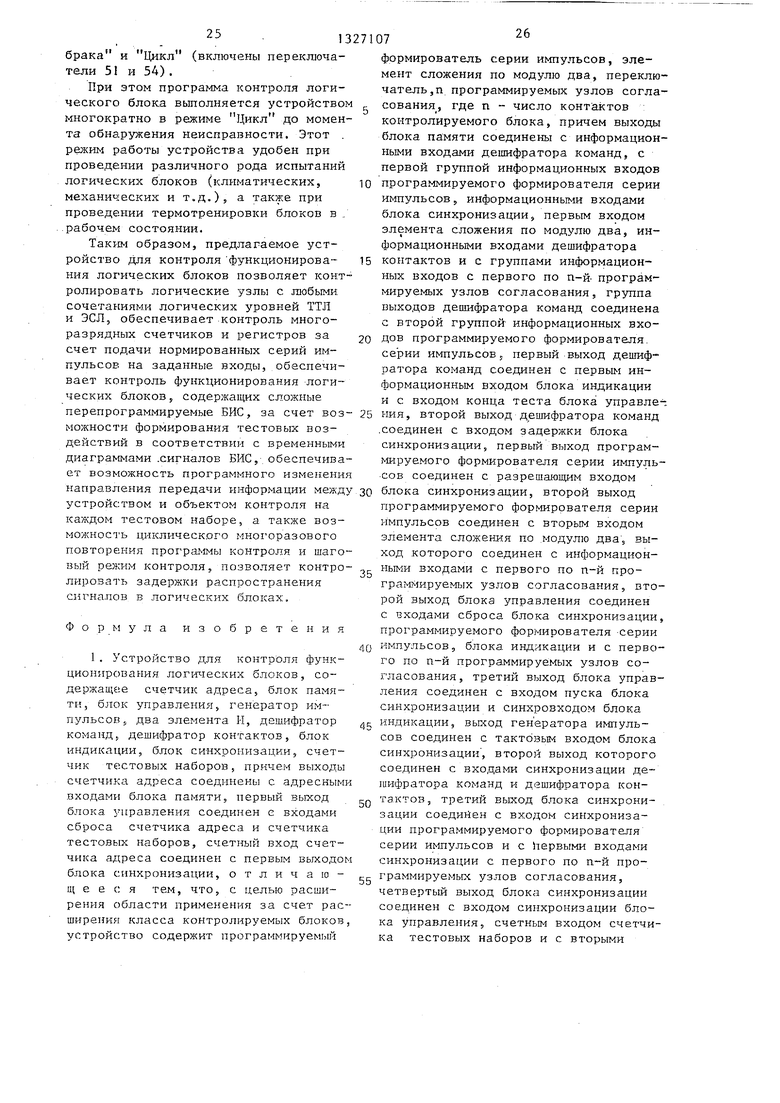

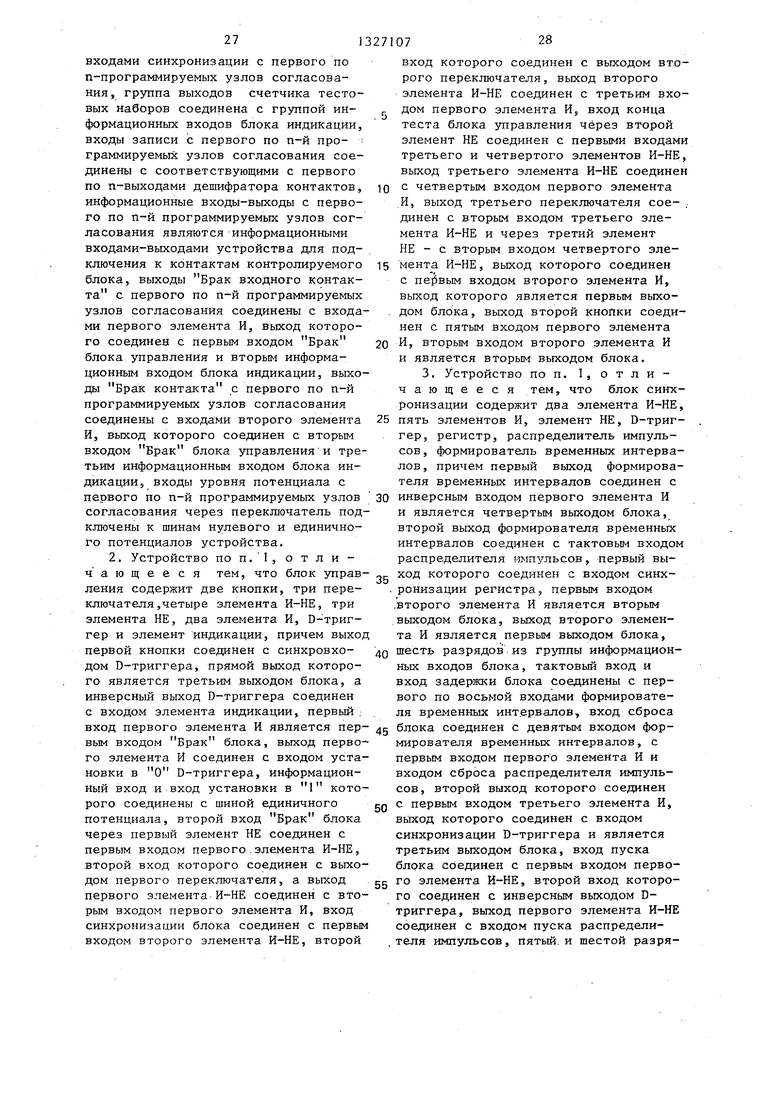

Дешифратор 3 команд (фиг, 2) содержит элемент Й-НЕ 40, дешифратор 4 двоичного кода 6 (позиционный), Программируемый формирователь 4 импульсов серии (фиг, 3) содержит элемент И-НЕ 42, двоичные четырехразрядные счетчики 43-46, счетный триггер 47, элемент ИЛИ 48.

0

31

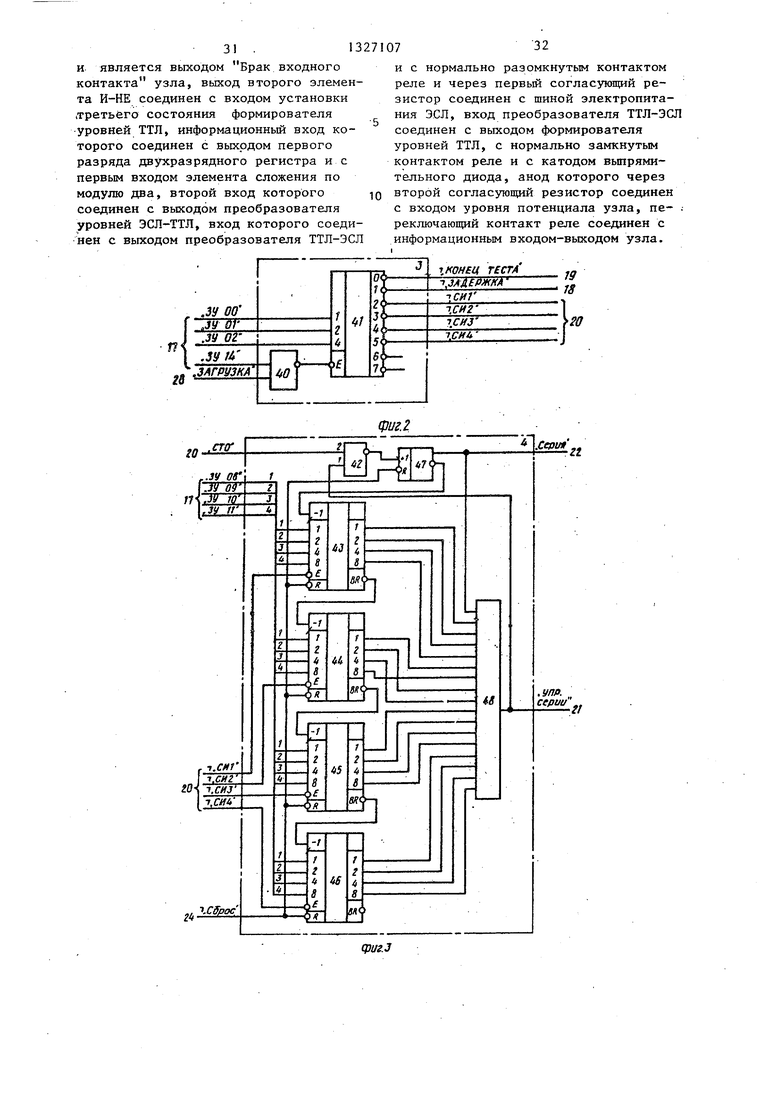

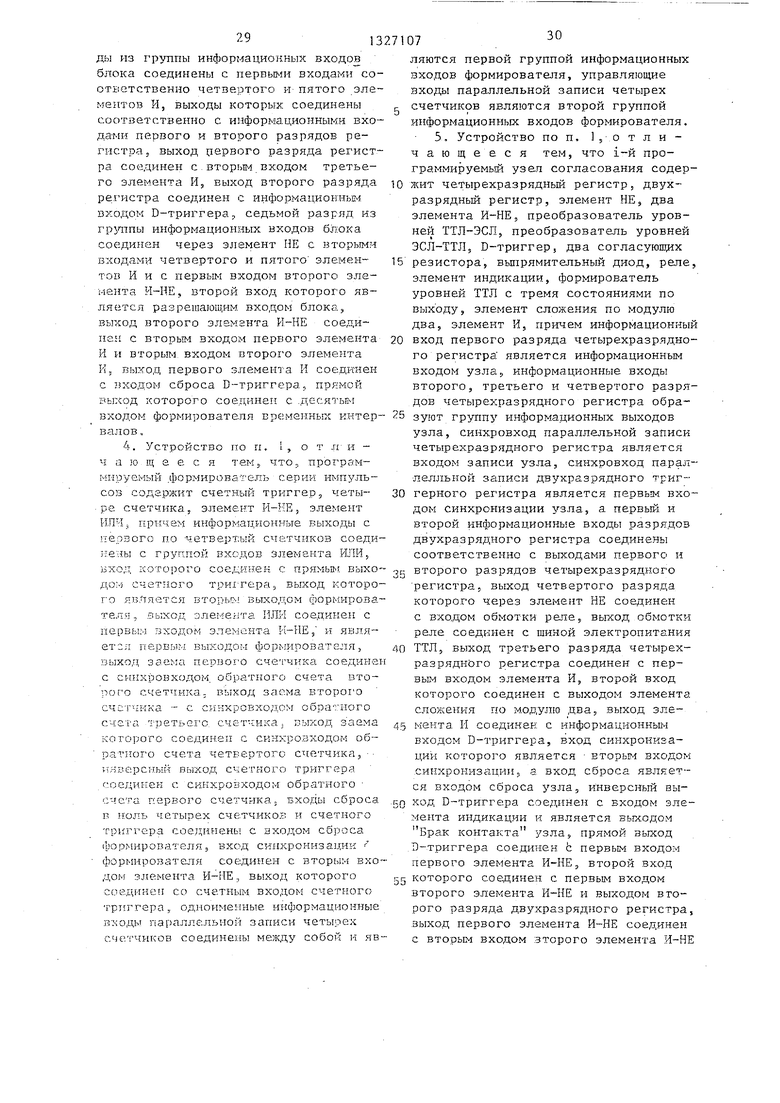

Блок 5 управления (фиг. 4) содержит первую кнопку 49, первый элемент НЕ 50 первый 51 и второй 52 переключатели, второй элемент НЕ 53, третий переключатель 54, вторую кнопку 55, первый - третий 56-58 элементы И-НЕ, первый элемент И 59, третий элемент НЕ 60, D-триггер 61, четвертый элемент И-НЕ 62, элемент 63 индикации, второй элемент И 64.

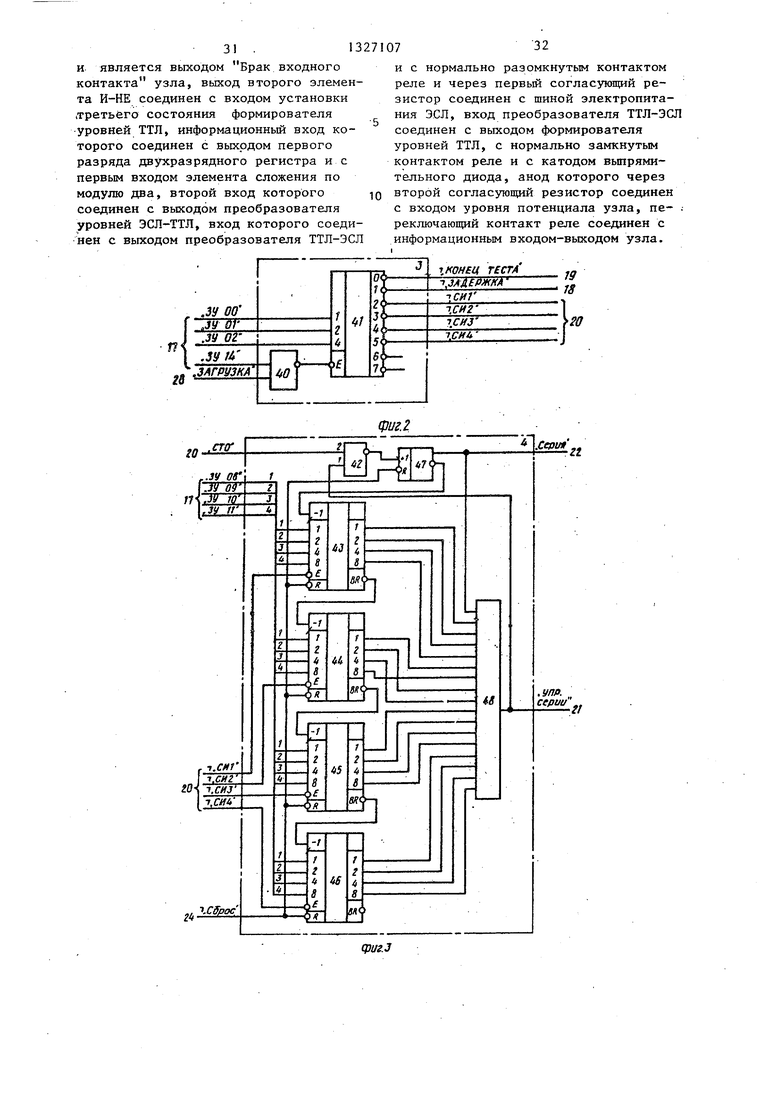

Блок 7 синхрониэации (.фиг. 5) содержит первый элемент И-НЕ 65, распределитель 66 импульсов, четвертый 67 и пятый 68 элементы И-НЕ, элемент НЕ 69, второй элемент И-НЕ 70, регистр 71, первый элемент И 72, второй 73 и третий 74 элементы И, D- триггер 75, программируемый формирователь временных интервалов 76.

На фиг. 5 обозначены вход 77 пуска распределителя импульсов, второй выход 78 распределителя импульсов, прямой выход 79 D-триггера, второй выход 80 формирователя временных ин тервалов.

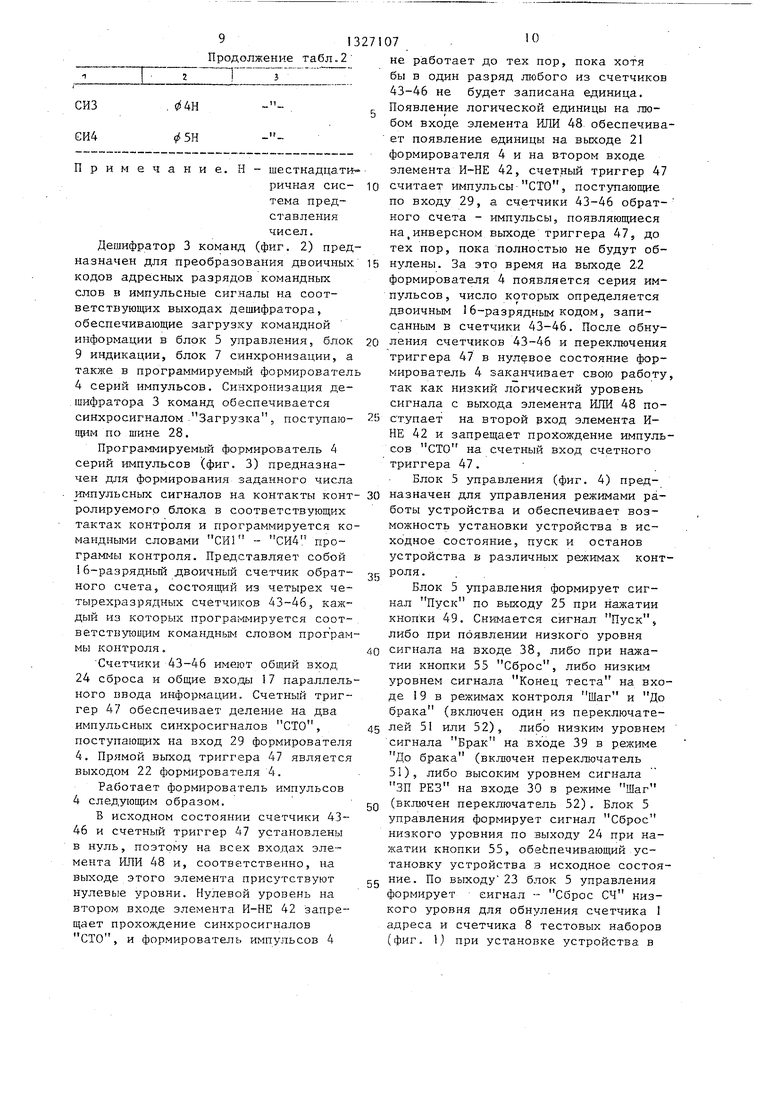

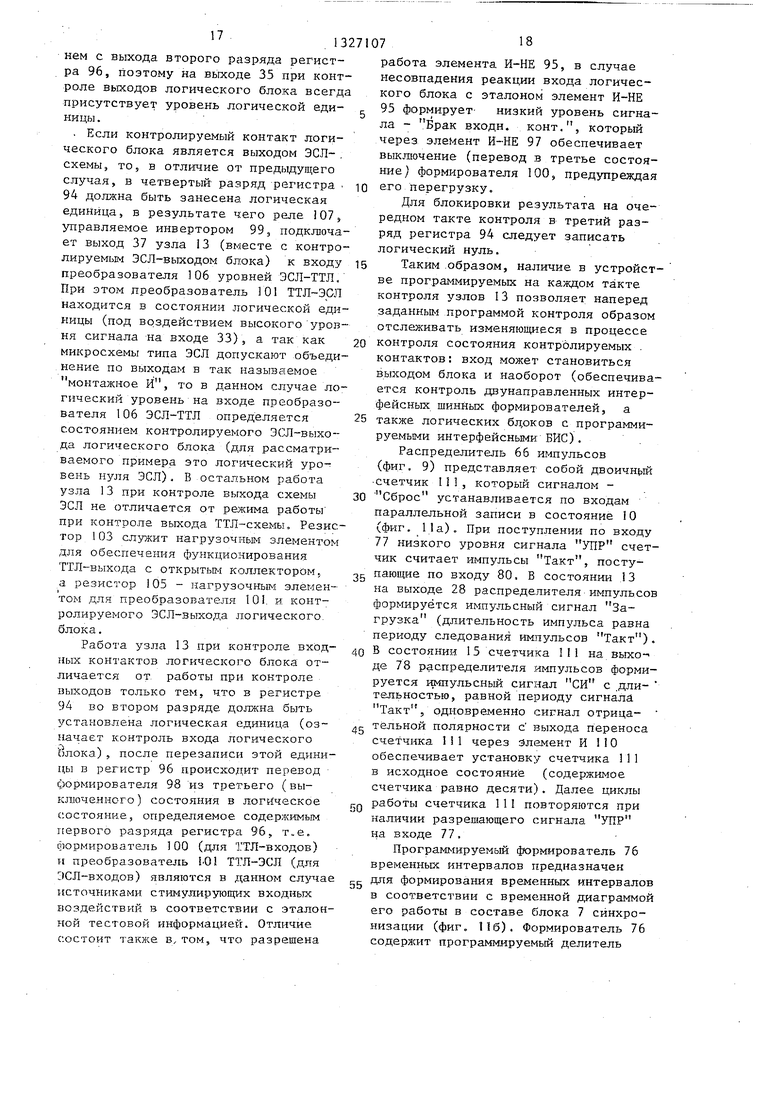

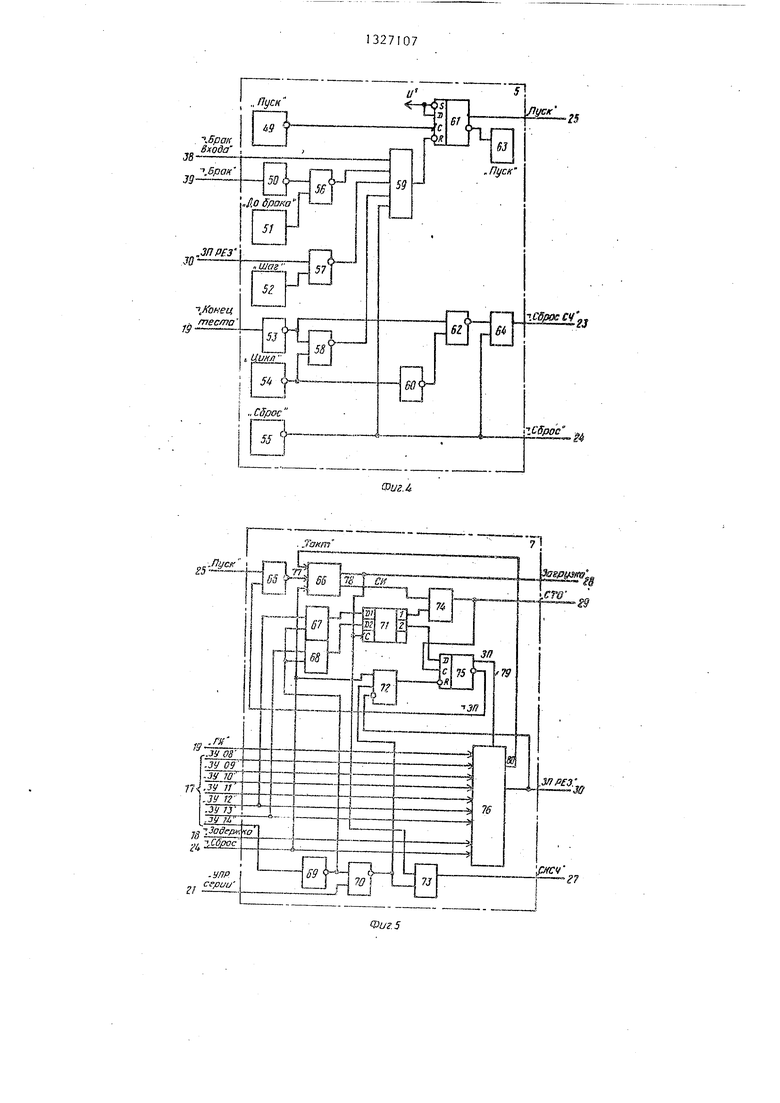

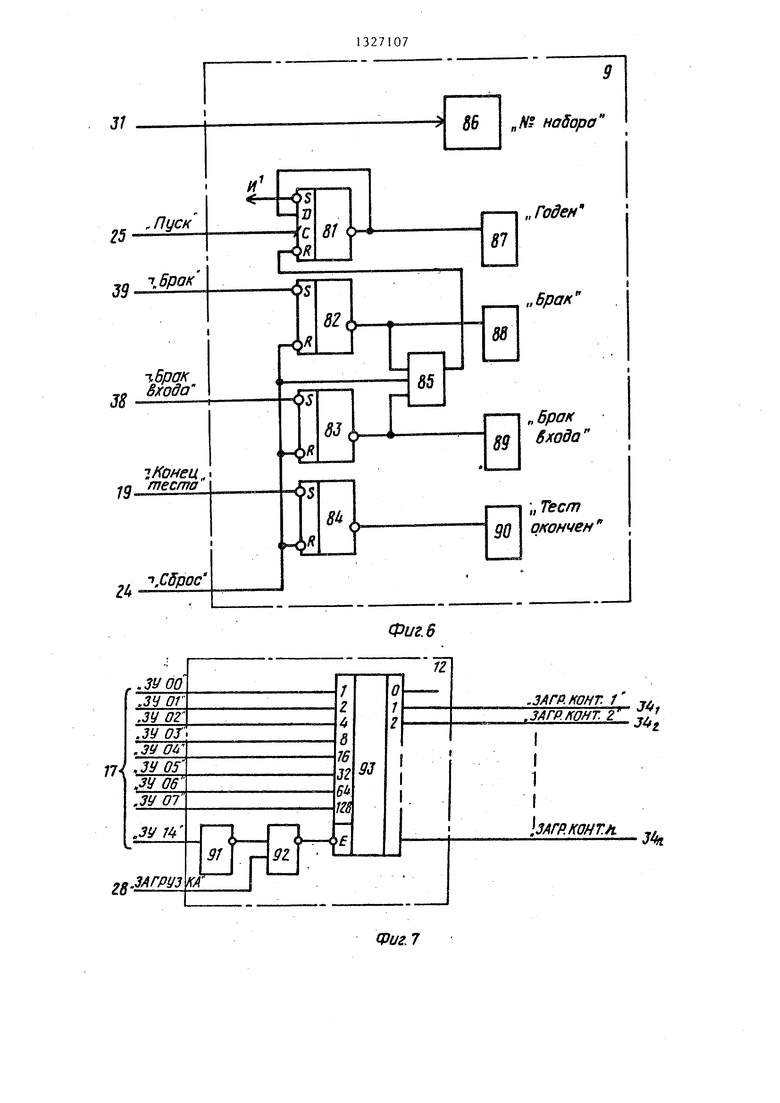

Блок 9 индикации (фиг. 6) содержит D-триггер 81, RS-триггеры 82-84, элемент И 85, цифровой индикатор 86, элементы 87-90 индикации.

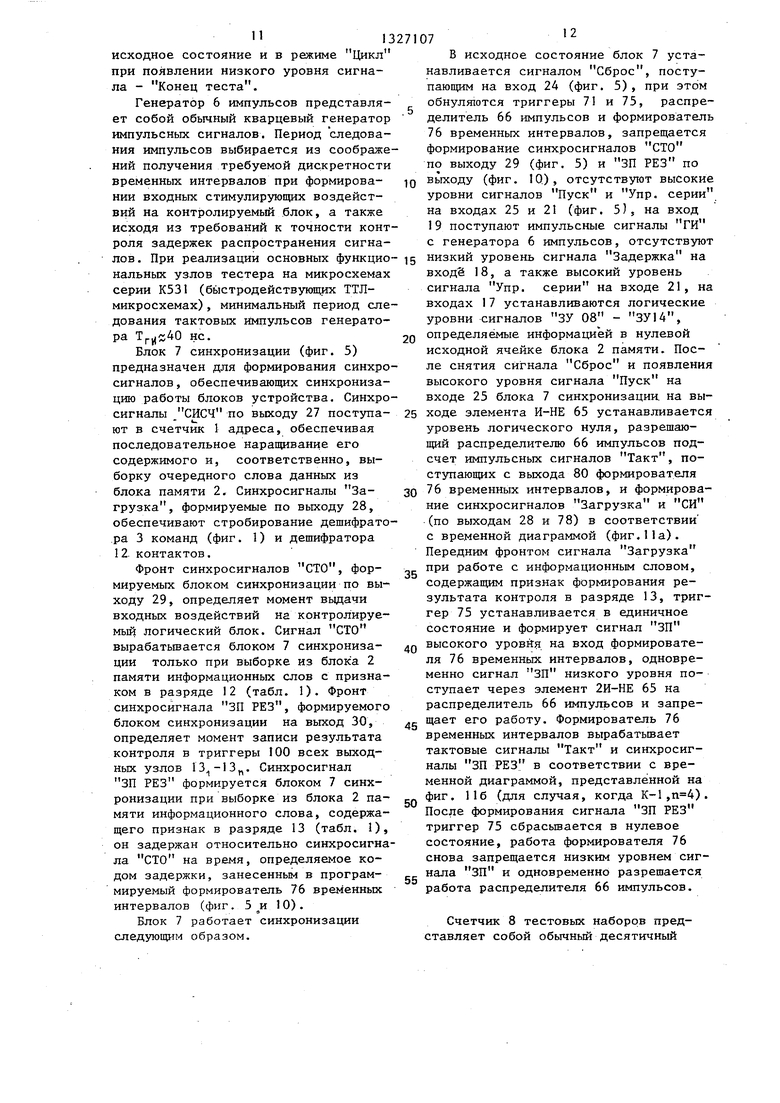

Дешифратор 12 контактов (фиг. 7) содержит элемент НЕ 91, элемент И-НЕ 92, дешифратор 93 двоичного кода в позиционный.

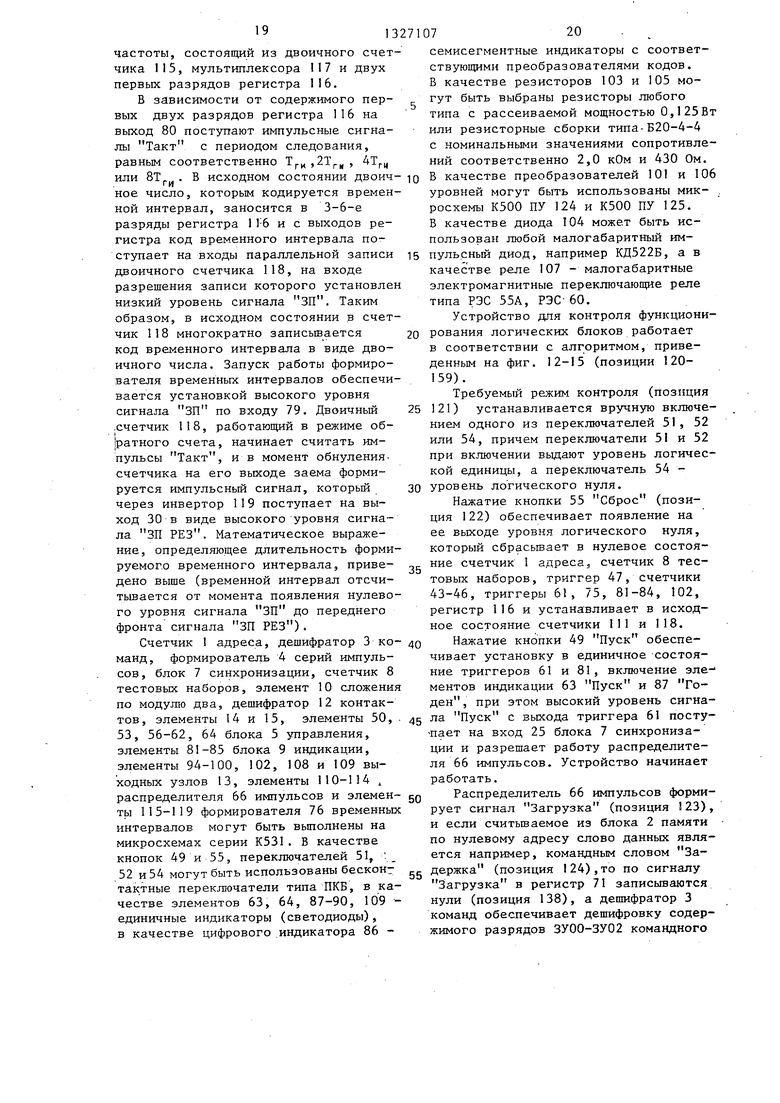

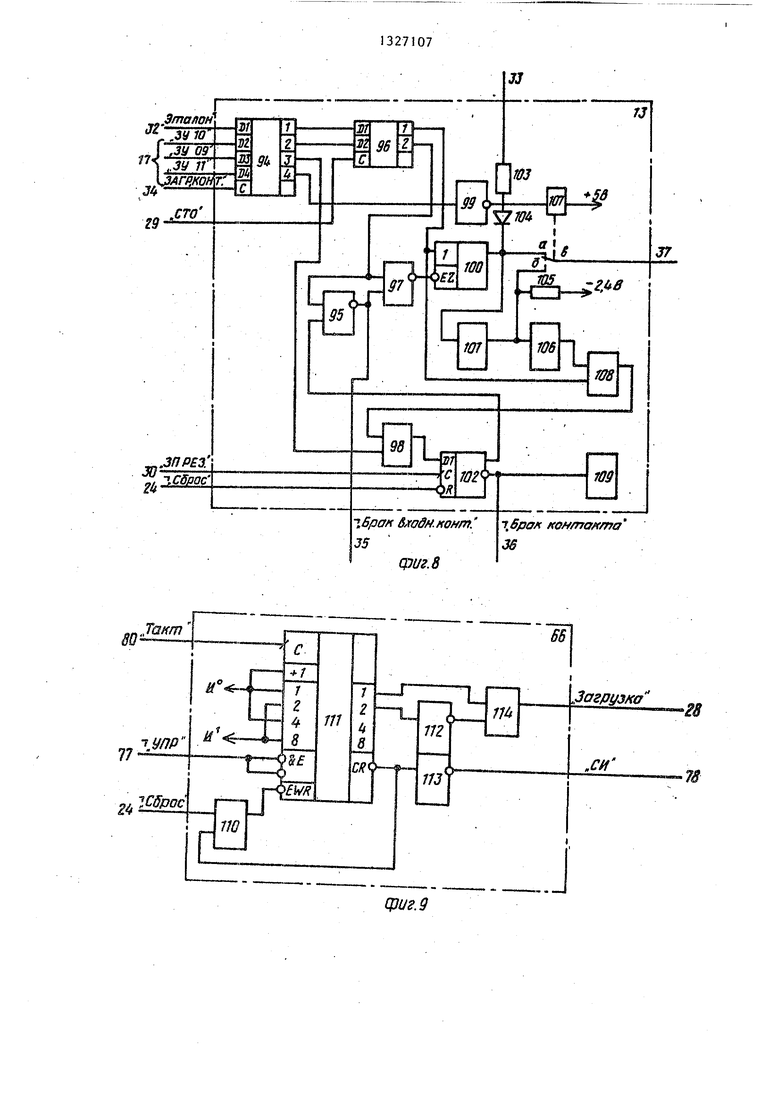

Каждьй из п программируемых узлов согласования (фиг. 8) содержит четырехразрядный регистр 94, первый элемент И-НЕ 95, двухразрядный регистр 96, второй элемент И-НЕ 97, элемент И 98, элемент НЕ 99, формирователь I00 уровней ТТЛ с тремя состояниями по выходу, преобразователь 101 уровней ТТЛ-ЭСЛ, D-триггер

102,второй согласующий резистор

103,выпрямительный диод 104, первый согласующий резистор 105, преобразователь 106 уровней ЭСЛ-ТТЛ, реле 107

07

элемент 108 сложения по модулю два, элемент 109 индикации.

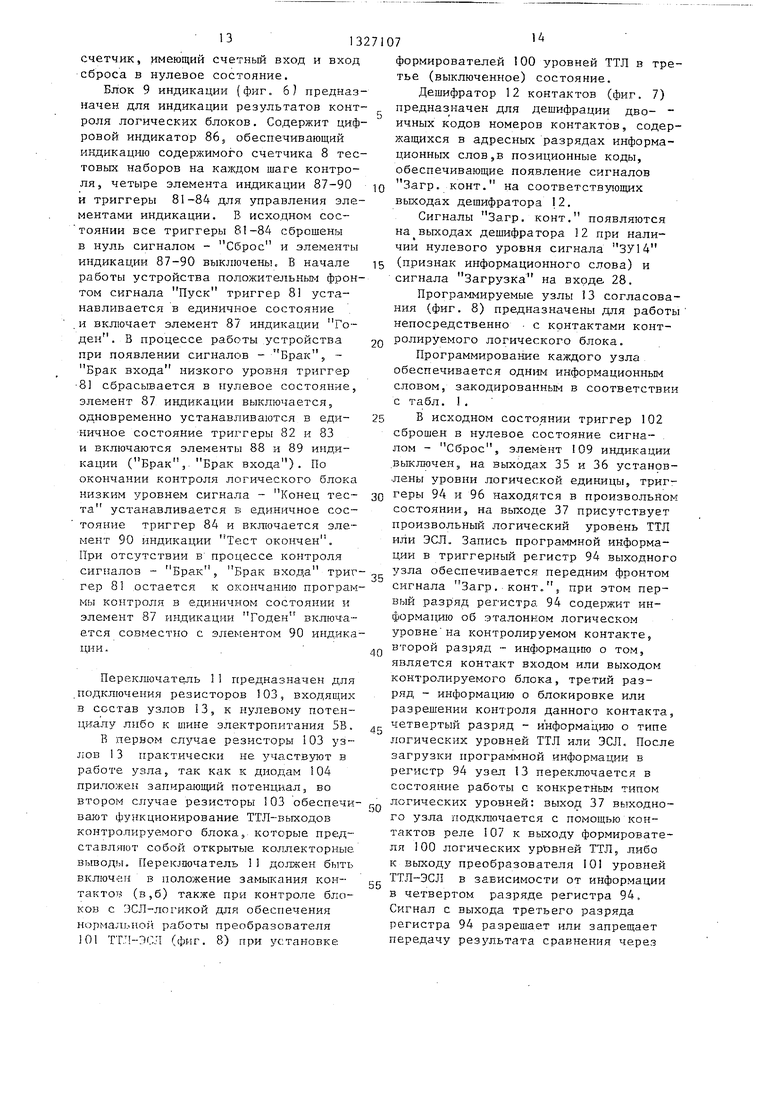

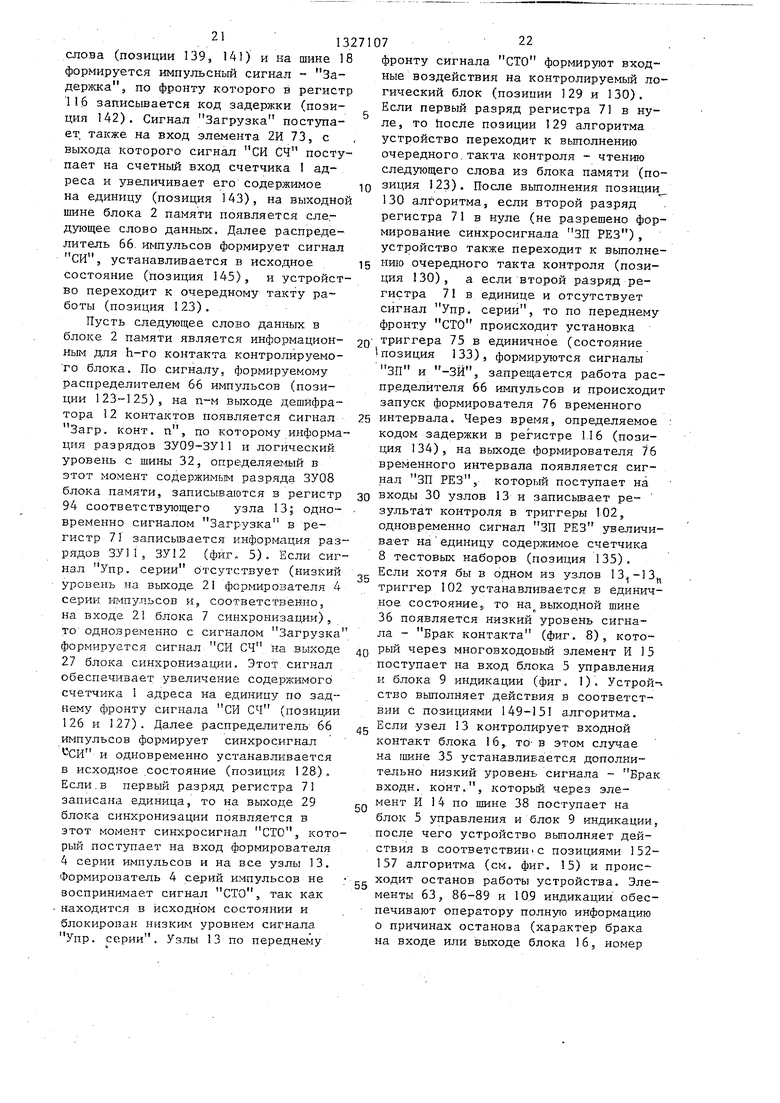

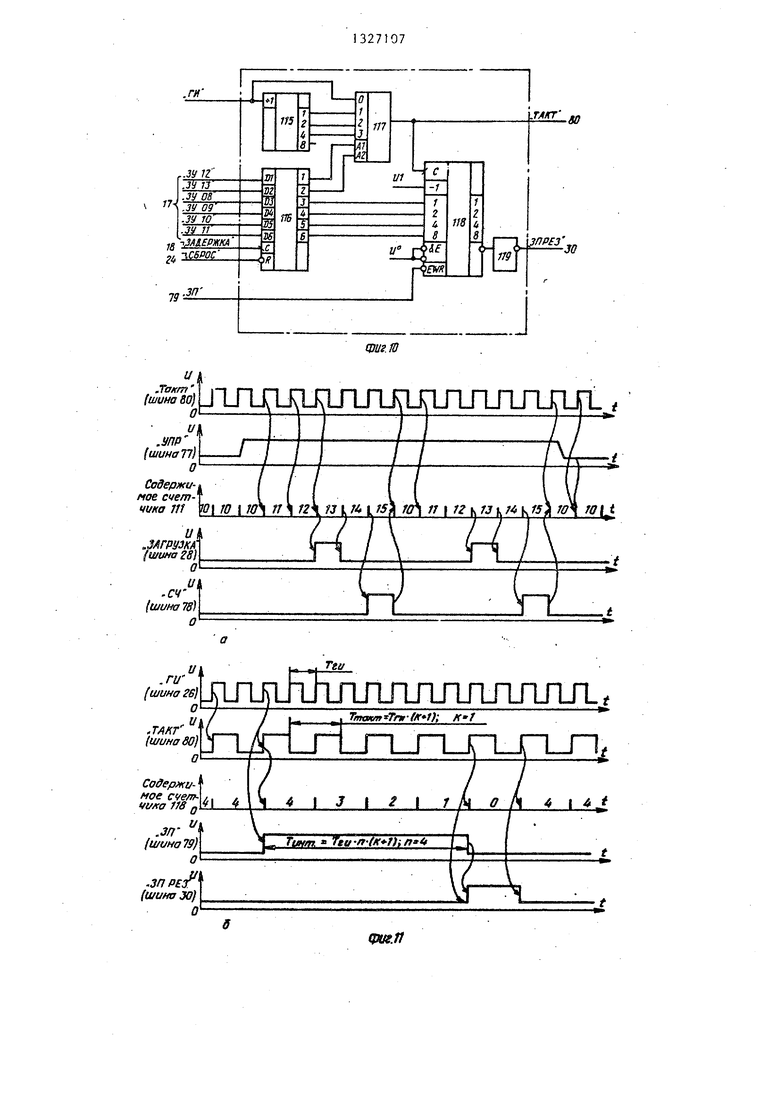

Распределитель 66 импульсов (фиг. 9) блока 7 синхронизации содержит элемент И 110, счетчик 111, элементы НЕ 112, 113, элемент И 114.

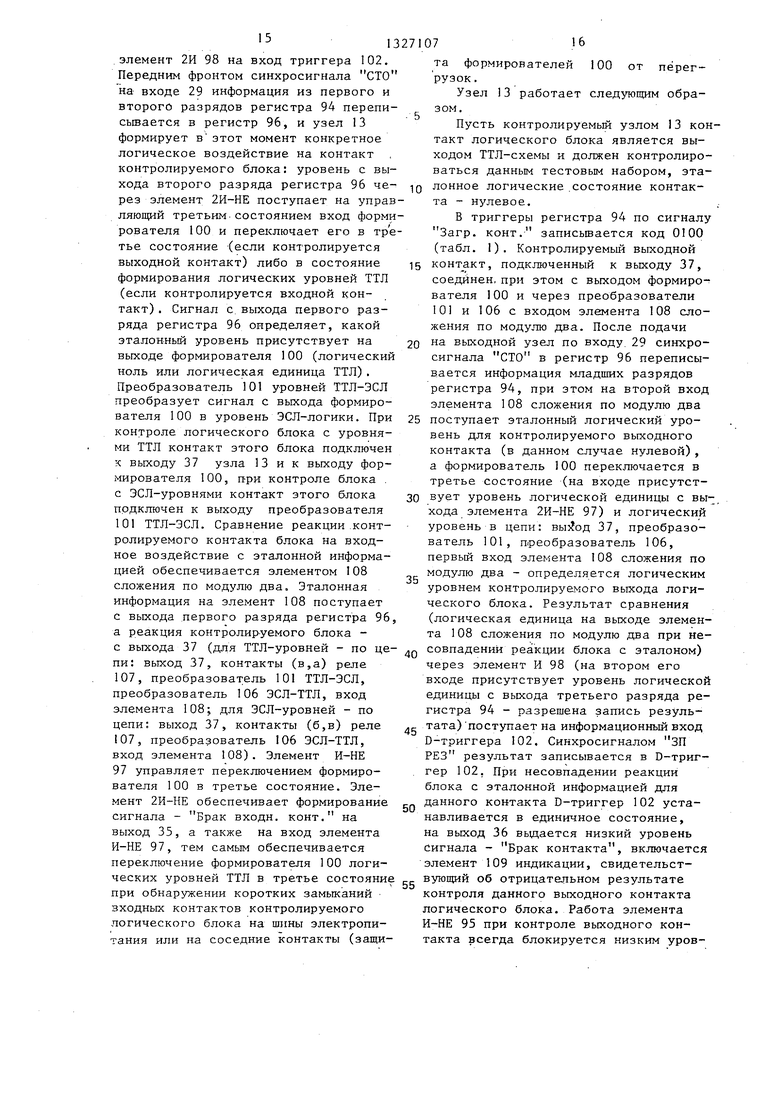

Программируемый формирователь 76 временных интервалов (фиг. 10) содержит первый двоичный счетчик 115, шестиразрядный регистр 116,. мультиплексор 117, второй двоичный счетчик

118, элемент НЕ 119.

I

Счетчик 1 адреса предназначен для формирования адресов для блока 2 памяти, представляет собой обычный двоичный многоразрядный счетчик (число разрядов счетчика определяется объемом блока памяти), имеющий вход установки в нулевое состояние, соединенный с первым выходом 23 блока 5 управления, и прямой счетный вход, соединенный с первым выходом 27 блока 7 синхронизации (фиг. 1), и может быть реализован на микросхемах К531ИЕ17.

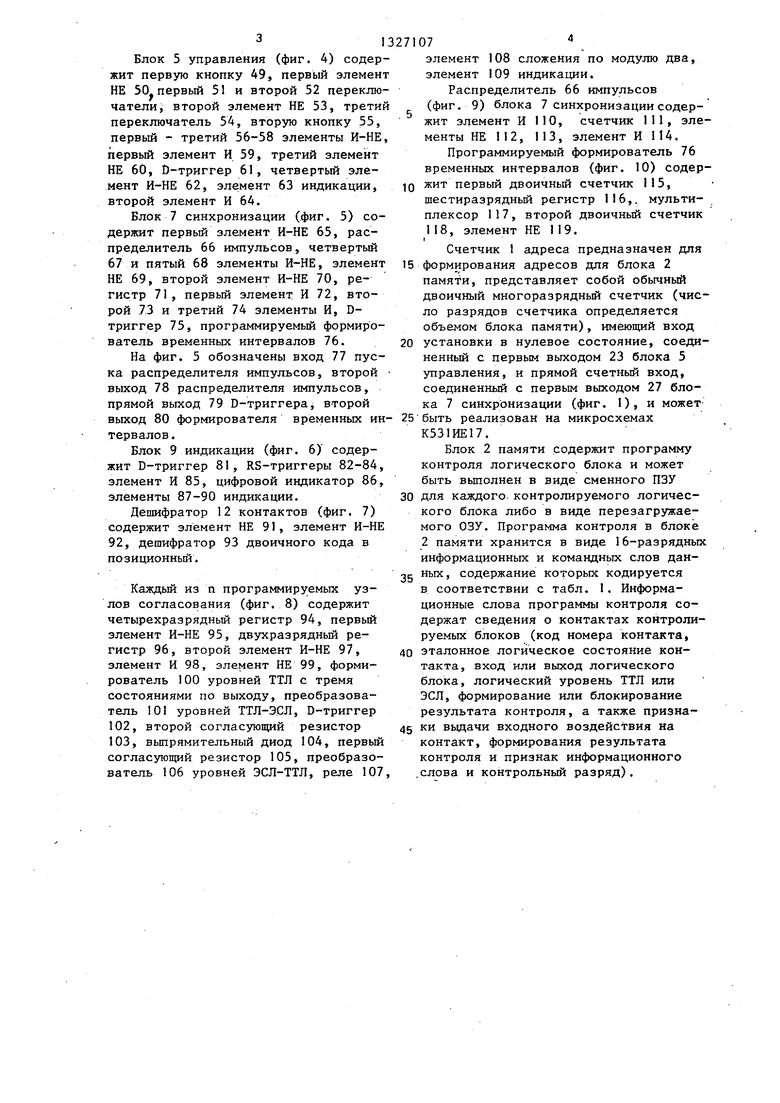

Блок 2 памяти содержит программу контроля логического блока и может быть вьшолнен в виде сменного ПЗУ для каждого контролируемого логического блока либо в виде перезагружаемого ОЗУ. Программа контроля в блоке 2 памяти хранится в виде 16-разрядных информационных и командных слов данных, содержание которых кодируется в соответствии с табл. 1. Информационные слова программы контроля содержат сведения о контактах контролируемых блоков (код номера контакта, эталонное логическое состояние контакта, вход или выход логического блока, логический уровень ТТЛ или ЭСЛ, формирование или блокирование результата контроля, а также признаки выдачи входного воздействия на контакт, формирования результата контроля и признак информационного слова и контрольный разряд).

0

1

2

3

4

Функциональные разряды

Логическое состояние контакта: лог. нуль, лог. единица

О - блокировка контроля, 1 - контроль контакта О - контакт выходной, - контакт входной

Тип логики контакта: О логика ТТЛ, 1 - логика ЭСЛ Служебные разряды

1 - признак формирования воздействия на контролируемый блок

1 признак формирования результата контроля О - признак информационного слова

Контрольный разряд. Устанавливается 1 при нечетном количестве единиц в раз- -miL.

Т а б л и ц а 1

Разряды данных , команды

Содержание разрядов определяется в зависимости от команды

Служебные разряды

Признак командного слова

Контрольный разряд. Устанавливается 1 при нечетном количестве единиц в разрядах 0-14

132

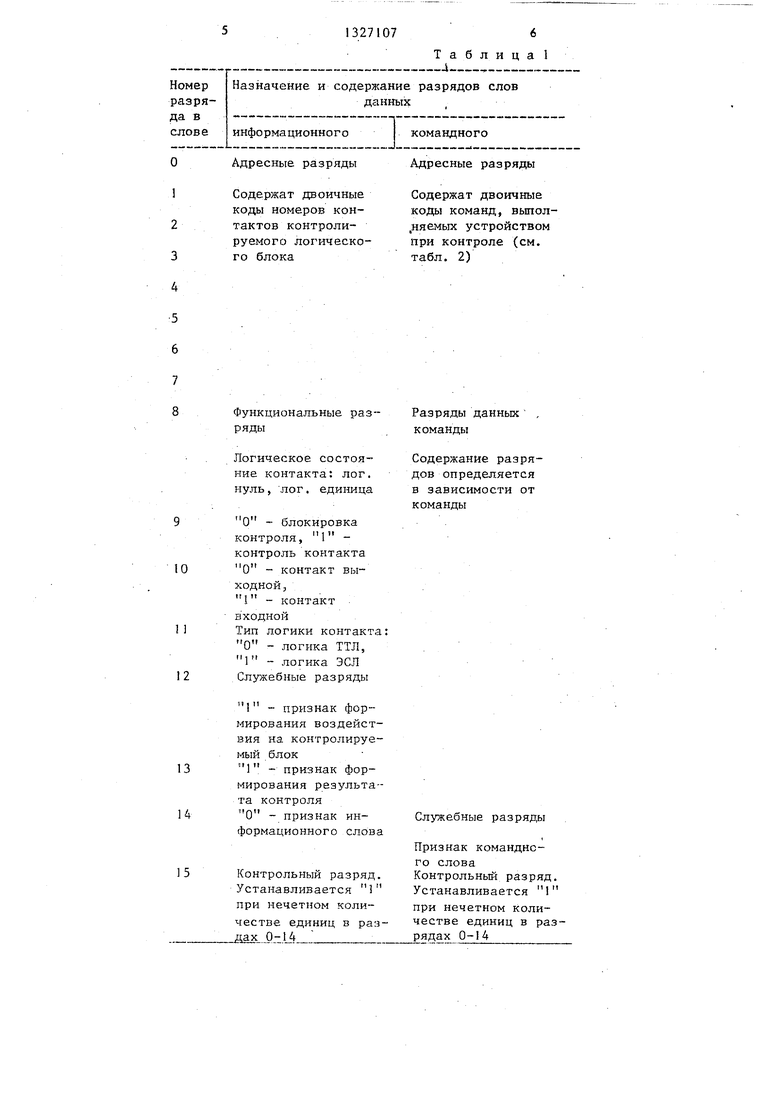

Командные слова программы контроля содержат сведения, обеспечивающие программирование соответствующих блоков устройства в заданное состояние.

Например, командное слово Конец теста обеспечивает включение элемента индикации 90 Тест окончен (фиг,6), сброс триггера 61 (фиг, 4) в нулевое

состояние и выключение элемента инди- ю на контролируемый блок в виде заракации 63 Пуск, т.е. командное ело-. во Конец теста служит для останова устройства. Командное слово Задержка обеспечивает программирование формирователя 76 временных интерва- is лов (фиг. 5 и 10), причем формируемый временной интервал кодируется разрядами 8-13 командного слова и определяется из соотношения

.«refe.. Тги П-(К+1),20

где п - число в разрядах 8-11 командного слова Задержка (код задержки); период следования импульсов

генератора;25

К - число в разрядах 12-13 командного слова Задержка. Программа контроля логического блока состоит из некоторого числа

нее запрограммированной временной диаграммы сигналов. Дискретность вре менных интервалов в такой временной диаграмме определяется следующим соотношением:

г (К+1),

где it - дискретность временных интервалов, определяется временем выборки очередного информационного слова из блрка 2 памяти; Тр - период следования импульсов

генератора 6; К - двоичное число . в разрядах

1,2 регистра 116.

Командные слова обеспечивают программирование формирователя 4 серий импульсов, причем каждое из этих слов обеспечивает протестовых наборов, которые представля- зограммирование одного из счетчиков 43ют собой совокупность служебных и ин-46 формирователя 4.

формационных слов данных, размещенных Число импульсов кодируется разряпоследовательно в блоке 2 памяти,дами 8-11 соотвествующего командного

причем последним словом .в тестовомслова. Командное слово СИ1 обеспенаборе всегда является информационное ,,дчивает возможность программирования , содержащее в разряде 14 приел ов о

знак формирования результата контроля. Каждый тестовый набор содержит эталонную информацию о входных воздействиях для некоторого числа вход- 40 ных контактов контролируемого логического блока и эталонную информацию о реакции контролируемого блока на эти воздействия для некоторого числа выходных контактов. Функция, вьшол- няемая контактом контролируемого блока на данном тестовом наборе, программируется , как правило, одним информационным словом в соответствии с табл. 1 , но при необходимости фор- gQ Конец мирования воздействия на контроли- - руемый блок в виде временной диаграммы сигналов допускается многократное изменение функции логического контакта в одном тестовом наборе, при этом информационные слова должны содер-- жать единицу в I2-м разряде (признак формирования воздействия на контролируемый блок).СИ2

1-15 импульсов в серии, СИ2 - 16- 240, СИЗ - .241-3840, СИ4 - 3841- 61440 импульсов. Четыре командных слова СИ1 - СИ4 в совокупности позволяют программировать серию импульсов от 1 до 65535.

Таблица2 Командные слова программы контроля

теста

Задержка

55

СИ1

Не используются

Ф1Н Код задержки

2Н Код числа импульсов

03Н .То же

8

Таким образом, устройство позволяет многократно изменять логическое состояние любого входного контакта контролируемого блока в пределах одного тестового набора в любой заданной программой контроля последовательности, т.е. обеспечивает выдачу входных стимулирующих воздействий

нее запрограммированной временной диаграммы сигналов. Дискретность временных интервалов в такой временной диаграмме определяется следующим соотношением:

г (К+1),

где it - дискретность временных интервалов, определяется временем выборки очередного информационного слова из блрка 2 памяти; Тр - период следования импульсов

генератора 6; К - двоичное число . в разрядах

1,2 регистра 116.

Командные слова обеспечивают программирование формирователя 4 серий импульсов, причем каждое из этих слов обеспечивает прочивает возможность программирования

онец И2

1-15 импульсов в серии, СИ2 - 16- 240, СИЗ - .241-3840, СИ4 - 3841- 61440 импульсов. Четыре командных слова СИ1 - СИ4 в совокупности позволяют программировать серию импульсов от 1 до 65535.

Таблица2 Командные слова программы контроля

ка

Не используются

Ф1Н Код задержки

2Н Код числа импульсов

03Н .То же

Продолжение табл.2 „

СИЗ

СИ4

(г«4н

5Н

Примечание, Н

шестнадцати

тема представлениячисел.

Дешифратор 3 команд (фиг. 2) предназначен для преобразования двоичных кодов адресных разрядов командных слов в импульсные сигналы на соответствующих выходах дешифратора, обеспечивающие загрузку командной информации в блок 5 управления, блок 9 индикации, блок 7 синхронизации, а таклсе в программируем1э1Й формирователь 4 серий импульсов. Синхронизация де- .шифратора 3 команд обеспечивается синхросигналом Загрузка, поступающим по шине 28.

Программируемьй формирователь 4 серий импульсов {фиг, 3) предназначен для формирования заданного числа

ричная сие- 10 считает импульсы- СТО, пост.упающие

по входу 29, а счетчики 43-46 обрат- ного счета - i-гмпульсы, появляющиеся на инверсном выходе триггера 47, до тех пор, пока полностью не будут об15 нулены. За это время на выходе 2-2 формирователя 4 появляется серия импульсов , число которых определяется двоичным 16-разрядным кодом, записанным в счетчики 43-46. После обну20 ления счетчиков 43-46 и переключения триггера 47 в нулевое состояние формирователь 4 заканчивает свою работу, так как низкий логический уровень сигнала с выхода элемента ИЛИ 48 по25 ступает на второй эход элемента И- НЕ 42 и запрещает прохождение импульсов СТО на счетный вход счетного триггера 47.

Блок 5 управления (фиг. 4) предимпульсных сигналов на контакты конт- 30 назначен для управления режимами раролируемого блока в соответствующих тактах контроля и программируется командными словами СИ - СИ4 программы контроля. Представляет собой i6-разрядный двоичный счетчик обратного счета, состояш 5й из четырех четырехразрядных счетчиков 43-46, каждый из которых програ:-4мируется соот- ветству1ош 1М командным словом программы контроля.

Счетчики 43-46 имеют общий вход 24 сброса и общие входы 17 параллельного ввода информации. Счетный триггер 47 обеспечивает деление на два импульсных синхросигналов СТО, поступающих на вход 29 формирователя 4. Прямой выход триггера 47 является выходом 22 формирователя 4.

Работает формирователь импульсов 4 следующим образом.

В исходном состоянии счетчики 43- 46 и счетный триггер 47 установлены в нуль, поэтому на всех входах элемента ИЛИ 4В и, соответственно, на выходе этого элемента присутствуют нулевые уровни. Нулевой уровень на втором входе элемента И-НЕ 42 запрещает прохождение синхросигналов СТО, и формирователь импульсов 4

не работает до тех пор, пока хотя бы Е один разряд любого из счетчиков 43-46 не будет записана единица. Появление логической единицы на любом входе элемента ИЛИ 48. обеспечивает появление единицы на выходе 21 формирователя 4 и на втором входе элемента И-НЕ 42, счетный триггер 47

5

0

5

0

5

боты устройства и обеспечивает возможность установки устройства в исходное состояние, пуск и останов устройства в различных режимах контроля.

Блок 5 управления формирует сигнал Пуск по выходу 25 при нажатии кнопки 49. Снимается сигнал Пуск, либо при появлении низкого уровня сигнала на входе 38, либо при нажатии кнопки 55 Сброс, либо низким уровнем сигнала Конец теста на входе 9 в режимах контроля Шаг и До брака (включен один из переключателей 51 или 52), либо низким уровнем сигнала Брак на входе 39 в режиме До брака (включен переключатель 51), либо высоким уровнем сигнала ЗП РЕЗ на входе 30 в режиме Шаг (включен переключатель 52). Блок 5 управления формирует сигнал Сброс низкого уровния по выходу 24 при нажатии кнопки 55, обеЬпечивающий установку устройства в исходное состояние. По выходу 23 блок 5 управления формирует сигнал - Сброс СЧ низкого уровня для обнуления счетчика адреса и счетчика В тестовых наборов (фиг. 1) при установке устройства в

ч1

исходное состояние и в режиме Цикл при появлении низкого уровня сигнала - Конец теста.

Генератор 6 импульсов представляет собой обычный кварцевый генератор импульсных сигналов. Период следования импульсов выбирается из соображений получения требуемой дискретности временных интервалов при формирова- НИИ входных стимулирующих воздействий на контролируемый блок, а также исходя из требований к точности контроля задержек распространения сигналов. При реализации основных функцио нальньгх узлов тестера на микросхемах серии К531 (быстродействующих ТТЛ- микросхемах) , минимальный период следования тактовых импульсов генератора T|.,,ci40 НС.

Блок 7 синхронизации (фиг. 5) предназначен для формирования синхросигналов , обеспечивающих синхронизацию работы блоков устройства. Синхросигналы СИСЧ по выходу 27 поступа- ют в счетчик 1 адреса, обеспечивая последовательное наращивание его содержимого и, соответственно, выборку очередного слова данных из блока памяти 2. Синхросигналы За- грузка, формируемые по выходу 28, обеспечивают стробирование дешифратора 3 команд (фиг. 1) и дешифратора 12 контактов.

Фронт синхросигналов СТО, фор- мируемых блоком синхронизации по вы- ходу 29, определяет момент выдачи входных воздействий на контролируемый логический блок. Сигнал СТО вырабатывается блоком 7 синхрониза- ции только при выборке из блок а 2 памяти информационных слов с признаком в разряде 12 (табл. 1). Фронт синхросигнала 30 РЕЗ, формируемого блоком синхронизации на выход 30, определяет момент записи результата контроля в триггеры 100 всех выходных узлов . Синхросигнал ЗП РЕЗ формируется блоком 7 синхронизации при выборке из блока 2 па- мяти информационного слова, содержащего признак в разряде 13 (табл. 1), он задержан относительно синхросигнала сто на время, определяемое кодом задержки, занесенным в програм- мируеный формирователь 76 временных интервалов (фнг. 5 к 10).

Блок 7 работает синхронизации следующим образом.

07

12

В исходное состояние блок 7 устанавливается сигналом Сброс, поступающим на вход 24 (фиг. 5), при этом обнуляются триггеры 7 и 75, распределитель 66 импульсов и формировател 76 временных интервалов, запрещается формирование синхросигналов СТО по выходу 29 (фиг. 5) и ЗП РЕЗ по вьпкоду (фиг. 10), отсутствуют высоки уровни сигналов Пуск и Упр. серии на входах 25 и 21 (фиг. 5), на вход 19 поступают импульсные сигналы ГИ с генератора 6 импульсов, отсутствую низкий уровень сигнала Задержка на входе 18, а также высокий уровень сигнала Упр. серии на входе 21, н входах 17 устанавливаются логические уровни сигналов ЗУ 08 - ЗУ14, определяемые информацией в нулевой исходной ячейке блока 2 памяти. После снятия сигнала Сброс и появления высокого уровня сигнала Пуск на входе 25 блока 7 синхронизации на выходе элемента И-НЕ 65 устанавливается уровень логического нуля, разрешающий распределителю 66 импульсов подсчет импульсных сигналов Такт, поступающих с выхода 80 формирователя 76 временных интервалов, и формирование синхросигналов Загрузка и СИ (по выходам 28 и 78) в соответствии с временной диаграммой (фиг.11 а). Передним фронтом сигнала Загрузка при работе с информационным словом, содержащим признак формирования результата контроля в разряде 13, триггер 75 устанавливается в единичное состояние и формирует сигнал ЗП высокого уровня на вход формирователя 76 временных интервалов, одновременно сигнал ЗП низкого уровня поступает через элемент 2И-НЕ 65 на распределитель 66 импульсов и запрещает его работу. Формирователь 76 временных интервалов вырабатьшает тактовые сигналы Такт и синхросигналы ЗП РЕЗ в соответствии с временной диаграммой, представленной на фиг. 116 (для случая, когда К-1,). После формирования сигнала ЗП РЕЗ триггер 75 сбрасьшается в нулевое состояние, работа формирователя 76 снова запрещается низким уровнем сигнала ЗП и одновременно разрешается работа распределителя 66 импульсов.

Счетчик 8 тестовых наборов представляет собой обычный десятичный

13

1327i и вход

счетчик, имеющий счетный вход сброса в нулевое состояние.

Блок 9 индикации (фиг. б) предназначен для индикации результатов контроля логических блоков. Содержит цифровой индикатор 86, обеспечивающий индикацию содержимого счетчика 8 тестовых наборов на каждом шаге контроля, четыре элемента индикации 87-90 триггеры 81-84 для управления элеентами индикации. В исходном сос- оянии все триггеры 81-84 сброшены нуль сигналом - Сброс и элементы ндикации 87-90 выключены. В начале работы устройства положительным фронтом сигнала Пуск триггер 81 устанавливается в единичное состояние и включает элемент 87 индикации Гоен . В процессе работы устройства при появлении сигналов - Брак, - Брак входа низкого уровня триггер 81 сбрасывается в нулевое состояние, элемент 87 индикации выключается, одновременно устанавливаются в единичное состояние триггеры 82 и 83 и включаются элементы 88 и 89 индикации (Брак,. Брак входа). По окончании контроля логического блока низким уровнем сигнала - Конец теста устанавливается в единичное состояние триггер 84 и включается элемент 90 индикации Тест окончен . При отсутствии в процессе контроля сигналов - Брак, Брак входа триггер 81 остается к окончанию програм- мы контроля в единичном состоянии и

20

,

элемент 87 индикации Годен включается совместно с элементом 90 индикации .

Переключатель 11 предназначен для подключения резисторов 103, входящих в состав узлов 13, к нулевому потенциалу либо к шине электропитания 5В.

В первом случае резисторы 103 узлов 13 практически не участвуют в работе узла, так как к диодам 104 приложен запирающий потенциал, во втором случае резисторы 103 обеспечивают функционирование ТТЛ-выходов контролируемого блока, которые представляют собой открытые коллекторные выводы. Переключатель 11 должен быть включен в положение замьшания контактов (в,б) также при контроле блоков с ЭСЛ-логиКой для обеспечения нормально работы преобразователя 101 ТТЛ-ЭСЛ (фиг. В) при установке

07

1А

0

5

0

0

5

0

5

0

5

формирователей 100 уровней ТТЛ в третье (выключенное) состояние.

Дешифратор 12 контактов (фиг. 7) предназначен для дешифрации дво- - ичных кодов номеров контактов, содер- жа:цихся в адресных разрядах информационных СЛОВ5В позиционные коды, обеспечивающие появление сигналов Загр. конт. на соответствующих выходах дешифратора 12.

Сигналы Загр. конт. появляются на выходах деимфратора 12 при наличии нулевого уровня сигнала ЗУ14 (признак информационного слова) и сигнала Загрузка на входе 28.

Программируемые узлы 13 согласования (фиг. 8) предназначены для работы непосредственно с контактами контролируемого логического блока.

Программирование каждого узла обеспечивается одним информационным словом, закодированным в соответствии с табл. 1.

В исходном состоянии триггер 102 сброшен в нулевое состояние сигна- . лом - Сброс, элемент 09 индикации .выключен, на выходах 35 и 36 установлены уровни логической единицы, триггеры 94 и 96 находятся в произвольном состоянии, на выходе 37 присутствует произвольный логический уровень ТТЛ или ЭСЛ. Запись программной информации в триггерный регистр 94 выходного узла обеспечивается передним фронтом сигнала Загр. конт., при этом первый разряд регистра 94 содержит информацию об эталонном логическом уровне на контролируемом контакте, второй разряд - информацшо о том, является контакт входом или выходом контролируемого блока, третий разряд, - информацию о блокировке или разрешении контроля данного контакта, четверты разряд информацию о типе логических уровней ТТЛ или ЭСЛ. После загрузки программной информации в регистр 94 узеш 13 переключается в состояние работы с конкретным типом логических уровней: выход 37 выходного узла подключается с помощью контактов реле 107 к выходу формирователя 100 логических урЬвней ТТЛ, либо к выходу преобразователя 10 уровней ТТЛ-ЭСЛ в зависимости от информации в четвертом разряде регистра 94, Сигнал с выхода третьего разряда регистра 94 разрешает или запрещает передачу результата сравнения через

элемент 2И 98 на вход триггера 102, Передним фронтом синхросигнала СТО на входе 29 информация из первого и второго разрядов регистра 94 перепи- сьшается в регистр 96, и узел 13 формирует в этот момент конкретное логическое воздействие на контакт контролируемого блока: уровень с выхода второго разряда регистра 96 через элемент 2И-НЕ поступает на управляющий третьим-состоянием вход формирователя 100 и переключает его в третье состояние (если контролируется выходной контакт) либо в состояние формирования логических уровней ТТЛ (если контролируется входной контакт) . Сигнал с выхода первого разряда регистра 96 определяет, какой эталонньй уровень присутствует на выходе формирователя 100 (логический ноль или логическая единица ТТЛ). Преобразователь 101 уровней ТТЛ-ЭСЛ преобразует сигнал с выхода формирователя 100 в уровень ЭСЛ-логики. При контроле логического блока с уровнями ТТЛ контакт этого блока подключен к выходу 37 узла 13 и к выходу формирователя 100, при контроле блока . с ЭСЛ-уровнями контакт этого блока подключен к выходу преобразователя 101 ТТЛ-ЭСЛ. Сравнение реакции контролируемого контакта блока на входное воздействие с эталонной информацией обеспечивается элементом I08 сложения по модулю два. Эталонная информация на элемент 108 поступает с выхода первого разряда регистра 96 а реакция контролируемого блока - с выхода 37 (для ТТЛ-уровней - по це пи: выход 37, контакты (в,а) реле 107, преобразователь 101 ТТЛ-ЭСЛ, преобразователь 106 ЭСЛ-ТТЛ, вход элемента 108; для ЭСЛ-уровней - по цепи: выход 37, контакты (б,в) реле 107, преобразователь 106 ЭСЛ-ТТЛ, вход элемента 108). Элемент И-НЕ 97 управляет переключением формирователя 100 в третье состояние. Элемент 2И-НЕ обеспечивает формирование сигнала - Брак входн. конт, на выход 35, а также на вход элемента И-НЕ 97, тем самым обеспечивается переключение формирователя 100 логических уровней ТТЛ в третье состояние при обнаружении коротких замьжаний входных контактов контролируемого логического блока на шины электропитания или на соседние контакты (защи

07

16

Q 5 0 5 о „ g „

5

5

та формирователей 100 от перегрузок .

Узел 13 работает следующим образом.

Пусть контролируемый узлом 13 контакт логического блока является выходом ТТЛ-схемы и должен контролироваться данньм тестовым набором, эталонное логические .состояние контакта - нулевое.

В триггеры регистра 94 по сигналу Загр. конт. записьшается код 0100 (табл. 1). Контролируемьй выходной контакт, подключенный к выходу 37, соединен, при этом с выходом формирователя 100 и через преобразователи 101 и 106 с входом элемента 108 сложения по модулю два. После подачи на выходной узел по входу. 29 синхросигнала сто в регистр 96 переписывается информация младших разрядов регистра 94, при этом на второй вход элемента 108 сложения по модулю два поступает эталонный логический уровень для контролируемого выходного контакта (в данном случае нулевой), а формирователь 100 переключается в третье состояние (на входе присутствует уровень логической единицы с вы-, хода элемента 2И-НЕ 97) и логический уровень в цепи: 37, преобразователь 101, преобразователь 106, первый вход элемента 108 сложения по модулю два - определяется логическим уровнем контролируе.мого выхода логического блока. Результат сравнения (логическая единица на выходе элемента 108 сложения по модулю два при несовпадении реакции блока с эталоном) через элемент И 98 (на втором его входе присутствует уровень логической единицы с выхода третьего разряда регистра 94 - разрешена запись результата) поступает на информационный вход D-триггера 102. Синхросигналом ЗП РЕЗ результат записывается в D-триг- гер 102. При несовпадении реакции блока с эталонной информацией для данного контакта D-триггер 102 устанавливается в единичное состояние, на выход 36 выдается низкий уровень Сигнала - Брак контакта, включается элемент 109 индикации, свидетельствующий об отрицательном результате контроля данного выходного контакта логического блока. Работа элемента И-НЕ 95 при контроле выходного контакта всегда блокируется низким уровнем с выхода второго разряда регистра 96, поэтому на выходе 35 при контроле выходов логического блока всегд присутствует уровень логической единицы.

. Если контролируемый контакт логического блока является выходом ЭСЛ- , схемы, то, в отличие от предыдуЕ1;его случая, в четвертый разряд регистра . 94 должна быть занесена логическая единица, в результате чего реле. 107, управляемое инвертором 99э подключает выход 37 узла 13 (вместе с контролируемым ЭСЛ-вьрсодом блока) к входу преобразователя 106 уровней ЭСЛ-ТТЛ, При этом преобразователь 101 ТТЛ-ЭСЛ находится в состоянии логической единицы (под воздействием высокого уровня сигнала на входе 33), а так как микросхемы типа ЭСЛ допускают объединение по выходам в так называемое монтажное И, то в данном случае логический уровень на входе преобразователя 106 ЭСЛ-ТТЛ определяется состоянием контролируемого ЭСЛ-выхо- да логического блока (для рассматриваемого примера это логический уро- вень нуля ЭСЛ). В остальном работа узла 13 при контроле выхода схемы ЭСЛ не отличается от режима работы при контроле выхода ТТЛ-схемы, Резистор 103 служит нагрузочным элементом для обеспечения функционирования ТТЛ-выхода с открытым коллектором., а резистор 105 - нагрузочным элементом для преобразователя 101. и контролируемого ЭСЛ-выхода логического, блока.

Работа узла 13 при контроле входных контактов логического блока отличается от работы при контроле выходов только тем, что в регистре 94 во втором разряде должна быть з;-стаьювлена логическая единица (означает контроль входа логического блока), после перезаписи этой единицы в регистр 96 происходит перевод формирователя 98 из третьего (выключенного ) состояния в логическое состояние, определяемое содержимым первого разряда регистра 96, т.е. формирователь 100 (для ТТЛ-входов)

н преобразователь 10 ТТЛ-ЭСЛ (для

(СЛ-входов) являются в данном „ для формирования временных интервалов

источниками стимулирую1щ-1х входных воздействий в соответствии с эталонной тестовой информацией. Отличие состоит также в.том, что разрешена

в соответствии с временной д aгpaммoй его работы в составе блока 7 синхронизации (фиг, 116). Формирователь 76 содерлсит программируемый делитель

работа элемента И-НЕ 95, в случае несовпадения реакции входа логического блока с эталоном элемент И-НЕ 95 формирует- низкий уровень сигнала - . Брак входн. конт., который через элемент И-НЕ 97 обеспечивает выключение (перевод в третье состояние) формирователя 100, предупреждая его перегрузку,

Для блокировки результата на очередном такте контроля в третий разряд регистра 94 следует записать логический нуль.

Таким .образом, наличие в устройст- ве программируемых на каждом такте контроля узлов 13 позволяет наперед заданньЕМ программой контроля образом отслеживать изменяющиеся в процессе контроля состояния контролируемых . контактов: вход может становиться выходом блока и наоборот (обеспечивается контроль дззунаправленных интерфейсных шинных формирователей, а также логических бдоков с программируемыми интерфейсными БИС).

Распределитель 66 импульсов (фиг. 9) представляет собой двоичнда счетчик 111, который сигналом - Сброс устанавливается по входам параллельной записи в состояние 10 (фиг, 11 а). При поступлении по входу 77 низкого уровня сигнала УПР счетчик считает импульсы Такт, посту- пающие по входу 80. В состоянии . 3 на выходе 28 распределителя импульсов формируется импульсный сигнал Загрузка (длительность импульса равна периоду следования импульсов Такт). В состоянии 15 счетчика III на выходе 78 распределителя импульсов формируется импульсный сигнал СИ с .дли- тельностью, равной периоду сигнала одновременно сигнал отрица- тельной полярности с выхода переноса счетчика 1 S 1 через элемент И ПО обеспечивает установку счетчика 111 в исходное состояние (содержимое счетчика равно десяти). Далее циклы работы счетчика I11 повторяются при наличии разрешаю щего сигнала УПР на входе 77.

Программируемый формирователь 76 временных интервалов ггредназначен

в соответствии с временной д aгpaммoй его работы в составе блока 7 синхронизации (фиг, 116). Формирователь 76 содерлсит программируемый делитель

191

частоты, состоящий из двоичного счетчика 115, мультиплексора 117 и двух первых разрядов регистра 116.

В зависимости от содержимого первых двух разрядов регистра 116 на выход 80 поступают импульсные сигналы Такт с периодом следования, равным соответственно Т,,2Т|., 41,

или 8т |. . В исходном состоянии ДВОИЧ

ное число, которым кодируется временной интервал, заносится в 3-6-е разряды регистра 1 1-6 и с выходов регистра код временного интервала поступает на входы параллельной записи двоичного счетчика 118, на входе разрешения записи которого установле низкий уровень сигнала ЗП. Таким образом, в исходном состоянии в счетчик 118 многократно записьшается код временного интервала в виде двоичного числа. Запуск работы формирователя временных интервалов обеспечивается установкой высокого уровня сигнала ЗП по входу 79. Двоичный .счетчик 118, работающий в режиме обратного счета, начинает считать импульсы Такт, ив момент обнуления- счетчика на его выходе заема формируется импульсный сигнал, который через инвертор 119 поступает на выход 30 в виде высокого уровня сигнала ЗП РЕЗ. Математическое выражение, определяющее длительность формируемого временного интервала, приве- дено выше (временной интервал отсчитывается от момента появления нулевого уровня сигнала ЗП до переднего фронта сигнала ЗП РЕЗ).

Счетчик 1 адреса, дешифратор 3 ко- манд, формирователь 4 серий импульсов, блок 7 синхронизации, счетчик 8 тестовых наборов, элемент 10 сложения по модулю два, дешифратор 12 контактов, элементы 14 и 15, элементы 50, 53, 56-62, 64 блока 5 управления, элементы 81-85 блока 9 индикации, элементы 94-100, 102, 108 и 109 выходных узлов 13, элементы 110-114 распределителя 66 импульсов и элемен- ты 115-119 формирователя 76 временных интервалов могут быть выполнены на микросхемах серии К531. В качестве кнопок 49 и 55, переключателей 51, : 52 и 54 могут быть использованы бескон- тактные переключатели типа ПКБ, в качестве элементов 63, 64, 87-90, 109 - единичные индикаторы (светодиоды), в качестве цифрового индикатора 86 07

20

5

Q

5 0 5 0 g

0 5 0 g

семисегментные индикаторы с соответствующими преобразователями кодов. В качестве резисторов 103 и 105 могут быть выбраны резисторы любого типа с рассеиваемой мощностью 0,125Вт или резисторные сборки типа 520-4-4 с номинальными значениями сопротивлений соответственно 2,0 кОм и 430 Ом. В качестве преобразователей 101 и 106 уровней могут быть использованы мик- . росхемы К500 ПУ 124 и К500 ПУ 125. В качестве диода 104 может быть использован любой малогабаритный импульсный диод, например КД522Б, а в качестве реле I07 - малогабаритные электромагнитные переключающие реле типа РЭС 55А, РЭС-60.

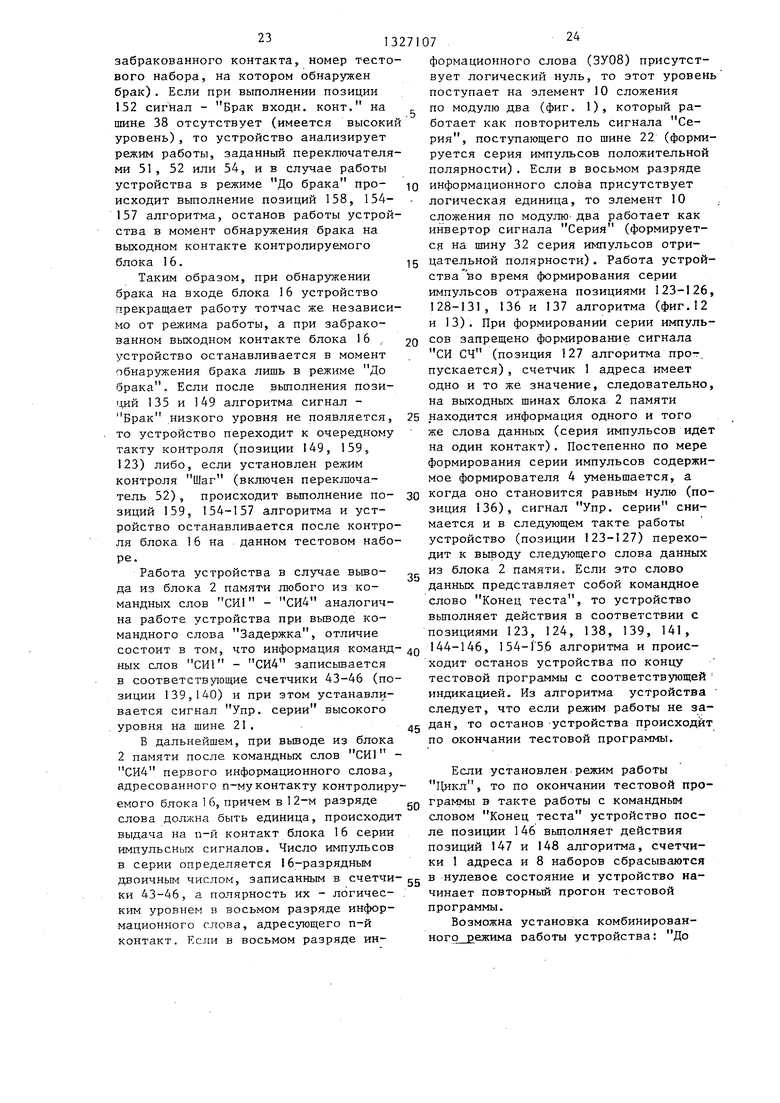

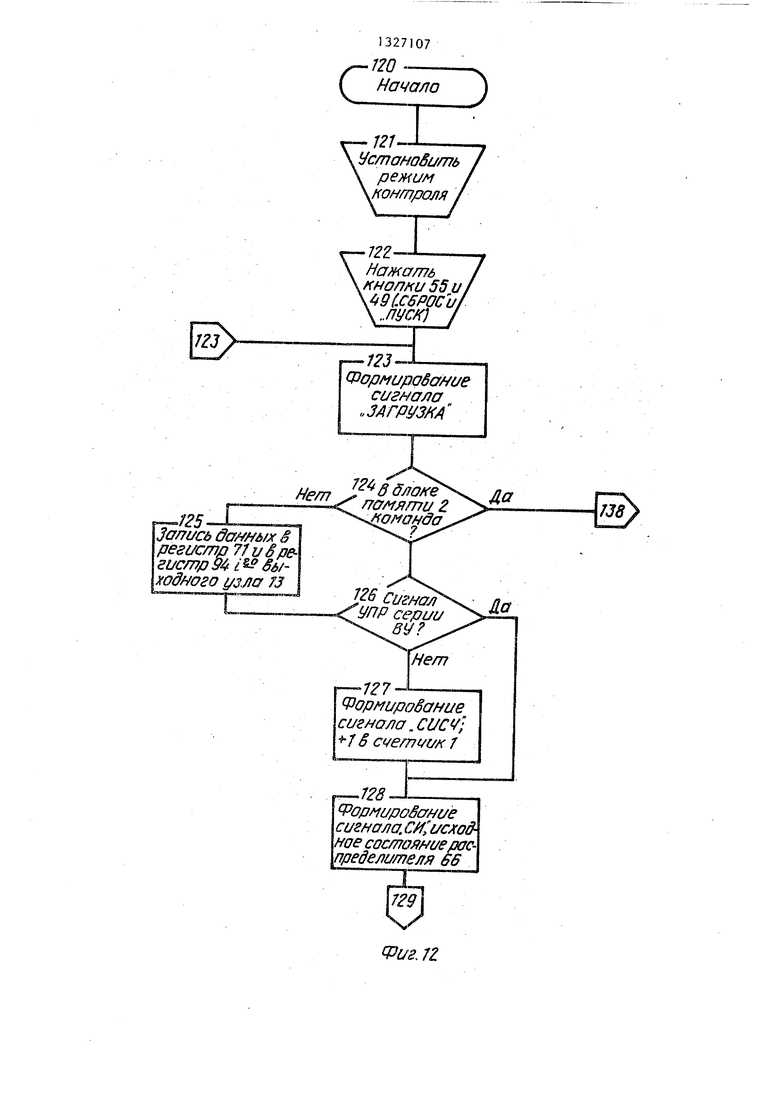

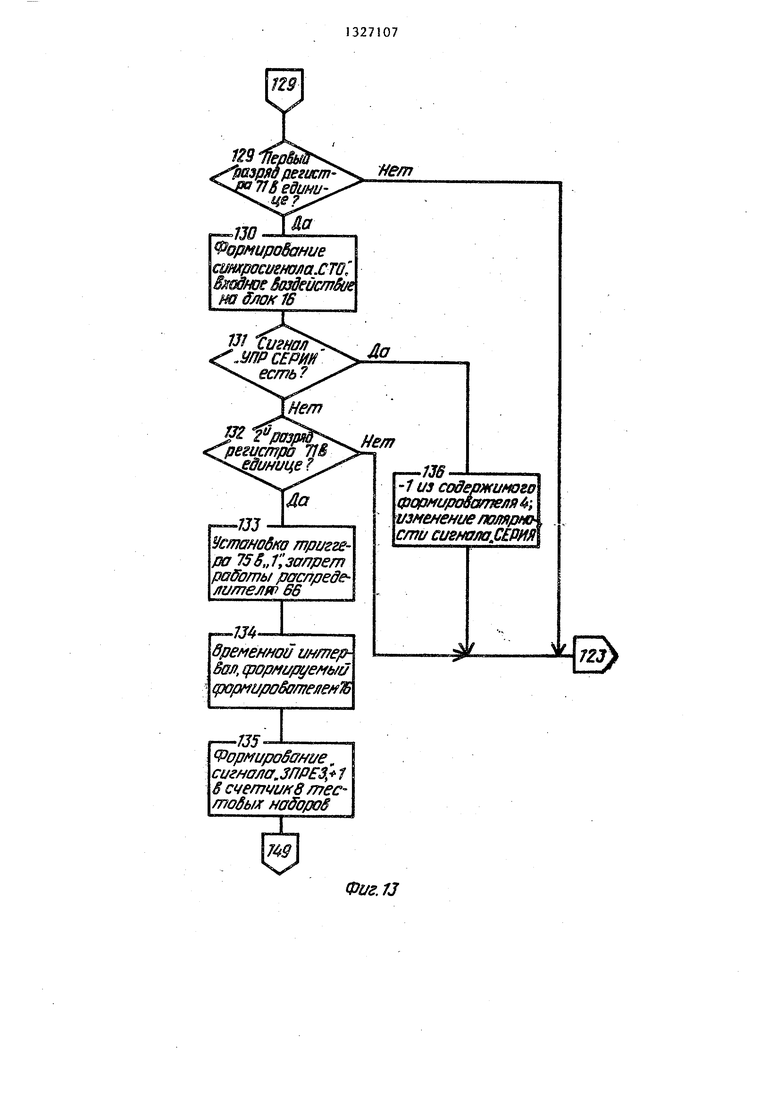

Устройство для контроля функционирования логических блоков работает в соответствии с алгоритмом, приведенным на фиг. 12-15 (позиции 120- 159).

Требуемый режим контроля (позиция 121) устанавливается вручную включением одного из переключателей 51, 52 или 54, причем переключатели 51 и 52 при включении выдают уровень логической единицы, а переключатель 54 - уровень логического нуля.

Нажатие кнопки 55 Сброс (позиция 122) обеспечивает появление на ее выходе уровня логического нуля, который сбрасьшает в нулевое состояние счетчик 1 адресаS счетчик 8 тестовых наборов, триггер 47, счетчики 43-46, триггеры 61, 75, 81-84, 102, регистр 116 и устанавливает в исходное состояние счетчики 111 и 118.

Нажатие кнопки 49 Пуск обеспечивает установку в единичное состояние триггеров 61 и 81, включение эле- ментов индикации 63 Пуск и 87 Годен , при этом высокий уровень сигнала Пуск с выхода триггера 61 поступает на вход 25 блока 7 синхронизации и разрешает работу распределителя 66 импульсов. Устройство начинает работать.

Распределитель 66 импульсов формирует сигнал Загрузка (позиция J 23), и если считьшаемое из блока 2 памяти по нулевому адресу слово данных является например, командным словом Задержка (позиция 124),то по сигналу Загрузка в регистр 71 записываются нули (позиция 138), а дешифратор 3 команд обеспечивает дешифровку содержимого разрядов ЗУОО-ЗУ02 командного

слова (позиции 139, 141) и на шине 18 формируется импульсный сигнал - Задержка, по фронту которого в регистр 116 записывается код задержки (позиция 142), Сигнал Загрузка постзша- ет, также на вход элемента 2И 73, с выхода которого сигнал СИ СЧ поступает на счетный вход счетчика адреса и увеличивает его содержимое на единицу (позиция 143), на выходной шине блока 2 памяти появляется сле,- дующее слово данных. Далее распределитель 66. импульсов формирует сигнал си, устанавливается в исходное состояние (позиция 145), и устройство переходит к очередному такту работы (позиция 123).

Пусть следующее слово данных в блоке 2 памяти является информационным для h-ro контакта контролируемо- то блока. По сигналу, формируемому распределителем 66 импульсов (позиции 123-125), на п-м выходе дешифратора 12 контактов появляется сигнал Загр. конт. п, по которому информация разрядов ЗУ09-ЗУ11 и логический уровень с шины 32, определяемый в этот момент содержимьич разряда ЗУ08 блока памяти, записываются в регистр 94 соответствующего узла 13; одновременно сигналом Загрузка в регистр 71 записывается информация разрядов ЗУ11, ЗУ12 (фиг. 5). Если сигнал Упр. серии отсутствует (низкий уровень на выходе 21 формирователя 4 серии импульсов и, соответственно, на входе 21 блока 7 синхронизации), то одновременно с сигналом Загрузка формируется сигнал CPI СЧ на выходе 27 блока синхронизации. Этот сигнал обеспечивает увеличение содержимого счетчика 1 адреса на единицу по заднему фронту сигнала СИ СЧ (позиции 126 и 127). Далее распределитель 66 импульсов формирует синхросигнал и одновременно устанавливается в исходное состояние (позиция 128), Если.в первый разряд регистра 71 записана единица, то на выходе 29 блока синхронизации появляется в этот момент синхросигнал СТО, который поступает на вход формирователя 4 серии импульсов и на все узлы 13. Формирователь 4 серий импульсов не воспринимает сигнал СТО, так как находится в исходн ом состоянии и блокирован низким уровнем сигнала Упр. серии. Узлы 13 по переднему

0

фронту сигнала СТО формируют входные воздействия на контролируемый логический блок (позиции 129 и 130). Если первый разряд регистра 71 в нуле, то йосле позиции 129 алгоритма устройство переходит к вьтолнению очередного.такта контроля - чтению следующего слова из блока памяти (позиция 123). После выполнения позиции 130 алгоритма, если второй разряд регистра 71 в нуле (не разрешено формирование синхросигнала ЗП РЕЗ), устройство также переходит к вьшолне- 5 ниш очередного такта контроля (позиция 130), а если второй разряд регистра 71 в единице и отсутствует сигнал Упр. серии, то по переднему фронту сто происходит установка триггера 75 в единичное (состояние позиция 133), формируются сигналы ЗП и -ЗЙ, запрещается работа распределителя 66 импульсов и ПРОИСХОДИТ

запуск формирователя 76 временного 5 интервала. Через время, определяемое кодом задержки в регистре 1.16 (позиция 134), на выходе формирователя 76 временного интервала появляется сигнал ЗП РЕЗ, который поступает на входы 30 узлов 13 и записьшает результат контроля в триггеры 102, одновременно сигнал ЗП РЕЗ увеличивает на единицу содержимое счетчика 8 тестовых наборов (позиция 135). Если хотя бы в одном из узлов , триггер 102 устанавливается в единичное состояние5 то на выходной шине 36 появляется низкий уровень сигнала - Брак контакта (фиг. 8), который через многовходовый элемент И 15 поступает на вход блока 5 управления и блока 9 индикации (фиг. I). Устрой- ство вьшолняет действия в соответствии с позициями 149-15 алгоритма, р. Если узел 13 контролирует входной контакт блока 16,. то- в этом случае на шине 35 устанавливается дополнительно низкий уровень сигнала - Брак входи, конт., который через элемент И 4 по шине 38 поступает на блок 5 управления и блок 9 индикации, после чего устройство выполняет действия в соответствии с позициями 152- 157 алгоритма (см. фиг. 15) и происходит останов работы устройства. Элементы 63 J 86-89 и 10.9 индикации обеспечивают оператору полную информацию о причинах останова (характер брака на входе или выходе блока 16, номер

0

5

0

0

5

2313

забракованного контакта, номер тестового набора, на котором обнаружен брак). Если при выполнении позиции 152 сигнал - Брак входн, конт, на шин.е 38 отсутствует (имеется высоки уровень), то устройство анализирует режим работы, заданный переключателями 51, 52 или 54, и в случае работы устройства в режиме До брака про- исходит вьшолнение позиций 158, 154- 157 алгоритма, останов работы устройства в момент обнаружения брака на выходном контакте контролируемого блока 16.

Таким образом, при обнаружении брака на входе блока 16 устройство прекращает работу тотчас же независимо от режима работы, а при забракованном выходном контакте блока 16,, устройство останавливается в момент обнаружения брака лишь в режиме До брака. Если после вьшолнения пози- дай 135 и 149 алгоритма, сигнал - Брак низкого уровня не появляется, то устройство переходит к очередному такту контроля (позиции 149, 159, 123) либо, если установлен режим контроля Шаг (включен переключатель 52), происходит вьтолнение по- зиций 159, 154-157 алгоритма и устройство останавливается после контроля блока 16 на данном тестовом наборе.

Работа устройства в случае вьшо- да из блока 2 памяти любого из командных слов СИ1 - СИ4 аналогична работе устройства при выводе командного слова Задержка, отличие состоит в том, что информация команд- ных слов СИ1 - СИ4 записьшается в соответствующие счетчики 43-46 (позиции 139,140) и при этом устанавливается сигнал Упр. серии высокого уровня на шине 21.

В дальнейшем, при вьшоде из блока 2 памяти после командных слов СИ1 - СИ4 первого информационного слова, адресованного п-му контакту контролируемого блока 16,причем в 12-м разряде слова должна быть единица, происходит выдача на п-й контакт блока 16 серии импульсных сигналов. Число импульсов в серии определяется 16-разрядным двоичным числом, записанным в счетчи- ки 43-46, а полярность их - логичес- КИМ уровнем в восьмом разряде информационного слова, адресующего п-й контакт. Если в восьмом разряде ин5

1

Q 5

0 5 О

Q 5

g

0724

формациоиного слова (ЗУ08) присутствует логический нуль, то этот уровень поступает на элемент 10 сложения по модулю два (фиг. 1), который работает как повторитель сигнала Серия, поступающего по шине 22 (формируется серия импульсов положительной полярности), Если в восьмом разряде информационного слова присутствует логическая единица, то элемент 10 сложения по модулю- два работает как инвертор сигнала Серия (формируется на шину 32 серия импульсов отрицательной полярности). Работа устройства Во время формирования серии импульсов отражена позициями 123-126, 128-131, 136 и 137 алгоритма (фиг,12 и 13). При формировании серии импульсов запрещено формирование сигнала СИ СЧ (позиция 127 алгоритма про-г. пускается), счетчик 1 адреса имеет одно и то же значение, следовательно, на выходных шинах блока 2 памяти находится информация одного и того же слова данных (серия импульсов идет на один контакт). Постепенно по мере формирования серии импульсов содержимое формирователя 4 уменьшается, а когда оно становится равным нулю (позиция 136), сигнал Упр. серии снимается и в следующем такте работы устройство (позиции 123-127) переходит к выводу следующего слова данных из блока 2 памяти. Если это слово данных представляет собой командное слово Конец теста, то устройство выполняет действия в соответствии с позициями 123, 124, 138, 139, 141, 144-146, 154-156 алгоритма и происходит останов устройства по концу тестовой программы с соответствующей индикацией. Из алгоритма устройства следует, что если режим работы не задан, то останов устройства происходит по окончании тестовой программы.

Если установлен режим работы Цикл, то по окончании тестовой программы в такте работы с командным словом Конец теста устройство после позиции 146 вьшолняет действия позиций 147 и 148 алгоритма, счетчики 1 адреса и 8 наборов сбрасываются в нулевое состояние и устройство начинает повторный прогон тестовой программы.

Возможна установка комбинирован- ного режима работы устройства: До

25 . 1327107

брака и Цикл (включены переключа- формирователь серии импульсов, элетели 51 и 54).

При этом программа контроля логического блока вьтолняется устройством многократно в режиме Цикл до момента обнаружения неисправности. Этот . режим работы устройства удобен при проведении различного рода испытаний логических блоков (климатических, механических и т.д.), а также при проведении термотренировки блоков в / .рабочем состоянии.

Таким образом, предлагаемое устройство для контроля функционирования логических блоков позволяет контролировать логические узлы с любыми сочетаниями логических уровней ТТЛ и ЭСЛ, обеспечивает контроль многоразрядных счетчиков и регистров за счет подачи нормированных серий импульсов на заданные входы, обеспечивает контроль функционирования логических блоков 5 содержащих сложные

мент сложения по модулю два, переключатель, п программируемых узлов соглаf сования, где п - число контактов : контролируемого блока, причем выходы блока памяти соединены с информационными входами д€ шифратора команд, с первой группой информационных входов

10 программируемого формирователя серии импульсов, информационными входами блока синхронизации, первым входом элемента сложения по модулю два, информационными входами дешифратора

15 контактов и с группами информационных входов с первого по п-й- программируемых узлов согласования 5 группа вьгходов дешифратора команд соединена с второй группой информационных вхо20 дов программируемого формирователя, серии импульсов 5 первый выход дешифратора команд соединен с первьм информационным входом блока индикации

и с входом конца теста блока управле-, перепрограммируемые БИС, за счет воз- 25 кия, второй выход дешифратора команд можности формирования тестовых воз- .соединен с входом задержки блока действий в соответствии с временными синхронизации, первый выход програм- диаграммами .сигналов БИС,.обеспечива- мируемого формирователя серии импуль- ет возможность программного изменения сов соединен с разрешающим входом направления передачи информации между зо блока синхронизации, второй выход устройством и объектом контроля на программируемого формирователя серии

импульсов соединен с вторым входом элемента сложения по .модулю два, выход .которого соединен с информацион- ,, ньми входами с первого по п-й программируемых узлов согласования, второй выход блока управления соединен с входами сброса блока синхронизации, программируемого формирователя серии 40 импульсов, блока индикации и с первого по п-й программируемых узлов со- 1 ласования, третий выход блока управления соединен с входом пуска блока синхронизации и синхровходом блока

45

каждом тестовом наборе, а также возможность циклическ.ого мнох оразового повторения прогр;1ммы контроля и шаговый контроля, позволяет контролировать задержки распростра.нения сигналов в логических блоках.

Формула изобретения

1. Устройство для контроля функционирования лоп-гческих блоков, содержащее счетчик адреса, блок памяти, блок управления, генератор импульсов, два элемента И, дешифратор команд, дешифратор контактов, блок индикации, блок синхроиизации, счетчик тестовых наборов, причем выходы счетчика адреса соединены с адресными .входами блока памяти, первый выход блока управления соединен с входами сброса счетчика адреса и счетчика тестовых наборов, счетный вход счетчика адреса соединен с первым выходом блока синхронизации, отличающееся тем, что, с целью расширения области применения за счет расширения класса контролируемых блоков, устройство содержит программируемый

50

индикации, выход генератора импульсов соединен с тактовым входом блока синхронизации , второй выход которого соединен с входами синхронизации дешифратора команд и дешифратора контактов, третий выход блока синхронизации соединен с входом синхронизации программируемого формирователя серии импульсов и с тервыми входами синхронизации с первого по п-й про- сц граммируемых узлов согласования, четвертый выход блока синхронизации соединен с входом синхронизации блока управления, счетным входом счетчика тестовых наборов и с вторыми

мент сложения по модулю два, переключатель, п программируемых узлов согласования, где п - число контактов : контролируемого блока, причем выходы блока памяти соединены с информационными входами д€ шифратора команд, с первой группой информационных входов

программируемого формирователя серии импульсов, информационными входами блока синхронизации, первым входом элемента сложения по модулю два, информационными входами дешифратора

контактов и с группами информационных входов с первого по п-й- программируемых узлов согласования 5 группа вьгходов дешифратора команд соединена с второй группой информационных входов программируемого формирователя, серии импульсов 5 первый выход дешифратора команд соединен с первьм информационным входом блока индикации

индикации, выход генератора импульсов соединен с тактовым входом блока синхронизации , второй выход которого соединен с входами синхронизации дешифратора команд и дешифратора контактов, третий выход блока синхронизации соединен с входом синхронизации программируемого формирователя серии импульсов и с тервыми входами синхронизации с первого по п-й про- граммируемых узлов согласования, четвертый выход блока синхронизации соединен с входом синхронизации блока управления, счетным входом счетчика тестовых наборов и с вторыми

входами синхронизации с первого по п-программируемых узлов согласования , группа выходов счетчика тестовых наборов соединена с группой информационных входов блока индикации, входы записи с первого по п-й про- граммируемых узлов согласования соединены с соответствующими с первого по п выходами дешифратора контактов, информационные входы-выходы с первого по п-й программируемых узлов согласования являются информационными входами-выходами устройства для подключения к контактам контролируемого блока, выходы Врак входного контакта с первого по п-й программируемых узлов согласования соединены с входами первого элемента И, выход которого соединен с первым входом Брак блока управления и вторым информационным входом блока индикации, выходы Брак контакта с первого по п-й программируемых узлов согласования соединены с входами второго элемента И, выход которого соединен с вторым входом Брак блока управления и третьим информационным входом блока индикации, входы уровня потенциала с первого по п-й программируемых узлов согласования через переключатель подключены к шинам нулевого и единичного потенциалов устройства.

2, Устройство по п. 1, о т л и - ч ающееся тем, что блок управ- ления содержит две кнопки, три переключателя ,четыре элемента И-НЕ, три элемента НЕ, два элемента И, D-триг- гер и элемент индикации, причем выход первой кнопки соединен с синхровхо- дом D-триггера, прямой выход которого является третьим выходом блока, а инверсный выход D-триггера соединен с входом элемента индикации, первый : вход первого элемента И является пер- вым входом Брак блока, выход первого элемента И соединен с входом установки в О D-триггера, информационный вход и вход установки в 1 которого соединены с шиной единичного потенциала, второй вход Брак блока через первый элемент НЕ соединен с первым входом первого.элемента И-НЕ, второй вход которого соединен с выходом первого переключателя, а выход первого элемента-И-НЕ соединен с вторым входом первого элемента И, вход синхронизации блока соединен с первым входом второго элемента И-НЕ, второй

вход которого соединен с выходом второго переключателя, выход второго элемента И-НЕ соединен с третьим входом первого элемента И, вход конца теста блока управления через второй элемент НЕ соединен с первыми входам третьего и четвертого элементов И-НЕ выход третьего элемента И-НЕ соедине с четвертым входом первого элемента И, выход третьего переключателя соединен с вторым входом третьего элемента И-НЕ и через третий элемент НЕ - с вторым входом четвертого элемента И-НЕ, выход которого соединен с первым входом второго элемента И, выход которого является первым выходом блока, выход второй кнопки соединен с пятым входом первого элемента И, вторым входом второго элемента И и является вторым выходом блока.

3. Устройство по п. 1, о т л и - чающееся тем, что блок синхронизации содержит два элемента И-НЕ пять элементов И, элемент НЕ, D-триг- гер, регистр, распределитель импульсов, формирователь временных интервалов , причем первый выход формирователя временных интервалов соединен с инверсным входом первого элемента И и является четвертым выходом блока, второй выход формирователя временных интервалов соединен с тактовым входом распределителя -«чпульсов, первый выход которого соединен с входом синхронизации регистра, первым входом .второго элемента И является вторым выходом блока, выход второго элемента И является первым выходом блока, шесть разрядов из группы информационных входов блока, тактовый вход и вход задержки блока соединены с первого по восьмой входами формирователя временных интервалов, вход сброса блока соединен с девятым входом формирователя временных интервалов, с первым входом первого элемента И и входом сброса распределителя импульсов, второй выход которого соединен с первым входом третьего элемента И, выход которого соединен с входом синхронизации D-триггера и является третьим выходом блока, вход пуска блока соединен с первым входом первого элемента , второй вход которого соединен с инверсным выходом D- триггера, выход первого элемента И-НЕ соединен с входом пуска распределителя импульсов, пятый, и шестой разря2913271073°

ды из группы информациорлНых входов ляются первой группой информационных блока соединены с первьми входами со- входов формирователя, управляющие ответственно четвертого и пятого элементов И, выходы которых соединены

входы параллельной записи четырех счетчиков являются второй группой информационных входов формирователя. 5. Устройство по п. 1,0 тли - чающееся тем, что i-й программируемый узел согласования содер

соответственно с информационными входами первого и второго разрядов регистра, выход цервого разряда регистра соединен с.вторьи входом третьего элемента И, выход второго разряда регистра соединен с информационнш . входом D-триггера., седьмой разряд из информационных входов блока соединен через элемент НЕ с вторыми входами четвертого и пятого элементов И и с первым входом второго зле- мента И-НЕ, второй вход которого является разрешающим вхо.г ом блока, выход второго элемента И-НЕ соеди- не с вторьм входом первого элемента И и вторым входом BTOpoi o элемента К. выход первого элемента И соедкнен с 1 ходом сброса D-триггера, прямой выход которого соединен с .десятьяч

входом формирователя временных интер-- 25 зуют группу информационных выходов

валов.

4. Устройство по п, 5 о т .гг и - ч а io щ е е с я тем,, что, программируемый .формирова ель серии импульсов содгрлсит счетный триггер, четы- ре счетчика, элемент И-НЕ, элемент ИЛИ, причем информационные выходы с перв-ого по Четвертый счетчиков соеди )1ены с группой входов элемента ИЛИ, вход которого соединен с прямь выхо д,о:-5 счетного трих-гера, выход которо г о является Бторьих выходом формирователя. зь;ход элеме :1та ИЛИ соединен с первым входом элемента И-НЕ, н явля- ет2л первым выходом форь;ипователя, выход заема первого сче счикэ. соедине с синх1 овходом. обратного счета второго счетчика.; выход заема второг О счетчика - с сикхровходом обратного счета третьего счетчика; выход заема которого соединен с ср нхровходом обратного счета четвертого счетчика, илверсньй выход счетного триггера соединен с синхровходом обратного счета первого счетчика, входы сброса в 1юль. четырех счетчиков и счетного Tpiirrepa соединены с входом сброса |1)ормирователя J вход С -1пхронизацик форьгирователя соединен с вторым входом элемента И-ИЕ., выход которого соед(-гнсн со счетнь1М входом счетного rpifrrepa . одмоимеиные информационные входь параллельной записи четырех счетчиков соединены между собой и являются первой группой информационных входов формирователя, управляющие

входы параллельной записи четырех счетчиков являются второй группой информационных входов формирователя. 5. Устройство по п. 1,0 тли - чающееся тем, что i-й программируемый узел согласования содер0 лсит четырехразрядный регистр, двух- разрядный регистр, элемент НЕ, два элемента И-НЕ, преобразователь уровней ТТЛ-ЭСЛ, преобразователь уровней ЭСЛ-ТТЛ, В-триггер, два согласующих

5 резистора, вьшрямительный диод, реле, элемент индикации, формирователь уровней ТТЛ с тремя состояниями по выходу, элемент сложения по модулю два, элемент И, причем информационньш

0 вход первого разряда четырехразрядного регистра является информационным входом узла,, информационные входы второго, третьего и четвертого разрядов четырехразрядного регистра обраузла, синхровход параллельной записи четырехразрядного регистра является входом записи узла, синхровход па.рал лелльной записи двухразрядного триг30 герного регистра является первья г входом синхронизации узла, а первый и второй информационнь е входы разрядов двухразрядного регистра соединены соответственно с выходами первого и

эд второго разрядов четырехразрядного регистра, выход четвертого разряда которого через элемент НЕ соединен с входом обмотки реле, выход обмотки реле соединен с шиной электропитания

40 ТТЛ, выход третьего разряда четырехразрядного регистра соединен с пер- вьм входом элемента И, второй вход которого соединен с выходом элемента сложения по модулю два, вьгход эле45 мента И соединен с информационным входом D-триггера, вход синхронизации которого является вторьи входом синхронизацииэ а вход сброса является входом сброса узла, инверсный вы50 ход D-триггера соединен с входом элемента индикации и является выходом Брак контакта узла, прямой выход Б-триггера соединен h первым входом первого элемента И-НЕ, второй вход

55 которого соединен с первым входом второго элемента И-НЕ и выходом второго разряда двухразрядного регистра выход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ

31 .13

и является выходом Брак входного контакта узла, выход второго элемента И-НЕ соединен с входом установки третьего состояния формирователя уровней ТТЛ, информационный вход которого соединен с выходом первого разряда двухразрядного регистра не первым входом элемента сложения по модулю два, второй вход которого соединен с выходом преобразователя уровней ЭСЛ-ТТЛ, вход которого соединен с выходом преобразователя ТТЛ-ЭСЛ

32

и с нормально раэомкнутьтм контактом реле и через первый согласующий резистор соединен с шиной электропитания ЭСЛ, вход преобразователя ТТЛ-ЭСЛ соединен с выходом формирователя уровней ТТЛ, с нормально замкнутым контактом реле и с катодом выпрямительного диода, анод которого через второй согласующий резистор соединен с входом уровня потенциала узла, пе- . реключающий контакт реле соединен с информационным входом-выходом узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля функционирования логических блоков | 1988 |

|

SU1599860A2 |

| Устройство для контроля и диагностики логических блоков | 1985 |

|

SU1302284A1 |

| Устройство для контроля цифровых систем | 1983 |

|

SU1130871A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для контроля логических схем | 1986 |

|

SU1381517A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU947863A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для тестового контроля логических узлов | 1991 |

|

SU1837297A1 |

| Устройство для тестового диагностирования цифровых блоков | 1987 |

|

SU1622884A1 |

Изобретение относится к вычислительной цифровой технике и может быть использовано для контроля функционирования логических блоков ЭВМ. Целью изобретения является расширение области применения за счет расширения класса контролируемых -блоков, (Л

г

J7

,Л/ набора

87

„Годен

„Врак

„брак gff Входа

;, Тест окончен

90

Фиг. 6

ЦЗигЛ

Эталон %. ,3tf W

1 Jr7

A.

95}ПИТ .-,

Ъ

т Л

. l gclOS

,Spffл контакта 36

фи.9

,Такт

,токт (шина 80)

О

.УПР I

(шина л)

О

Codepixt/ i

мое cvem-T

чика 111

О и

.ТАКТ 1 1шинад01

vaw-

nvc t,ve/7f- 1/{//еа lie д.

.J/7- (шина 79}

О

. (шит X)

у«

120

( Начало j

J21

г- и

Устоно6итб ре}ним (онтроля

г-/

Начать KHonf u55Ui f9{X6PgCuf ..ЛУСЮ

Г--Ш1327107

120

Начало

J21

и

/

Г--ШФормиробание

сигнала „ЗАГР1/ЗМ

25Р- „/ 5Запись S регистр 77 и В регистр 941 вб/- тдного з.ла /J

-гА- Ь чпО-J-

opfiupoScff i/e сигнала. C/ Lfcxod- we состояние/xfc- пределителя 66

03и г. П

.

розряо oeftffm - розряо ftsfiffm -71 В единиJ4e

Нормирование ciiHxpoci/eHom.CTQ , SosdfucnjSue на&локЮ

нет

Ш

Ус/пано6ка трцгге- fXf 75Sj lзапрет работы pacftpede- flumejffp 66

-1 из одержимого формирователя 1 тменен1 ло/ /зно- сти cusHO/KjJ EPHfi

.7J4.

Временной интервал, (popfft//x/e b/u дю/у иробатеаенЪ

135Я орми юВан1/е, сигнала,, 1 6 cvemw/fS /пес- тодыл Hoffo S

Фиг. 13

ш

7J7

Запись нулей 6 регистр 7/сиеш- лом ЗАГРУЗМ

Запись мода заде РЖ/f и 6регистр

т

./4J

Формирование сигнала „С (16c4emwKl адреса

Нет

-

Нет

УстаноВнаВ.. /

триггера 84,бклю

чение индикатора 90

JECr ОКОНЧЕН

CSpac C( 1и8ёнульс1/гнв- лон СБРОС С

1UB

fPopMupoeof/ue сиёнала.СИ,исход- ное состояние рас- npeдeлumeл R 66

-J

723

Ч/

Сброс триггера 61, Sb/мюцение инди- ко/лора „Л(/С/(

1551

Запрет paSo/ru/f блока 7 низким уровнем сигнала

,ПУСН

J5BHHduffouua wfte- ра HaSopa индикаторов 8S

.

f Конец j

Фиг. fS

Составитель. Д. Ванюхин Редактор Л. Веселовская Техред А.Кравчук Корректор Е. Рошко

Заказ 3605Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,-Раушская наб.,-д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство тестового контроля | 1982 |

|

SU1075265A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-02-05—Подача