Изобретение относится к области автоматики и вычислительной техники и предназначено для преобразования кодов.

Известен дешифратор для распознавания команд с последовательной посылкой частотных импульсов, содержащий усилитель мощности, соединенный с частотными избирателями, детекторными преобразователями, схемами совпадения, элементами памяти, задержки п «НЕ.

Предложенное устройство отличается тем, что выхОхТ, каждой схемы совпадения первой грунны соединен с входом соответствующей схемы совналТ.ения второй группы, выход которой связаи с входом соответствующего элемента памяти, выход элемента памяти через элемент «НЕ - с входами остальных схем совпадения второй группы, а выход элемента задержки - с входами дополнительных элементов задержки и «НЕ, выходы которых связаны с входами дополнительной схемы совпадения, выход последней подключен к входу дополнительного элемента памяти, выход этого элемента намятн - к входу дополнительной собирательной схемы, второй вход которой связан с выходом донолнительного элемента задержки, выходы схем совпадения первой группы элементов памяти, дополнительного элемента памяти соединены с входами всех схем совпадения второй группы.

Это позволяет повысить нахдежность, помехоустойчивость и расширить область применения устройства.

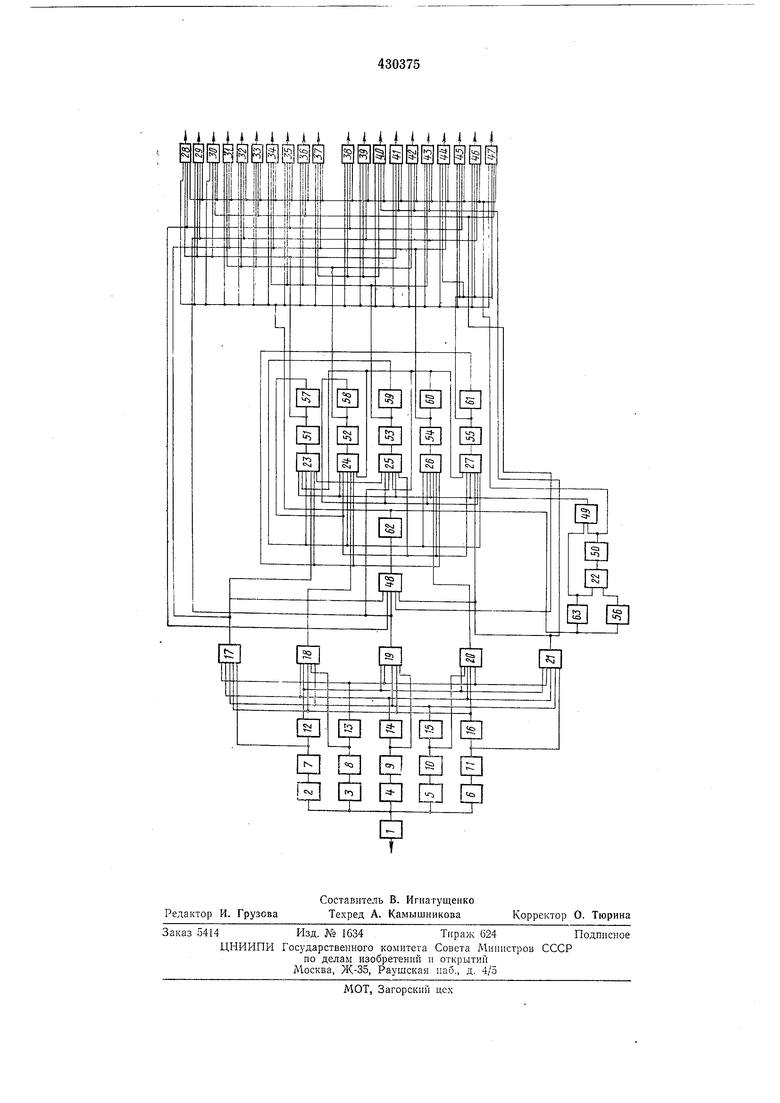

На чертеже показапа схема описываемого

устройства.

Устройство содержит усилитель 1 мощности, частотные избиратели 2-6, детекторные преобразователи 7-11, элементы «НЕ 12-16, схемы 17-21, 22, 23-27, 28-47 совпадения;

собирательиые схемы 48 и 49, элементы 50-55 памяти; элементы «НЕ 56-61; элементы 62 и 63 задерлски;

Прн поступлении первого импульса сигнала на схему 17 совнадения, он одновременно

через элемент «НЕ 12 осуществляет «запрет, воздействуя на схемы 18-21. Сигнал «единица с выхода схемы 17 подается па собирательную схему 48 и выходные схемы 31, 34, 37 и 44.

С выхода элемента 62 задержки сигиал проход.ит на дополнительную схему 63 задержки и элемент «НЕ 56, а далее па донолпительную схему 22 совпадения, дополнительный элемент 50 памяти и дополнительную собирательную схему 49, с которой сигнал поступает па все входы собирательных схем второй группы 23-27. С выхода элемепта 50 памяти сигпал поступает на все входы выходных схем 28-47 совпадения.

Одновременно на выходе схемы 23 совпадения появляется сигнал «единица, который через элемент 51 памяти попадает на выходные схемы совпадения.

Прохождение импульса аналогично.

Предмет изобретения

Дешифратор, содержащий усилитель мощности, выход которого соединен с входами частотных избирателей, выход каждого из которых через соответствующий детекторный преобразователь соединен с входом соответствующей схемы совпадения первой группы схем совпадений и через элемент «НЕ с входами остальных схем совпадений той же группы, выходы всех схем совпадений первой группы соединены с входами собирательной схемы, выход последней соединен с входом элемента задержки, выход которого соединен с входами всех выходных схем совпадения, вторую группу схем совпадения, элементы памяти, «НЕ, дополнительные элементы «НЕ, памяти, задержки, схему совпадения, собирательную схему, отличающийся тем, что, с целью повышения надежности, помехоустойчивости и расширения области нрименения, выход каждой схемы совпадения первой группы соединен с входом соответствующей схемы совпадения

второй группы, выход которой соединен с входом соответствующего элемента памяти, выход последнего через элемент «НЕ соединен с входами остальных схем совпадения второй группы, выход элемента задержки соединен с

входами дополнительных элементов задержки и «НЕ, выходы которых соединены с входами дополнительной схемы совпадения, выход последней соединен с входом дополнительного элемента памяти, выход которого соединен с

входом дополнительной собирательной схемы, второй вход которой соединен с выходом дополнительного элемента задержки, выходы схем совпадения первой группы, элементов памяти, дополнительного элемента памяти соединены с входами соответствующих выходных схем совпадения, а выход дополнительной собнрательной схемы соединен с входами всех схем совпадения второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор | 1975 |

|

SU584308A2 |

| Устройство для приема команд телеуправления | 1977 |

|

SU623225A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU317082A1 |

| ПЕРЁСЧЕТНОЕ УСТРОЙСТВО | 1971 |

|

SU308536A1 |

| Дискретный частотный фильтр | 1980 |

|

SU999138A1 |

| УСТРОЙСТВО ОХРАННОЙ СИГНАЛИЗАЦИИ | 1991 |

|

RU2031445C1 |

| УСТРОЙСТВО ДЛЯ ИССЛЕДОВАНИЯ НАДЕЖНОСТИ ФУНКЦИОНИРОВАНИЯ СИСТЕМ | 1969 |

|

SU255657A1 |

| АДАПТИВНОЕ ТЕЛЕИЗМЕРИТЕЛЬНОЕ УСТРОЙСТВО | 1970 |

|

SU419946A1 |

| СЛЕДЯЩИЙ ИНТЕГРАТОР | 1970 |

|

SU285356A1 |

| Система передачи дискретной информации | 1987 |

|

SU1506566A2 |

Даты

1974-05-30—Публикация

1972-02-07—Подача