Изобретение относится к радиотехнике. Удвоитель частоты найдет применение в синтезаторах частот, радиоприемных устройствах и др.

В перечисленных устройствах возникает необходимость в умножении частоты заполнения ко.рот1ких ради1аиМ|Пульсных €Иг.нало1В, причем частота заполнения может изменяться в широких пределах (например, в синтезаторах частот максимально возможная частота относится к минимальной частоте заполнения как 1 : 2 или 1:3).

В известном удвоителе частоты, содержащем преобразователь входного сигнала, выходы которого через интеграторы подключены к сумматору, входной сигнал преобразуется в два противофазных прямоугольных сигнала, которые в интеграторах превращаются в треугольные импульсы. В ограничителях эти импульсы ограничиваются, в результате чего на их выходах длительность имиульсов зависит от частоты входного сигнала. Сигнал, прошедший через логический сумматор, воздействует па блок формирователя выходного сигнала, который создает колебания с удвоенной частотой. Пороговое устройство и управляющий элемент автоматически устанавливают пороги ограничения в ограничителях.

Из-за наличия пепи отрипательной обратной связи это устройство обладает большим

временем установления и не может умножать несущую частоту коротких радиоимпульсов.

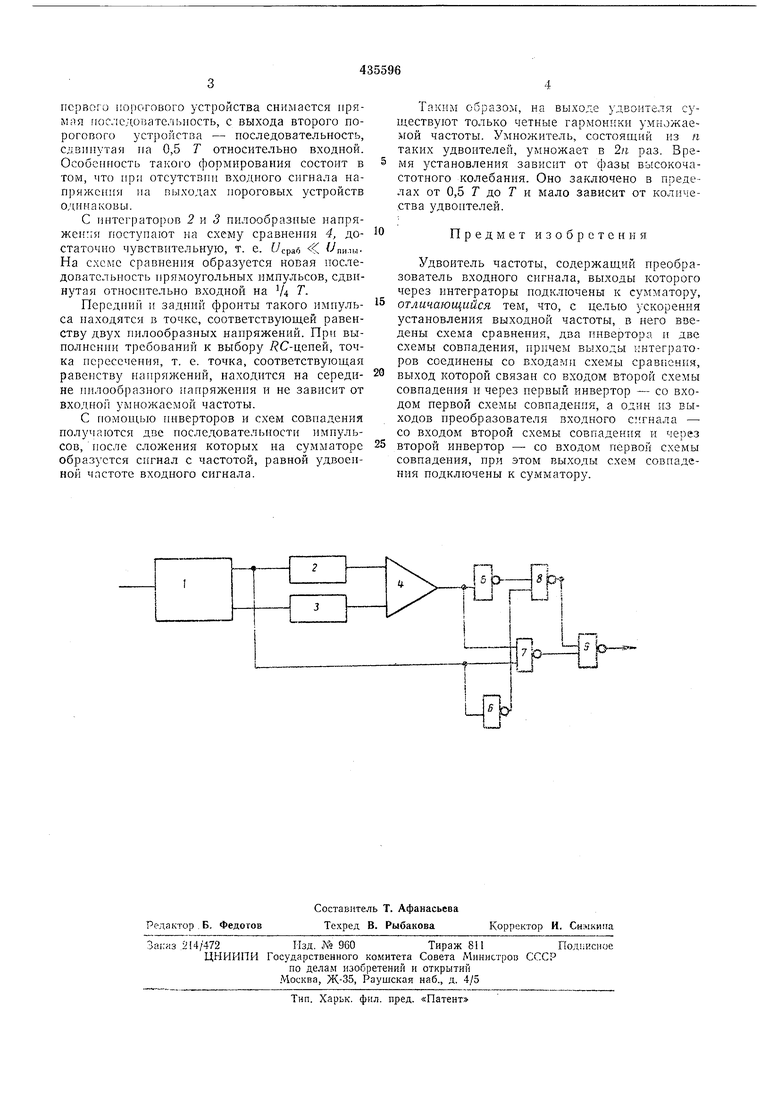

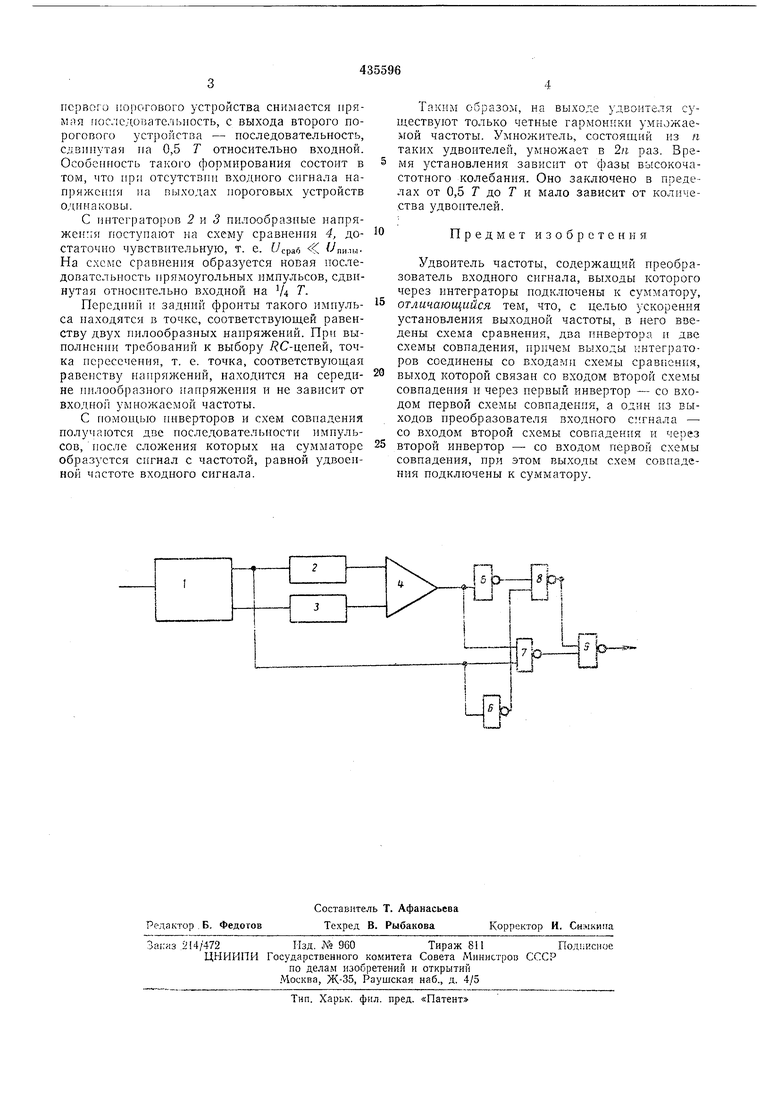

Цель изобретения - ускорение установления выходной частоты - достигается тем, что в предлагаемый удвоитель частоты введепы схема сравнения, два инвертора и две схемы совпадения, причем выходы инверторов соединены со входами схемы сравнения, выход которой связан со входом второй схемы совпадения и через первый пнвертор - со входом первой схемы совпадения, а один из выходов гфеобразователя входного сигнала - со входом второй схемы совпадения и через второй инвертор - со (ВХОДОМ первой схемы совпаде:М|ИЯ. Выходы схем совпадения лодключелы к сумматору.

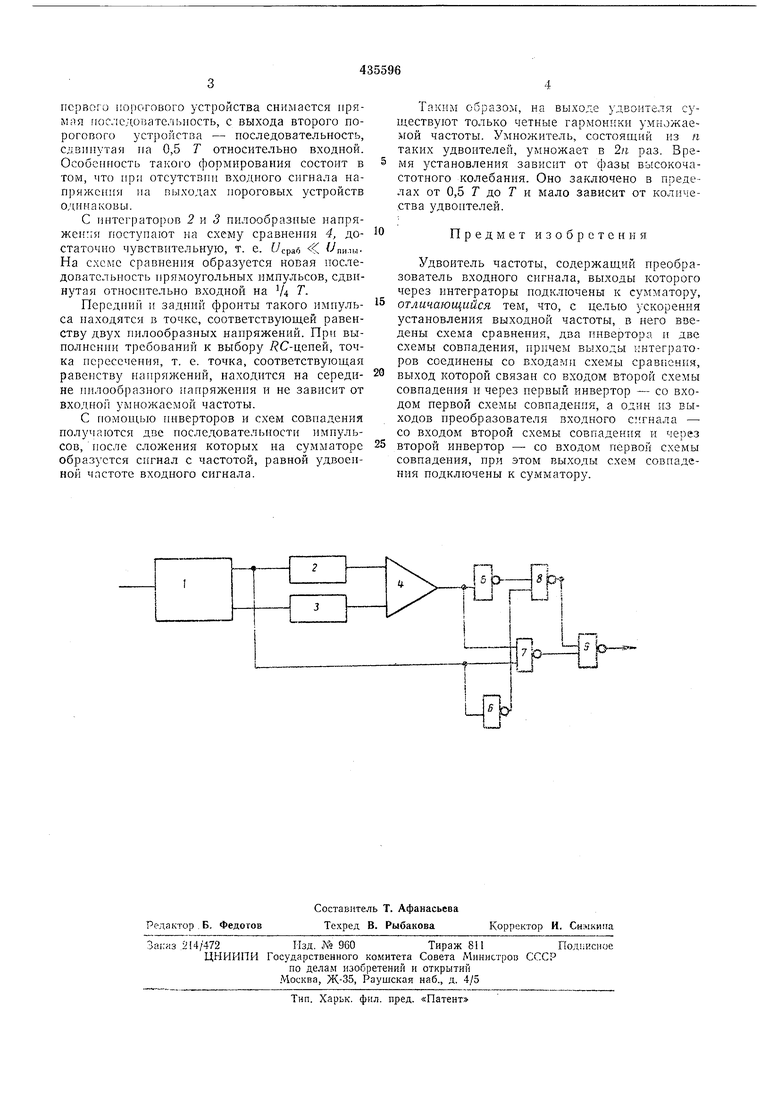

Блок-схема устройства приведена на чертеже.

Удвоитель частоты содержит преобразователь входного сигнала 1, интеграторы 2 и 3, схему сравненпя 4, ипверторы 5 и 6, схемы совпадения 7 п 8, сумматор 9.

Преобразователь входного сигнала / содержит усилительпый каскад с импульснЫ М трансформатором п два каскада пороговых устройств. Две последовательности прямоугольных импульсов, снимаемые с обмоток трансформатора с заземленной средней точкой, подаются на пороговые устройства. С выхода

первого noporvOBoro устройства снимается прямая ггослсдотзателыюсть, с выхода второго порогового устройства - последовательность, сдвппутая па 0,5 Т относительно входной. Особеппость такого формирования состоит в том, что при отсутствпп входного сигнала напряжения иа выходах пороговых устройств о,.

С пнтеграторов 2 и 3 пилообразные напряжения поступают на схему сравнения 4, достаточно чувствительную, т. е. f/cpao С пилы.

На схеме сравнения образуется новая последовательность прямоугольных импульсов, сдвинутая относительно входной на /4 Т.

Передний и задний фронты такого имиульса находятся в точке, соответствующей равенству двух пилообразных напряжений. При выполнении требований к выбору / С-цепей, точка пересечения, т. е. точка, соответствующая равенству напряжений, находится на середине гп лообразного напряжения и не зависит от входно умножаемой частоты.

С помощью пнверторов и схем совпадения получаются две последовательности импульсов, после сложения которых на сумматоре образуется ситнал с частотой, равной удвоенной частоте входного сигнала.

Таким образо.%1, на выходе удвоителя существуют только четные гармоники умножаемой частоты. Умножитель, состоящий из п таких удвоителей, умножает в 2/ раз. Время установления зависит от фазы высокочастотного колебания. Оно заключено в пределах от 0,5 Г до 7 и мало зависит от количе.ства удвоителей.

Предмет изобретения

Удвоитель частоты, содержащий преобразователь входного сигнала, выходы которого через интеграторы подключены к сумматору, отличающийся тем, что, с целью ускорения установления выходной частоты, в него введены схема сравнения, два инвертора и две схемы совпадения, причем выходы интеграторов соединены со входами схемы срав 1ения, выход которой связан со входом второй схемы совпадения и через первый инвертор - со входом первой схемы совпадения, а один из выходов преобразователя входного сигнала - со входом второй схемы совпадения и через второй инвертор - со входом первой схемы совпадения, при этом выходы схем совпадения подключены к сумматору.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для интерполяции сигналов измерительных преобразователей | 1977 |

|

SU752139A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОД-НАПРЯЖЕНИЕ | 2014 |

|

RU2559722C1 |

| ЦЕЗИЕВЫЙ СТАНДАРТ ЧАСТОТЫ | 1994 |

|

RU2076411C1 |

| ДВУХФАЗНЫЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ СИГНАЛОВ | 1990 |

|

RU2033684C1 |

| Устройство для передачи сигнала с частотной манипуляцией | 1985 |

|

SU1256235A1 |

| Устройство для определения параметров симметричных импульсов | 1982 |

|

SU1078345A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ | 2008 |

|

RU2361358C1 |

| ПАРАМЕТРИЧЕСКИЙ СИНТЕЗАТОР | 1970 |

|

SU265218A1 |

| Преобразователь напряжение-код | 1984 |

|

SU1197082A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА - НАПРЯЖЕНИЕ | 2014 |

|

RU2565472C1 |

5 |Э- L.J

Даты

1974-07-05—Публикация

1972-11-24—Подача