1

Изобретение относнтся к измерению линейных и угловых размеров и может использоваться, например, в линейных и круговых измерительных преобразователях перемещения рабочих органов стаиков с ЧПУ, а также коордппатпо-пзмерительных машипах.

Известно устройство для интерполяции, построенное ио компенсационной схеме, содержащее измерительный преобразователь перемещений, компенсационный преобразователь, фазовые детекторы, коммутатор, усилитель, двигатель, цифровой датчик угла 1.

Недостатком данного устройства является узкий частотный диапазон преобразования.

Наиболее близким техническим рещеппем к изобретению является устройство для интерполяцпп спгиалов измерительных преобразователей, содержащее двухфазный измерительный преобразователь перемещения, два блока выделения модуля спгналов, подключенные к нему параллельно, сумматор, подключенный к выхОлТ,ам блоков выделения модуля сигналов, преобразователь амплитуда - постоянное напряжение, соединенный входами с входами и выходами блоков выделения модуля сигналов, блок цифровой кнтикации 2.

Недоетатками такого устройства является необходимость наличия большого числа компараторов для обеспечения необходимой точности, сложность оперативного нзмене5 ння коэффнциента иитерноляцип.

Целью пзобретеппя является повышение точностн н разрешающей способности.

Цель достигается тем, что устройство еиабжено последовательно соединенными

10 генератором нмпульсов счета, делителем частоты, амплитудно-импульсным модулятором, ннтегратором, тремя компараторами, первый из которых подключен входами к выходам сумматора и интегратора, второй

15 и третий - к соответствующим выходам двухфазного нзмернтельного преобразователя, инвертором, подключенным к выходу первого компаратора, тремя формирователями импульсов, первый из которых под20 ключеп к выходу первого компаратора, второй - к выходу пнвертора, третшТ - к выходу делителя частоты, двумя двухвходовыми логическими элемептами И, первые входы которых подключены к выходам первых

25 двух формирователей импульсов соответственно логическим элементом ИЛИ, иодключенным к выходам первых двух логических элементов И, триггером, первый вход которого подключен к выходу логического эле30 мента ИЛИ, а второй - к выходу третьего

формирователя импульсов, блоком неравнозначности, соединенным двумя входами с выходами второго и третьего компараторов, а выходом - со вторыми входами первого и второго логических элементов PI, делителем частоты с переменным коэффициентом деления, третьим логическим элементом И, соедннеииым входами с выходом триггера и выходом делителя частоты с переменным коэффициентом деления, счетчиком импульсов, подключенным входом к выходу делителя частоты с переменным коэффициентом деления, а выходом - к блоку цифровой индикации.

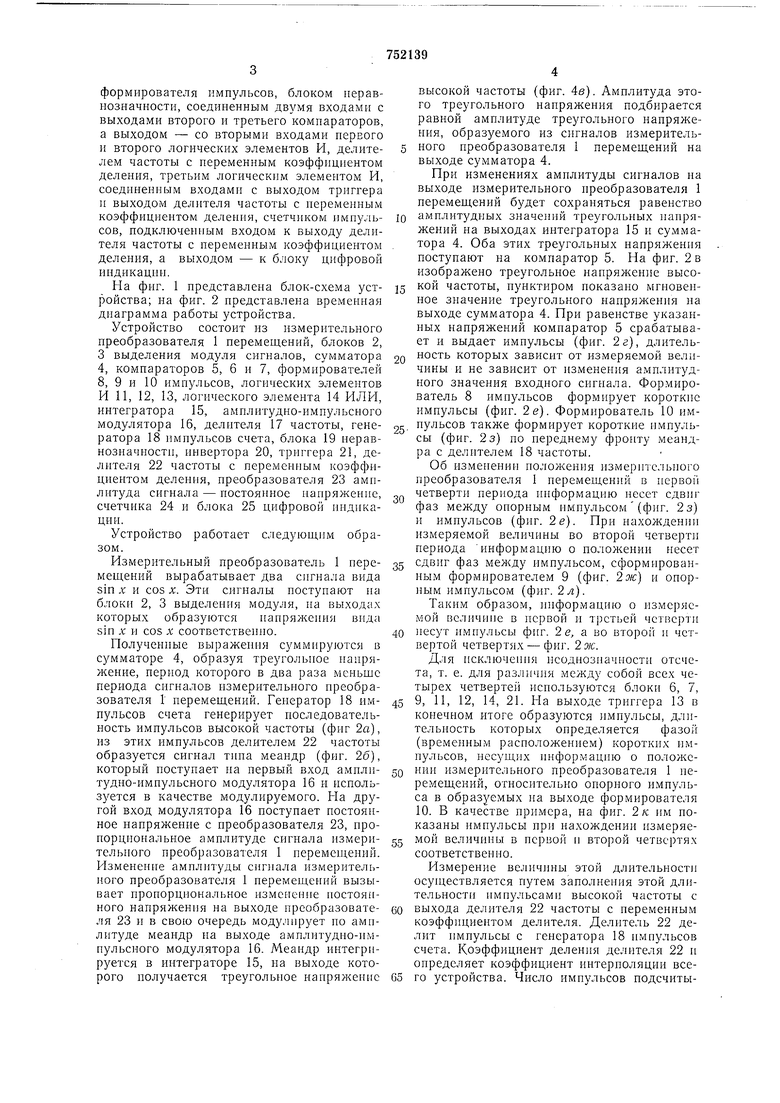

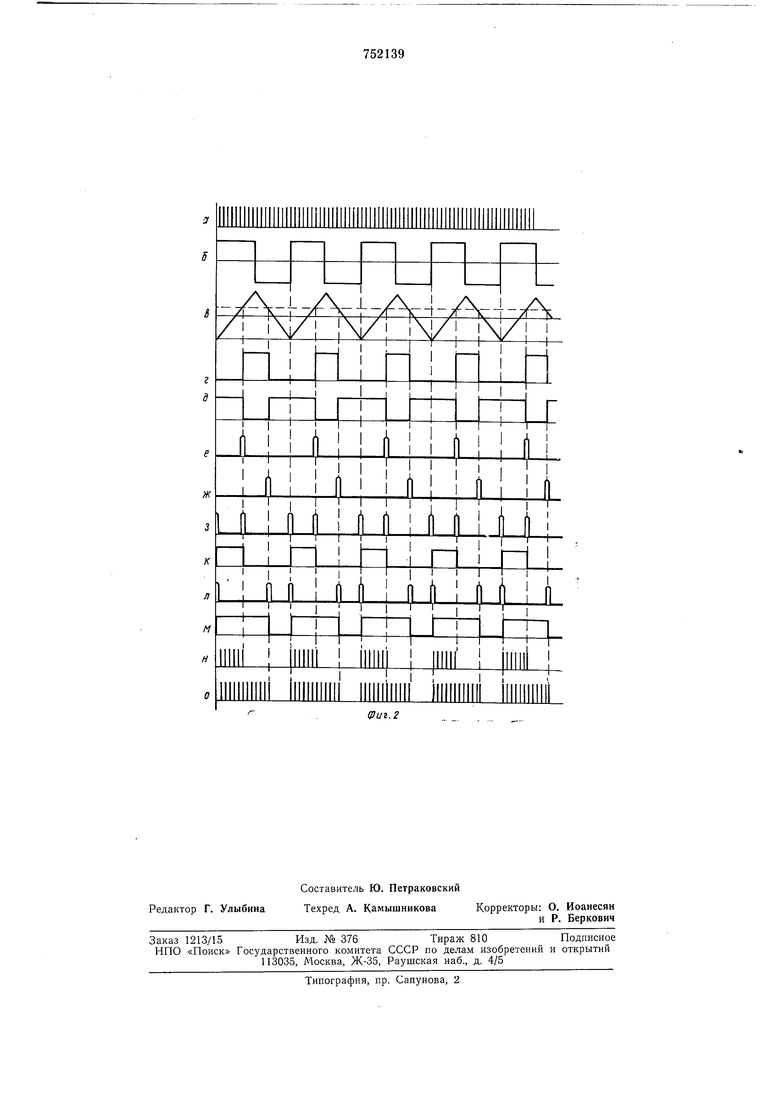

На фиг. 1 представлена блок-схема устройства; на фиг. 2 представлена временная диаграмма работы устройства.

Устройство состоит нз измерительного преобразователя 1 неремещений, блоков 2, 3 выделения модуля сигналов, сумматора 4, компараторов 5, 6 н 7, формирователей 8, 9 и 10 импульсов, логических элементов И 11, 12, 13, логического элемента 14 ИЛИ, интегратора 15, амплитудно-импульсного модулятора 16, делнтеля 17 частоты, генератора 18 импульсов счета, блока 19 неравнозначности, инвертора 20, триггера 21, делителя 22 частоты с переменным коэффициентом деления, нреобразователя 23 амилнтуда сигнала - постоянное напряжение, счетчика 24 и блока 25 цифровой индикации.

Устройство работает следующим образом.

Измерительный преобразователь 1 перемещений вырабатывает два сигнала вида sin X и cos X. Эти сигналы поступают па блоки 2, 3 выделеиня модуля, иа выходах которых образуются иапряжепия вида sin X и cos X соответствепно.

Полученные выраже1И1я суммируются в сумматоре 4, образуя треугольное иаиряжение, период которого в два раза меньше периода сигналов измерительиого иреобразователя 1 иеремещений. Геиератор 18 импульсов счета генерирует последовательность импульсов высокой частоты (фиг 2а), из этих импульсов делителем 22 частоты образуется сигнал типа меандр (фиг. 26), который иостуиает на первый вход амплитудно-импульсного модулятора 16 н использзется в качестве модулируемого. На другой вход модулятора 16 поступает постоянное напряжение с преобразователя 23, иропорциональное амплитуде сигнала нзмерительного преобразователя 1 перемещений. Изменение амплитуды сигнала измерительного преобразователя 1 неремещений вызывает пропорциональное изменение постоянного напряжения на выходе преобразователя 23 и в свою очередь модулирует по амплитуде меандр иа выходе амплптудио-нмиульсного модулятора 16. Меаидр интегрируется в интеграторе 15, на выходе которого получается треугольное напряжение

высокой частоты (фиг. 40). Амплитуда этого треугольного напряжения подбирается равной амплитуде треугольного напряжения, образуемого из сигналов измерительного иреобразователя 1 перемещений на выходе сумматора 4.

При изменениях амплитуды сигналов на выходе измерительного нреобразователя 1 перемещеннй будет сохраняться равенство

амплитудных значений треугольных напряжений иа выходах интегратора 15 и сумматора 4. Оба этих треугольных напряження поступают на компаратор 5. На фиг. 2 в изображено треугольное наиряжение высокой частоты, пунктиром ноказано мгновенное значение треугольного напряження на выходе сумматора 4. Прн равенстве указанных напряженнй компаратор 5 срабатывает и выдает импульсы (фиг. 2 г), длительность которых зависит от измеряемой величины и не зависит от изменения амплитудного значения входного сигнала. Формирователь 8 имиульсов формирует короткие импульсы (фиг. 2е). Формирователь 10 импульсов также формирует короткие импульсы (фиг. 2 з) по иереднему фронту меандра с делнтелем 18 частоты.

Об измеиении иоложения измерительиого преобразователя 1 перемещеннй в иервой четверти периода ииформацию несет сдвиг фаз между оиорным нмпульсом (фиг. 2з) и импульсов (фиг. 2е). При нахождении измеряемой величины во второй четверти периода информацию о положении несет

сдвиг фаз между импульсом, сформироваипым формирователем 9 (фиг. 2 ж) и опорным импульсом (фиг. 2л).

Таким образом, ииформацию о измеряемой величине в иервой и третьей четверти

иесут импульсы фиг. 2 е, а во BTOpoii и четвертой четвертях - фиг. 2 ж.

Для исключения пеоднозиачности отсчета, т. е. для различия Д1ежду собой всех четырех четвертей иснользуются блокн 6, 7,

9, И, 12, 14, 21. На выходе триггера 13 в конечном итоге образуются импульсы, длительпость которых определяется фазой (временным расположением) коротких импульсов, несущих информацию о иоложеНИИ измерительного преобразователя 1 перемещений, относительно опорного импульса в образуемых на выходе формирователя 10. В качестве нримера, на фиг. 2 к им ноказаны имиульсы нри нахождении измеряемой величииы в нсрвой и второй четвертях соответственио.

Измерение величины этой длительности осуществляется путем заполнения этой длительности импульсами высокой частоты с

выхода делителя 22 частоты с переменным коэффициентом делителя. Делитель 22 делит импульсы с геиератора 18 импульсов счета. Коэффициент деления делителя 22 и определяет коэффициент интерполяции всего устройства. Число имиульсов подечитыБается счетчиком 24 и индицируется в цифровом виде в блоке 25. Таким образом осуществляется внутришаговое деление иериода входного сигнала.

Формула изобретения

Устройство для интериоляции сигналов измерительных иреобразователен, содержащее двухфазный измерительный иреобразователь иеремещения, два блока выделения модуля сигналов, иодключенные к нему параллельно, сумматор, нодключенный к выходам блоков выделения модуля сигналов, преобразователь амилитуда-иостояиное наиряжение, соединенный входами с входами и выходами блоков выделения модуля сигналов, блок цифровой индикации, о тличающееся тем, что, с целью иовышения точности и разрешающей сиособиости, оно снабжено последовательно соединенными генератором имиульсов счета, делителем частоты, амплитудно-имиульсным модулятором, интегратором, тремя комиараторами, первый из которых подключен входами к выходам сумматора и интегратора, второй и третий - к соответствующим выходам двухфазного измерительпого преобразователя, инвертором, подключенным к выходу первого компаратора, тремя формирователями импульсов, первый из которых иодключен к выходу первого компаратора,

второй - к выходу инвертора, третий - к выходу делителя частоты, двумя двухвходовыми логическими элементами И, первые входы которых подключены к выходам первых двух формирователей импульсов соответственно,, логнческим элементом ИЛИ, подключенным к выходам первых двух логических элементов И, триггером, первый вход которого подключен к выходу логического элемента ИЛИ, а второй - к выходу третьего формирователя нмпульсов, блоком неравнозначности, соединенным двумя входами с выходами второго и третьего компараторов, а выходом - со вторыми входами

иервого и второго логических элементов И, делителем частоты с неременным коэффнциентом деления, третьим логическим элементом И, соедппенным входамн с выходом триггера и выходом делителя частоты с переменным коэффициентом деления, счетчиком импульсов, подключенным входом к выходу делителя частоты с переменным коэффициентом делення, а выходом - к блоку цифровой индикации.

Источники ииформацин,

пр П1Ятые во внимание ири эксиертизе

1.Зверев А. Е., Максимов В. П., Мясников В. А. Иреобразователи угловых перемещений в цифровой код. Л., «Энергия,

1974, с. 76.

2.Патент ФРГ Л 194520G, кл. 42D 5/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ БИНАРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2567002C1 |

| КВАЗИКОГЕРЕНТНЫЙ МОДУЛЯТОР СИГНАЛОВ КВАДРАТУРНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ | 2014 |

|

RU2581646C1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Устройство для формирования импульсов сложной формы | 1982 |

|

SU1075388A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧАСТОТА - НАПРЯЖЕНИЕ | 2014 |

|

RU2565472C1 |

| Растровый интерполятор | 1978 |

|

SU769492A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ МНОГОФАЗНОГО ПЕРИОДИЧЕСКОГО СИГНАЛА | 1991 |

|

RU2017063C1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| Анализатор спектра вибраций | 1975 |

|

SU546827A1 |

| МНОГОКАНАЛЬНОЕ АКУСТИКО-ЭМИССИОННОЕ УСТРОЙСТВО | 2020 |

|

RU2736171C1 |

/ г I 7 14 7

/-

I

I I

i И

п

I I

о р И о

I

м

--1

I г

Авторы

Даты

1980-07-30—Публикация

1977-06-06—Подача