1

Изобретение относится к технике радиосвязи и может использоваться в системах передачи информации час- тотно-манипулированными сигналами с непрерывной фазой.

Цель изобретения - уменьшение ур овня внеполосного излучения.

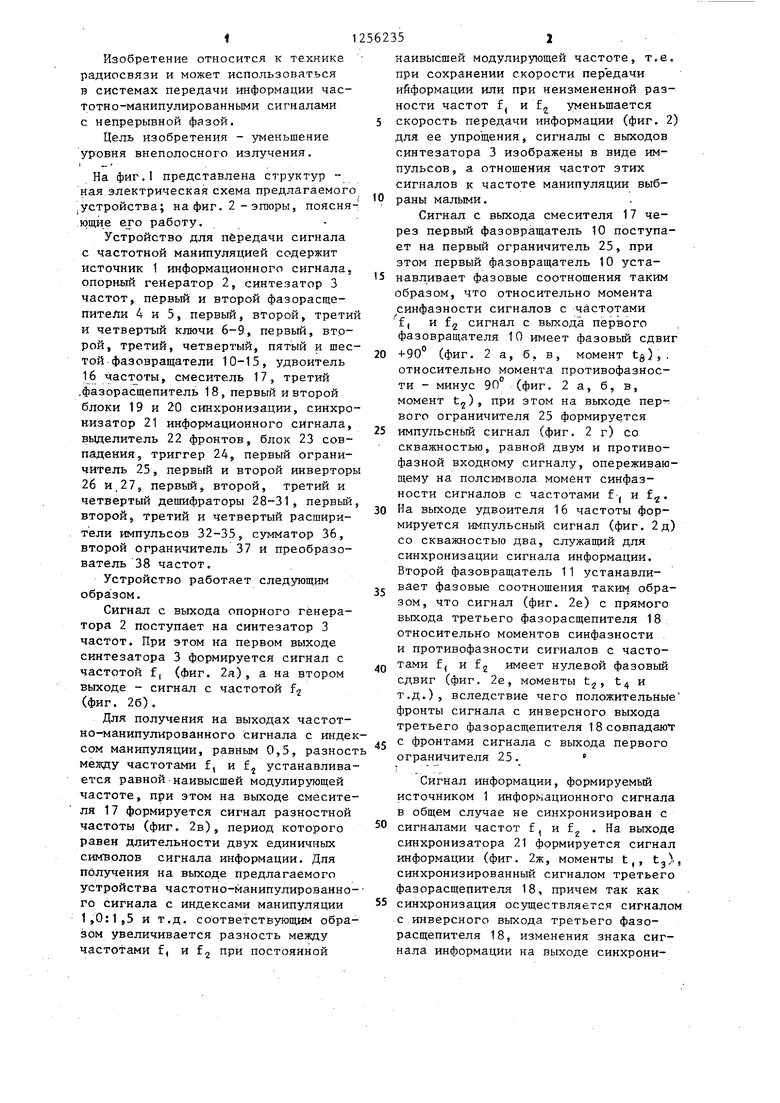

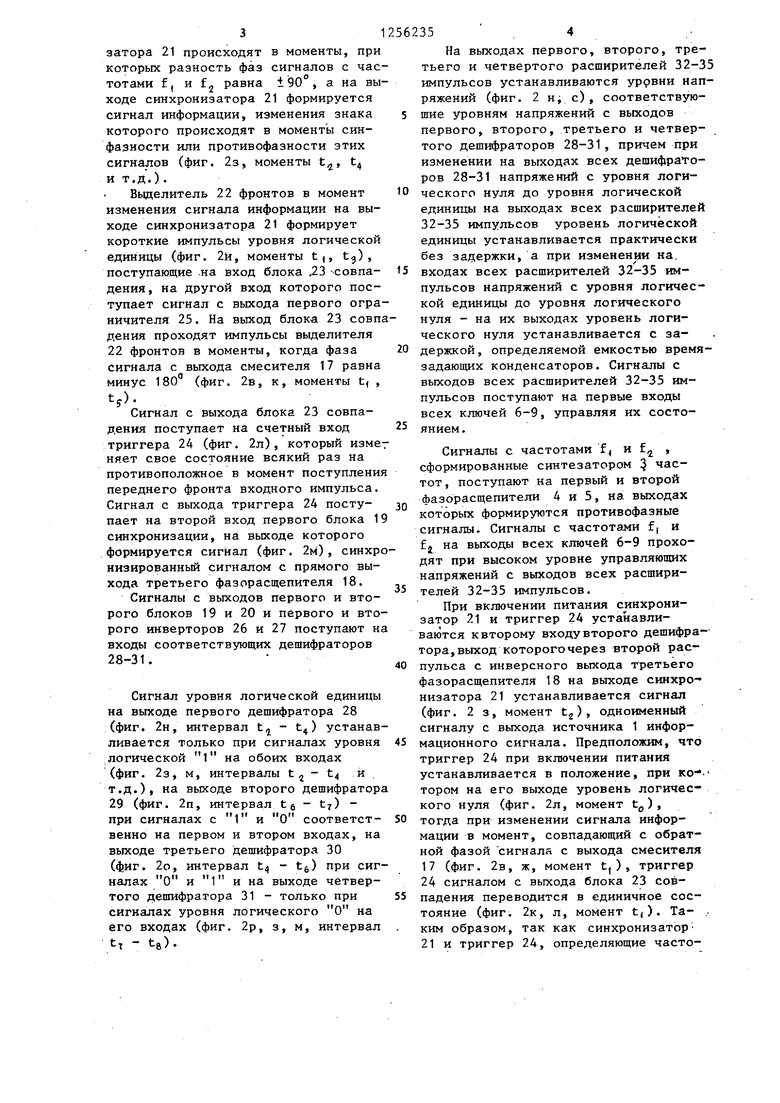

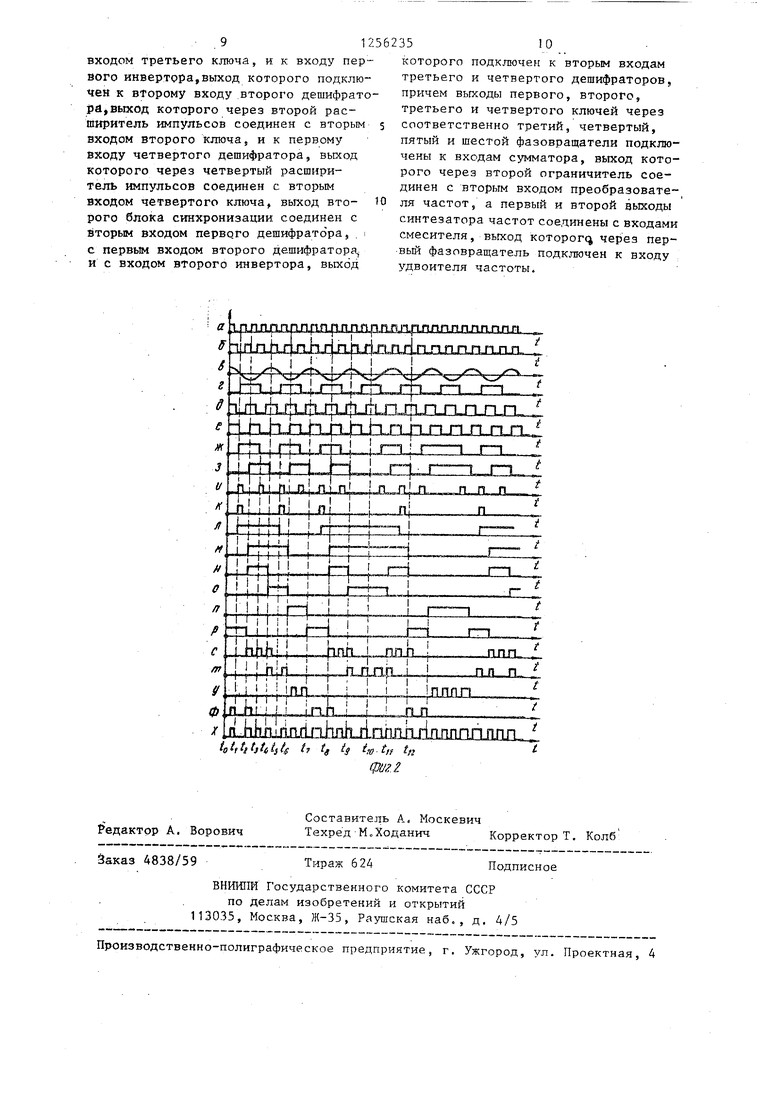

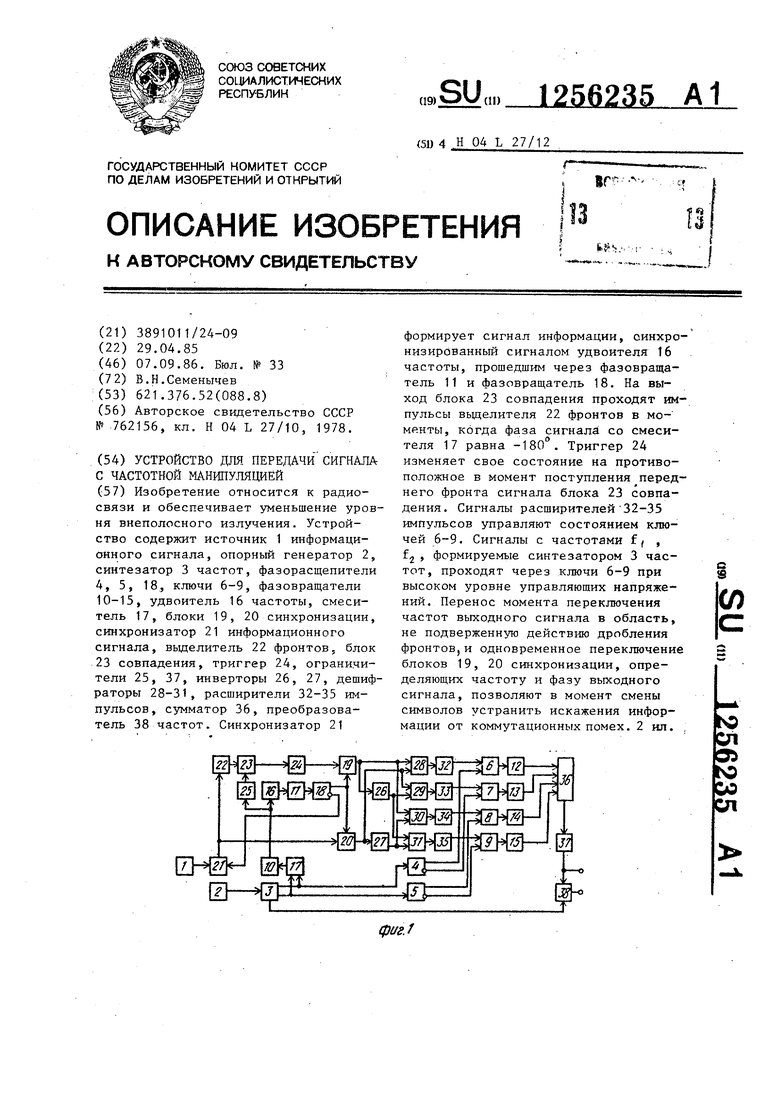

На фиг.1 представлена структур - ная электрическая схема предлагаемого устройства; на фиг. 2 - эпюры, поясняющие ejo работу.Устройство для передачи сигнала с частотной манипуляцией содержит источник 1 информационного сигнала, опорный генератор 2, синтезатор 3 частот, первый и второй фазорасще- пители 4 и 5, первый, второй, третий и четверэъгй ключи 6-9, первый, вто рой, третий, четвертый, пятый и шестой фазовращатели 10-15, удвоитель 16 , смеситель 17, третий .фазорасщепитель 1 8, первый и второй блоки 19 и 20 синхронизации, синхронизатор 21 информационного сигнала, выделитель 22 фронтов, блок 23 совпадения, триггер 24, первый ограничитель 25, первый и второй инверторы 26 и.27, первый, второй, третий и четвертый дешифраторы 28-31, первый, второй, третий и четвертый расширители импульсов 32-35, сумматор 36, второй ограничитель 37 и преобразователь 38 частот.

Устройство работает следующим образом.

Сигнал с выхода опорного генератора 2 поступает на синтезатор 3 частот. При этом на первом выходе синтезатора 3 формируется сигнал с частотой f| (фиг. 2а), а на втором выходе - сигнал с частотой fj (фиг. 26),

Для получения на выходах частот- но-манипулированного сигнала с индексом манипуляции, равным 0,5, разность между частотами f, и f устанавливается равнойнаивысшей модулирующей частоте, при этом на выходе смесите- ля 17 формируется сигнал разностной частоты (фиг. 2в), период которого равен длительности двух единичных символов сигнала информации. Для получения на выходе предлагаемого устройства частотно-манипулированно- го сигнала с индексами манипуляции 1,0:1,5 и т.д. соответствующим образом увеличивается разность между частотами f, и f, при постоянной

:

62352 . наивысшей модулирующей частоте, т.е. при сохранении скорости передачи ибформации или при неизмененной разности частот f, и fj уменьшается 5 скорость передачи информации (фиг. 2) для ее упрощения, сигналы с выходов синтезатора 3 изображены в виде импульсов, а отношения частот этих сигналов к частоте манипуляции выбраны малыми.

Сигнал с выхода смесителя 17 через первый фазовращатель 10 поступает на первый ограничитель 25, при этом первый фазовращатель 10 устанавливает фазовые соотношения таким образом, что относительно момента синфазности сигналов с частотами

10

15

f, И 2 сигнал с выхода первого фазовращателя 10 имеет фазовый сдвиг

20 +90 (фиг. 2 а, б, в, момент

te) .

относительно момента противофазнос- ти - минус 90 (фиг, 2 а, б, в, момент t) , при этом на выходе пер- вого ограничителя 25 формируется импульсньгй сигнал (фиг. 2 г) со скважностью, равной двум и противофазной входному сигналу, опереживаю- щему на полсимвола момент синфазности сигналов с частотами f- и f . На выходе удвоителя 16 частоты формируется импульсный сигнал (фиг. 2д) со скважностью два, служаш 1й для синхронизации сигнала информации. Второй фазовращатель 11 устанавливает фазовые соотношения таким образом, что сигнал (фиг. 2е) с прямого выхода третьего фазорасщепителя 18 относительно моментов синфазности и противофазности сигналов с частотами f( и fj имеет нулевой фазовый сдвиг (фиг. 2е, моменты t, t и т.д.), вследствие чего положительные фронты сигнала с инверсного выхода третьего фазорасщепителя 1 8 совпадают с фронтами сигнала с выхода первого ограничителя 25.

Сигнал информации, формируемый источником 1 информационного сигнала в общем случае не синхронизирован с сигналами частот f, и f .На выходе синхронизатора 21 формируется сигнал информации (фиг. 2ж, моменты t,, tj), синхронизированный сигналом третьего фазорасщепителя 18, причем так как синхронизация осуществляется сигналом с инверсного выхода третьего фазорасщепителя 18, изменения знака сигнала информации на выходе синхрони31

затора 21 происходят в моменты, при которых разность фаз сигналов с частотами f, и fj равна 190°, а на выходе синхронизатора 21 формируется сигнал информации, изменения знака которого происходят в моменты син- фазности или противофазности этих сигналов (фиг. 2з, моменты t, t и т.д.).

Выделитель 22 фронтов в момент изменения сигнала информации на выходе синхронизатора 21 формирует короткие импульсы уровня логической единицы (фиг. 2и, моменты t(, t), поступающие .на вход блока ,23 -совпадения, на другой вход которого поступает сигнал с выхода первого ограничителя 25. На выход блока 23 совпадения проходят импульсы выделителя 22 фронтон в моменты, когда фаза сигнала с выхода смесителя 17 равна минус 180° (фиг. 2в, к, моменты t, , t,).

Сигнал с выхода блока 23 совпадения поступает на счетный вход триггера 24 (фиг. 2л), который измег няет свое состояние всякий раз на противоположное в момент поступления переднего фронта входного импульса. Сигнал с выхода триггера 24 поступает на второй вход первого блока 19 синхронизации, на выходе которого формируется сигнал (фиг. 2м), синхронизированный сигналом с прямого выхода третьего фазорасщепителя 18.

Сигналы с выходов первого и второго блоков 19 и 20 и первого и второго инверторов 26 и 27 поступают на входы соответствующих дешифраторов 28-31.

Сигнал уровня логической единицы на выходе первого дешифратора 28 (фиг. 2н, интервал tj - t) устанавливается только при сигналах уровня логической 1 на обоих входах (фиг. 2з, м, интервалы t - t и . т.д.), на выходе второго дешифратора 29 (фиг. 2п, интервал te - t) - при сигналах с 1 и О соответственно на первом и втором входах, на выходе третьего дешифратора 30 (фиг. 2о, интервал t - t) при сигналах О и 1 и на выходе четвертого дешифратора 31 - только при сигналах уровня логического О на его входах (фиг. 2р, з, м, интервал tT - te).

56235 . 4

На выходах первого, второго, третьего и четвертого расширителей 32-35 импульсов устанавливаются уррвни напряжений (фиг. 2 к; с), соответствую- 5 шие уровням напряжений с выходов первого, второго, третьего и четвертого дешифраторов 28-31, причем при изменении на выходах всех дешифраторов 28-31 напряжений с уровня логи 0 ческого нуля до уровня логической единицы на выходах всех расширителей 32-35 импульсов уровень логической единицы устанавливается практически без задержки, а при изменении на.

5 входах всех расширителей 32-35 импульсов напряжений с уровня логической единицы до уровня логического нуля - на их выходах уровень логического нуля устанавливается с за20 держкой, определяемой емкостью время- задающих конденсаторов. Сигналы с выходов всех расширителей 32-35 импульсов поступают на первые входы всех ключей 6-9, управляя их состо5

янием.

Сигналы с частотами f и f , сформированные синтезатором частот , поступают на первый и второй фазорасщепители 4 и 5, на выходах которых формируются противофазные сигналы. Сигналы с частотами f, и fJ на выходы всех ключей 6-9 проходят при высоком уровне управляющих напряжений с выходов всех расширителей 32-35 импульсов.

При включении питания синхронизатор 21 и триггер 2А устанавливаются к второму входу второго дешифратора, выход которого через второй распульса с инверсного выхода третьего фазорасщепителя 1В на выходе синхро- низатора 21 устанавливается сигнал (фиг. 2 3, момент tj), одноименный сигналу с выхода источника 1 информационного сигнала. Предположим, что триггер 24 при включении питания устанавливается в положение, при ко-,- тором на его выходе уровень логического нуля (фиг. 2л, момент t,) ,

тогда при изменении сигнала информации в момент, совпадающий с обратной фазой сигнала с выхода смесителя 17 (фиг. 2в, ж, момент t, ), триггер 24 сигналом с выхода блока 23 совпадения переводится в единичное состояние (фиг. 2к, л, момент tj). Та- .. КИМ образом, так как синхронизатор 21 и триггер 24, определяющие частоту и фазу выходного сигнала устройства, з равляются сигналом с инверсного выхода третьего фазорасщепителя 18 они устанавливаются в необходимо состояние из полсимвола до момента переключения частот, что исклк чает влияние внутриаппаратурных задержек вьщелителя 22 фронтов, блока 23 совпадения, триггера 24 и первого ограничителя 25.

Передним фронтом импульса логической единицы с выхода третьего фазорасщепителя 18 первый и второй блоки 19 и 20 синхронизация переводятся в состояние, при котором сигна лы на их выходах одноименны с сигналами, на их входах (фиг.. 2е, э, л,, м.

момент tj).

Таким образом, после поступления первого же импульса уровня логической 1 с выхода третьего фазорасщепителя 18 при указанных исходных состояниях на входах первого дешифратора 28 устанавливаются уровни логической 1, что обуславливает прохождение сигнала с частотой fj и фазой О через первый ключ б (фиг. 2с, т, у, ф, интервал t - t)

При очередном изменении сигнала информации на выходе синхронизатора 21 с высокого уровня на низкий (фиг. 2ж 5 момент t) , в момент пос- тутшения очередного импульса с вько- да третьего фазорасщепителя 18 (фиг. 2 е, момент t) на выходе второго блока 20 синхронизации устанавливается уровень логического нуля (фиг. 2д, интервал t tg), и если при этом длительность предгзщущей посылки равнялась длительности единич- него символа, то состояние триггера 24 и, следовательно, состояние первого блока 19 синхронизации не изменяется. При изменении сигнала на выходе второго блока 20 сикхроииза-, рии с высокого уровня на низкий Первый ключ б закрывается, а третий , ключ 8 открываетсяJ поскольку на пер Ьом и втором входах третьего дешиф- ijaTopa 30 устанавливаются уровни логического О и 1 соответственно При этом на выход третьего ключа 8 проходит сигнал с частотой f и фа- Эой О (фиг. 2и, интервал t tg).

При чередовании символов на вых од синхронизатора 21 (фиг. 2з, интерва tJ- tg) на соответствующем выходе удтройства формируется частотно-ман

15

пулированный сигнал. При этом при указанных исходных состояниях на этот выход поочередно проходит сигнал: f,,0-°(t2 - t4); f,,,0(t4 -.tg); 5 fy, 180° (t, - t); fj, 180 (t, - tg) и вновь f , (tg - tg).

Синхронизатор 21 при этом определяет частоту выходного сигнала, а первый блок 19 синхронизации - фазу iO выходного сигнала; при уровне логической 1 на выходе первого блока

19 синхронизации йа выход устройства

проходят сигналы f, и f с фазой О

(

при уровне логического 180.

О - с фазой

На этом выходе устройства в этом случае формируется частотно-манипу- лированный сигнал без разрыва фазы при любом соотношении длительностей чередующихся символов информации., . Так, например, после окончания символа нуля, длительность которого равна двум единичным символам (фиг. 2з, интервал tg - tj, ) , на выходе, первого дешифратора 28 формируется импульс уровня логической единицы {фиг. 2н5 интервалы t,, - t,., ), которым открывается первый ключ 6, вслед- Ътвие чего на соответствующий выход

устройства вслед за сигналом с частотой f. , О без разрыва фазы проходит сигнал с частотой f,, О (фиг. Zx, момент t(, ) . Третий, четвертый, пятый и шестой фазовращатели 12-15

компенсируют фазовые сдвиги, вноси- мые первым, вторым, третьим и четвертым ключами 6-9.

Неоднозначность состояния тригге- ра 24 при включении питания не ока- зьшает влияния на работоспособность устройства, так как триггер 24 определяет лишь фазу выходного сигнала относительно фазы сигнала той же частоты с выхода синтезатора 3 час- оказывает влияния ни на частоту сигнала, ни на непрерывность фазы выходного сигнала при переключении частот. При сбоях первого и второго блоков 19 и 20 синхрони- зации и синхронизатора 21 устройст-. во самостоятельно корректируется, так как на них непрерывно поступает сигнал тактовой частоты, корректи- .рующий их, работу..

Если длительность импульсов с выходов всех расширителей 32-35 импульсов установлена такой, что импульсы с их выходов по времени час71256235

тично совпадают, то интервалы совпадения на входы сумматора 36 одновременно проходят-сигналы с частос

тами f, и f2. На выходе сумматора 36 формируется сигнал вида

СО,-.

f (t)sinco,t + sincci t 2sin ---t

X sin

032 +CO,

т.е. амплитудно-модулироващ1Ый сигнал с несущей частотой (f (. )/2 Сигнал с выхода сумматора Зб поступает на вход второго ограничителя 3 по амплитуде-, выполняющего, функцию сравнения с нулем, вследствие чего на его выходе в интервалы времени, когда импульсы перекрываются, формируется сигнал со средней частотой равной (f, + f2). Поскольку импульс с выходов расширителей 32-35 импульсов совпадают в моменты синфазности сигналов с частотами f, и fg , то сигнал с частотой (f, + f)/2 также синфазен с сигналами частот f, и f вследствие чего переход сигнала с частотой f, на сигнал с частотой f происходит через сигнал с частотой (f, + 2)72 без разрыва фазы и без коммутационных помех, вызванных в известном устройстве скачкообразным переходом с одной символьной частоты сигнала на другую.

Длительность интервалов, в течен которых формируется сигнал с часто- той (f, + fg)/2, определяется временем совпадения импульсов с выходов всех расширителей 32-35 импульсов. . Для уменьшения искажений частот- но-манипулированного сигнала при формировании его в высокочастотном диапазоне в устройстве сигнал с третьего выхода синтезатора 3 поступает на преобразователь 38 частот на выходе которого формируется сиг- нал в высокочастотном диапазоне.

Перенос момента переключения частот выходного сигнала-в область, не подверженную действию дробления фронтов, одновременное переключение первого и второго блоков 19 и 20 синхронизации, определяющих частоту и фазу, выходного сигнала, позволяет в момент смены символов устранить искажение информации под действием коммутационных помех и повысить .скорость передачи информации.

,8 Формула изобретения

0

5 0 5 о

5 0 5

Устройство для передачи сигнала с частотной манипуляцией, содержащее

последовательно соединенные опорный, генератор и синтезатор частот, пер- вьш, второй и третий выходы которого соединены соответственно с входом первого фазорасщепителя, выходы которого подключены к первым входам первого и второго ключей, с входом второго фазорасщепителя, выходы которого подключены к первым входам третьего и четвертого ключей, и с первым входом преобразователя частот, а также триггер, первый фазовращатель, удвоитель частоты, выход которого подключен к входу второго фазовращателя, и последовательно соединенные источник информационного сигнала и синхронизатор информационного сигнала, отличающее- с я тем, что, с целью уменьшения уровня внеполосного излучения, в него введены два ограничителя, сумматор, третий фазорасщепитель, четыре дешифратора, третий, четвертый, пятый и шестой фазовращатели, два инвертора, четыре расширителя импульсов, смеситель, два блока синхронизации и последовательно соединенные вьвделитель фронтов и блок совпадения, второй вход и выход которого соединены соответственно с выходом первого.ограничителя, к входу которого подключен выход первого фазовращателя, и с входом триггера, выход которого подключен к первому входу первого блока синхронизации, второй вход которого соединен с прямым выходом третьего фазорасщепителя, к входу которого под- ключен . выход второго фазовращателя, и с вторым входом второго блока синхронизации, первый вход которого соединен с входом выделителя фронтов и с выходом синхронизатора информационного сигнала, к второму входу которого подключен инверсный выход третьего фазорасщепителя, при этом выход первого блока синхронизации подключен к первому входу первого дешифратора, выход которого через первый расширитель импульсов соеди- ;нен с вторым входом первого ключа, . к первому входу третьего дешифратора, выход которого через третий расширитель импульсов соединен с вторым

.912

входом третьего ключа, и к входу первого инвертора,выход которого подключен к второму входу второго дешифратора, выход которого через второй расширитель импульсов соединен с вторым входом второго ключа, и к первому входу четвертого дешифратора, вькод которого через четвертый расширитель импульсов соединен с вторым входом четвертого ключа, выход второго блока синхронизации соединен с вторым входом первого дешифрато ра, , с первым входом второго дешифратора и с входом второго инвертора, выход

Редактор А. Ворович

Составитель А. Москевич

Техред МоХоданич Корректор Т, Колб

Заказ 4838/59

Тираж 624

ВНИИГВД Государственного комитета СССР

по Делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3510

которого подключен к вторым входам третьего и четвертого дешифраторов, причем выходы первого, второго, третьего и четвертого ключей через соответственно третий, четвертый, пятый и шестой фазовращатели подключены к входам сумматора, выход которого через второй ограничитель соединен с вторым входом преобразователя частот, а первый и второй выходы синтезатора частот соединены с входами смесителя, выход KOToporq через пер- вьй фазовращатель подключен к входу удвоителя частоты.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный манипулятор | 1985 |

|

SU1277421A1 |

| Преобразователь угла поворота вала в код | 1983 |

|

SU1146803A1 |

| Преобразователь перемещения в код | 1983 |

|

SU1129635A1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

| Частотный манипулятор | 1979 |

|

SU824474A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Частотный манипулятор | 1981 |

|

SU985966A1 |

| Автоматизированная радиолиния | 1987 |

|

SU1443189A1 |

| Система передачи и приема информации с многоосновным кодированием | 1989 |

|

SU1642590A1 |

Изобретение относится к радиосвязи и обеспечивает уменьшение уровня внеполосного излучения. Устройство содержит источник 1 информационного сигнала, опорный генератор 2, синтезатор 3 частот, фазорасщепители 4, 5, 18, ключи 6-9, фазовращатели 10-15, удвоитель 16 частоты, смеситель 17, блоки 19, 20 синхронизации, синхронизатор 21 информационного сигнала, выделитель 22 фронтов, блок 23 совпадения, триггер 24, ограничители 25, 37, инверторы 26, 27, дешифраторы 28-31, расширители 32-35 импульсов, сумматор 36, преобразователь 38 частот. Синхронизатор 21 формирует сигнал информации, синхронизированный сигналом удвоителя 16 частоты, прошедшим через фазовращатель 11 и фазовращатель 18. На выход блока 23 совпадения проходят импульсы выделителя 22 фронтов в мо- менты, когда фаза сигнала со смесителя 17 равна -180 . Триггер 24 изменяет свое состояние на противоположное в момент поступления переднего фронта сигнала блока 23 совпадения. Сигналы расширителей 32-35 импульсов управляют состоянием ключей 6-9. Сигналы с частотами f , fj, формируемые синтезатором 3 частот, проходят через ключи 6-9 при высоком уровне управляюших напряжений. Перенос момента переключения частот выходного сигнала в область, не подверженную действию дробления фронтов, и одновременное переключение блоков 19, 20 синхронизации, определяющих частоту и фазу выходного сигнала, позволяют в момент смены символов устранить искажения информации от коммутационных помех. 2 ил. , (Л

| Авторское свидетельство СССР № 762156, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-09-07—Публикация

1985-04-29—Подача