(54) ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО КАСКАДНОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХРАЗНЕСЕННЫХ И СОСРЕДОТОЧЕННЫХВ ПАКЕТЫ ОШИБОК | 1972 |

|

SU428435A1 |

| Способ кодирования и декодирования блокового кода с использованием алгоритма Витерби | 2015 |

|

RU2608872C1 |

| ВСЕСОЮЗНАЯ I | 1971 |

|

SU304582A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА | 2012 |

|

RU2485683C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

| Дешифратор двоичного циклического кода | 1981 |

|

SU1117848A1 |

1

Изобретение - декодирующее устройство, совмещающее функции корректора ошибок и дешифратора, - может найти применение в системах телеуправления и связи.

Известные дешифраторы-корректоры циклических кодов на КОЛЬЦОВЫХ управляемых регистрах сдвига, позволяющие наряду с дешифрированием исправлять стирания и обнаруживать ошибки, не могут исправлять ошибки.

Известны также дешифраторы-корректоры циклических кодов «а кольцевых упра.вляе1мых регистрах сдвига, позволяющие исправлять ошибки. Однако в таких устройствах с ростом числа исправляемых ошибок линейно растет число управляемых регистров сдвига.

Цель изобретения - оостроение простых дешифраторов-корректоров с исиравлецием ошибок.

Предлагаемое декодирующее устройство каскадного кода, на первой и второй ступенях которого используются циклические коды, как и известные дешифраторы-корректоры, вьтолНено на кольцевых управляемых регистрах сдвига, но в нем для иоцравления ошибок требуется лишь незначительное дополнительное оборудование, которое практически не зависит от числа исправляемых ошибок.

Это достигнуто благодаря тому, что код первой ступени используется для обнаружения ошибок (комбинации кода первой ступени

с обнаруженными ошибками стираются, а код второй ступени используется для исправления этих стираний). Достоинство этого алгоритма декодирования состоит в том, -что дешифраторы на кольцевых управляемых регистрах сдвига, используеМые в качестве декодирующих устройств кода первой и второй ступеней, позволяют без каких-либо дополнительных затрат оборудования обнаруживать ошибки

(на первой ступени декодирования) и исправлять стирания (на второй ступени декодирования) .

В предлагаемом устройстве выходы кольцевого дешифратора первой ступени через двухвходовые схемы «ИЛИ, вторые входы которых связаны с выходом инвертора, соединены с одноименными входа:ми кольцевого дешифратора второй ступени, вход инвертора связан с выходом многовходовой схемы «ИЛИ,

входы которой соединены соответственно с выходами кольце1вого дешифратора первой ступени.

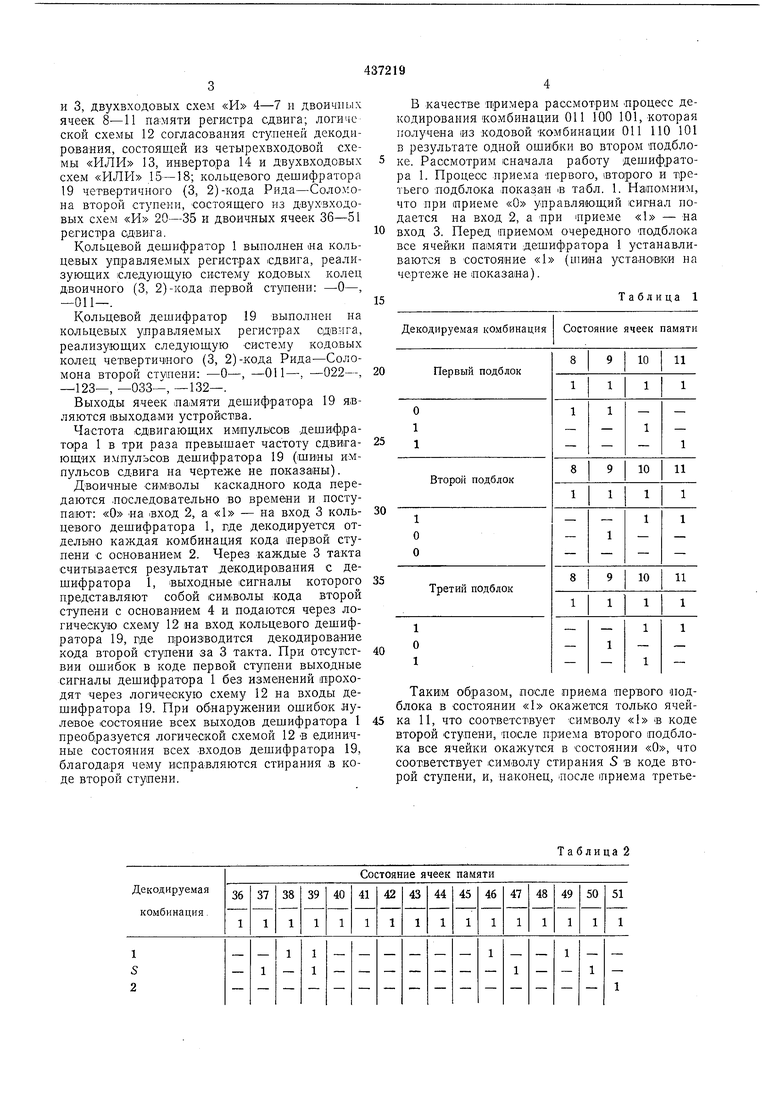

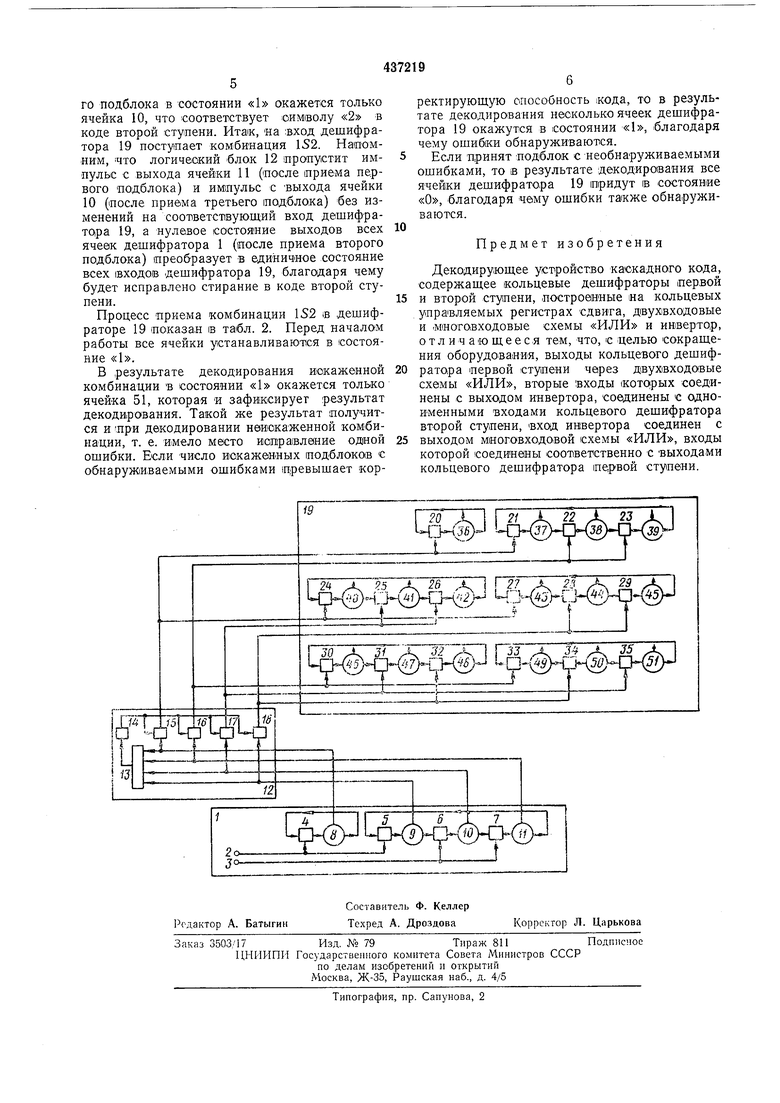

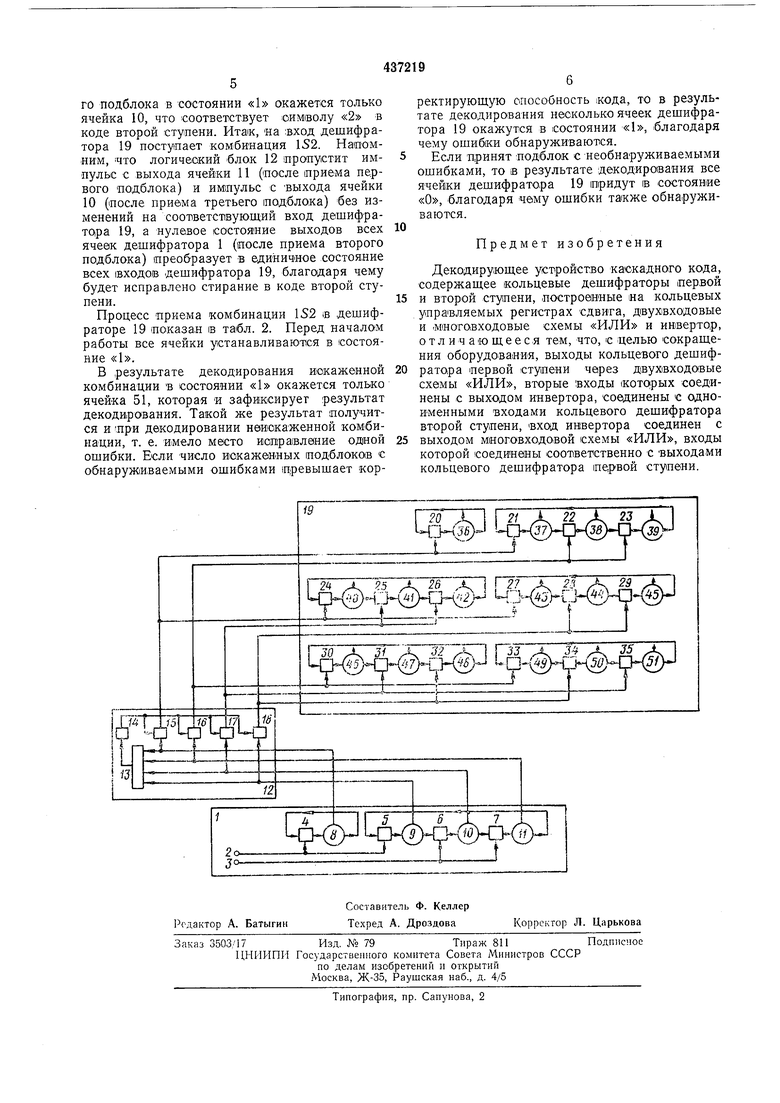

На чертеже представлена схема декодирующего устройства -каскадного (9, 4)-кода с минимальным кодовым расстоянием d-4, исправляющего все одиночные и обнаруживающего все двойные ошибки.

Устройство состоит из кольцевого дешифратора 1 двоичного (3, 2)-кода цервой ступени, состоящего из инфор;мациокных входов 2

и 3, двухвходовых схем «И 4-7 и двоичных ячеек 8-11 регистра сдвига; логичс ской схемы 12 согласования ступеней декодирования, состоящей из четырехвходовой схемы «ИЛИ 13, инвертора 14 и двухвходовых схем «ИЛИ 15-18; кольцевого дешифратора 19 четвертичного (3, 2)-кода Рида-Соломона второй ступени, состоящего из двухзходовых схем «И 20-35 и двоичных ячеек 36-51 регистра сдвига.

Кольцевой дешифратор 1 выполнен «а кольцевых управляемых регистрах 1сдвига, реализующих следующую систему кодовых колец двоичного (3, 2)-кода первой ступени: -О-, -011-.

Кольцевой дешифратор 19 выполнен на кольцевых управляемых регистр:ах сдвига, реализующих следующую систему кодовых колец четвертичного (3, 2) -кода Рида-Соломона второй ступени: -О-, -011-, -022-, -123-, -033-, -132-.

Выходы ячеек памяти дешифратора 19 являются выходами устройства.

Частота сдвигающих импульсов дешифратора 1 в три раза превышает частоту сдвигающих импульсов дешифратора 19 (шины импульсов сдвига на чертеже не показаны).

Двоичные символы каскадного кода передаются последовательно во времени и поступают: «О на вход 2, а «1 - на вход 3 кольцевого дешифратора 1, где декодируется отделыно каждая комбинация кода первой ступени с основанием 2. Через каждые 3 такта считывается результат декодирования с дешифратора 1, выходные сигналы которого представляют собой символы «ода второй ступени с основанием 4 и подаются через логическую схему 12 на вход кольцевого дешифратора 19, оде производится декодирование кода второй ступени за 3 такта. При отсутствии ошибок в коде первой ступени выходные сигналы дешифратора 1 без изменений проходят через логическую схему 12 на входы дешифратора 19. При обнаружении ошибок нулевое состояние всех выходов дешифратора 1 преобразуется логической схемой 12 в единичные состояния всех входов дешифратора 19, благодаря чему исправляются стирания в коде второй ступени.

В качестве примера рассмотрим процесс декодирования комбинации 011 100 101, которая получена из кодовой комбинации 011 ПО 101 в результате одной ошибки во втором подблоке. Рассмотрим сначала работу дешифратора 1. Процесс приема первого, второго и третьего подблока показан в табл. 1. Напомним, что при приеме «О управляющий сигнал подается на вход 2, а при приеме «1 - на вход 3. Перед приемом очередного подблока все ячейки памяти дешифратора 1 устанавливаются в состояние «1 (uiHiHa установки на чертеже не показана).

Таблица 1

Состояние ячеек памяти

Декодируемая комбинация

ТакЕМ образом, после приема первого аюдблока в состоянии «1 окажется только ячейка 11, что соответствует символу «Ь в коде второй ступени, после приема второго подблока все ячейки окажутся в состоянии «О, что соответствует символу стирания S в коде второй ступени, и, наконец, после шриема третьеТаблица 2

Состояние ячеек памяти

Авторы

Даты

1974-07-25—Публикация

1971-03-24—Подача